AMD Vitis Networking P4 工具 ( VNP4 ) 是一種高級設計環境,針對 FPGA 和自適應 SoC 的包處理數據平面,可實現簡化設計的效果。它能夠將用 P4 編寫的設計轉換為設備就緒的 RTL 代碼,以實現最佳的硬件實現。使用 VNP4,您可以顯著減少開發基于設備的數據包處理系統所需的工程工作量,同時仍能實現每 LUT 或每 RAM 的高性能。本白皮書概述了使用 VNP4 進行設計的優點。

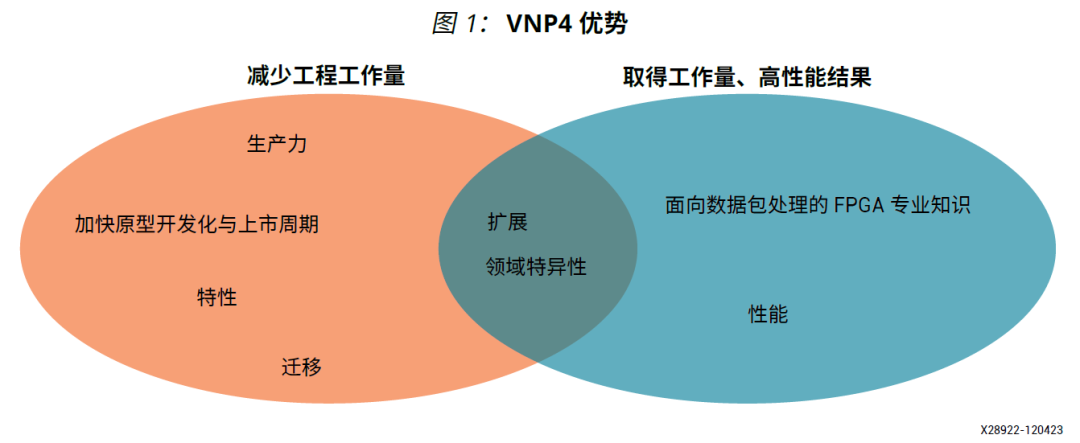

VNP4 的優勢大致可分為兩類:減少工程工作量和取得高質量、高性能結果。

1

生產力:解決方案可以減少開發工作量。

2

加快原型開發與上市周期:加快設計周期有助于您的產品更早上市。實現多個設計選項的迭代更為簡便、快速。

3

特性:廣泛的特性有助于您實現產品差異化,包括 User Metadata 和 User Externs 中的選項。

4

遷移:設計意圖可以從一個 FPGA 或 SoC 遷移到另一個。

5

擴展:由 VNP4 生成的數據包處理塊可以并行或串行部署,以支持諸如多級解析和多數據流水線系統等功能。

6

領域特異性:這種高級抽象解決方案具有領域特異性,使您能夠在不犧牲性能情況下充分發揮抽象的優勢。

7

面向數據包處理的 FPGA 專業知識:此解決方案以及硬件實現的質量印證了著我們在高吞吐量數據包處理領域深耕高速 FPGA 設計與存儲器子系統多年的經驗。

8

性能:此系統已經進行全新設計,以確保高吞吐量、低時延和最低資源占用。

編程協議不受數據包處理影響

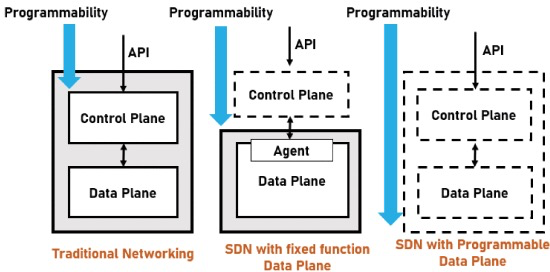

P4 是一種行業標準的、領域特定的編程語言,用于需求捕獲且不依賴變成協議。VNP4 可以將 P4

設計意圖轉換為 AMD FPGA 或自適應 SoC 的設計解決方案,并支持程序員通過明確指定報頭與數據包處理要求創建新的數據平面。為了實現 P4 的設計,編譯器將預期功能映射到 VNP4 RTL 引擎與軟件驅動程序的定制數據平面架構上。該映射選擇適當的引擎類型,并根據 P4 指定的處理對其進行定制。用于實現此目標的專用引擎包括解析引擎、匹配操作引擎和反向解析引擎,均根據應用特定的需求生成。

生成的 RTL 集成到 AMD Vivado 設計套件的封裝 IP 中,可以立即與其它標準 IP(如媒體訪問控制器)結合使用,以創建完整的設備設計。然后對設計進行綜合,并為目標設備生成 bit 文件。即使在生成綜合設計數據之前,也可以獲得關鍵的設計指標,如所需的時延和存儲器資源。

現有 AMD 解決方案基于數百個客戶反饋意見以及從早期迭代收集的信息優化而成。最新一代工具的三大特點包括:

原生支持 P416 語言

算法內容可尋址存儲器技術

致力于實現高效資源利用和可靠時序收斂

-

FPGA

+關注

關注

1630文章

21783瀏覽量

605020 -

soc

+關注

關注

38文章

4193瀏覽量

218736 -

數據包

+關注

關注

0文章

266瀏覽量

24437 -

Vivado

+關注

關注

19文章

815瀏覽量

66769

原文標題:白皮書 | 利用 P4 與 Vivado 工具簡化數據包處理設計

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

I2C總線數據包結構詳解

mtu配置步驟詳解 mtu與數據包丟失的關系

鞍山163.18平米戶外P4條柵屏安裝完工

利用P4與Vivado工具簡化數據包處理設計

利用P4與Vivado工具簡化數據包處理設計

評論