雖然推動(dòng)業(yè)界向小型基站轉(zhuǎn)變的因素眾多,但可能最重要的是,消費(fèi)者想要隨時(shí)隨地都能快速有效地連接到服務(wù)提供商,而服務(wù)提供商需要做的就是找到更具成本效益的方法來(lái)為他們的用戶提供所需要的高帶寬。方法之一如圖1左邊所示,就是在集中式和標(biāo)準(zhǔn)化服務(wù)器硬件中利用現(xiàn)有的高速光纖互連來(lái)加強(qiáng)無(wú)線基站的基帶處理。使用光纖和標(biāo)準(zhǔn)通訊信道(例如CPRI)連接遠(yuǎn)程無(wú)線電頭端(Remote Radio Heads, RRH)的連接已完成。可以接入到他們自己的光纖的運(yùn)營(yíng)商可能發(fā)現(xiàn)這個(gè)方法具有高成本效益。使用標(biāo)準(zhǔn)服務(wù)器有可能使得運(yùn)營(yíng)商將某些處理功能轉(zhuǎn)移到更接近消費(fèi)者,從而提供新的特性和營(yíng)收來(lái)源。

另一個(gè)方法就是小型基站,如圖1右側(cè)所示,使用了幾種不同類型的蜂窩(故常被稱為異構(gòu)網(wǎng)絡(luò))來(lái)提供不同的覆蓋范圍。這些基站將無(wú)線電前端和基帶后端功能結(jié)合在集成的小型空間內(nèi),無(wú)需安裝昂貴的無(wú)線電塔。這使它更容易部署附加容量到快速增長(zhǎng)的區(qū)域,或者覆蓋沒(méi)有被大型無(wú)線電塔覆蓋的盲區(qū)。較小的覆蓋區(qū)域可能無(wú)需使用高速光纖來(lái)連接網(wǎng)絡(luò),而且可能利用其它現(xiàn)有的銅纜連接用于回程。

圖1:集中式網(wǎng)絡(luò)與小型基站網(wǎng)絡(luò)的比較

在這樣的部署下,小型基站比更集中的方法有完全不同的DSP要求。

實(shí)施小型基站的DSP要求

DSP處理器供應(yīng)商傾向于將開(kāi)發(fā)工作集中在像家庭基站(Femtocell)這樣的最大批量的市場(chǎng)上。這些設(shè)備的范圍較小,通常位于住宅內(nèi)或在一個(gè)戶外熱點(diǎn)內(nèi),這意味著容易部署,且可提供擴(kuò)展而無(wú)需無(wú)線電塔的占用空間。家庭基站對(duì)成本、占用空間和功率最為敏感,因而集成式解決方案往往成為首選方案。通常在Femto級(jí)的設(shè)備中,單個(gè)DSP就是一個(gè)主要處理器件,并且在單一處理器件中結(jié)合了無(wú)線電相關(guān)功能和基帶功能。

當(dāng)轉(zhuǎn)變到Pico級(jí)和Micro級(jí)設(shè)備時(shí),便需要更多的覆蓋范圍、更大的處理功率、和各種不同的接口。典型設(shè)計(jì)會(huì)利用或許來(lái)自現(xiàn)有Femto方案的DSP,然后采用SoC FPGA來(lái)增強(qiáng),以提供額外的DSP能力和承擔(dān)系統(tǒng)管理和橋接或接口功能。

隨著SoC FPGA的DSP能力不斷發(fā)展,已使其成為DSP處理器的合適配套器件。例如,F(xiàn)PGA能夠?qū)崿F(xiàn)并行DSP管線(pipeline),從而進(jìn)行管理,提供滿足實(shí)時(shí)帶寬需求的高效能方案,這對(duì)于由DSP處理器提供的更多串行處理方法是一個(gè)極佳的補(bǔ)充。基于閃存的FPGA還可提供具有更低靜態(tài)功耗的DSP能力,因?yàn)镕PGA架構(gòu)配置了非易失性單元,所以每個(gè)單元的泄漏電流比基于SRAM的FPGA減小1000倍。低靜態(tài)功耗是重要的,因?yàn)閷?duì)于小型基站部署來(lái)說(shuō),電力是非常珍貴的。SoC FPGA提供附加的橋接、緩沖、轉(zhuǎn)化和安全能力,可以滿足小尺寸、低成本和小型空間的關(guān)鍵要求。

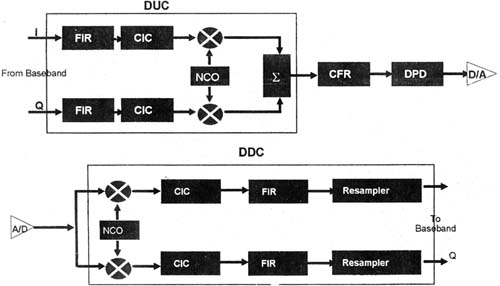

使用美高森美SmartFusion2 SoC FPGA的設(shè)計(jì)案例如圖2所示。SoC FPGA管理網(wǎng)絡(luò)接口,通過(guò)JESD204X接口連接到外部ADC/DAC,并分擔(dān)DSP中被卸載的關(guān)鍵前端DSP功能提供硬件加速。能夠分擔(dān)DSP中各種物理層功能,例如峰值因素衰減(Crest factor Reduction, CFR),并在SoC FPGA上實(shí)現(xiàn)它們,就可以釋放出巨大的帶寬。

圖2:使用美高森美SmartFusion2 SoC FPGA和DSP的小型基站設(shè)計(jì)。

而且,在SoC FPGA上實(shí)現(xiàn)的網(wǎng)絡(luò)接口和橋接功能,如CPRI或以太網(wǎng),可以使小型基站能夠與各種回程網(wǎng)絡(luò)連接。這只是在DSP和SoC FPGA之間如何劃分內(nèi)存、處理和接口管理來(lái)改進(jìn)整個(gè)系統(tǒng)設(shè)計(jì)的案例之一而已。

小型基站方案必須滿足安全要求。例如,保護(hù)小型基站設(shè)計(jì)的知識(shí)產(chǎn)權(quán)(IP),防止逆向工程或復(fù)制是至關(guān)重要的。片上(On-chip)嵌入式架構(gòu)(fabric-embedded)的配置存儲(chǔ)器和加密位流(bit stream)編程可以自動(dòng)保護(hù)設(shè)計(jì)IP,即便在一個(gè)不安全設(shè)施中進(jìn)行生產(chǎn)期間,IP也受到保護(hù)。額外的安全性問(wèn)題之所以會(huì)發(fā)生,是因?yàn)樾⌒突驹O(shè)備部署在一個(gè)難以進(jìn)入的位置上,例如在一個(gè)大的無(wú)線電塔或集中式設(shè)施,因而難以獲得保護(hù)免受入侵。在一些較易進(jìn)入的位置上,設(shè)備需要主動(dòng)的篡改防護(hù),并免受先進(jìn)入侵技術(shù)使用邊信道(side-channel)攻擊,如差分功率分析(Differential Power Analysis, DPA)。這里,我們推薦針對(duì)配置和位流加載的內(nèi)置防篡改能力和DPA-resistant算法。網(wǎng)絡(luò)接口也可成為攻擊來(lái)源,因此FPGA必須具有確保遠(yuǎn)程更新(例如通過(guò)加密和驗(yàn)證配置位流)的特性,并實(shí)現(xiàn)安全的啟動(dòng)功能(防止受到試圖替換CPU啟動(dòng)代碼的攻擊)。

支持安全啟動(dòng)在小型基站設(shè)計(jì)中被視為全球主要運(yùn)營(yíng)商的一個(gè)要求,因?yàn)樾⌒突救菀资艿轿锢砉粢约盎诰W(wǎng)絡(luò)的攻擊。假如小型基站的啟動(dòng)代碼能夠被盜用,例如被攻擊者安裝了隱匿程序(rootkit),而這些程序存留在啟動(dòng)順序后或甚至在啟動(dòng)代碼遠(yuǎn)程更新后,網(wǎng)絡(luò)的其余部分便會(huì)更易受到進(jìn)一步攻擊和利用。潛在的機(jī)密數(shù)據(jù)損失(可能是數(shù)百萬(wàn)客戶的信用卡交易),不管是對(duì)需要保護(hù)客戶數(shù)據(jù)安全的企業(yè),還是保護(hù)企業(yè)的客戶機(jī)密數(shù)據(jù)的小型基站設(shè)備公司來(lái)說(shuō)都是災(zāi)難性的。美高森美的參考設(shè)計(jì)演示了安全啟動(dòng)來(lái)簡(jiǎn)化設(shè)計(jì)中實(shí)現(xiàn)過(guò)程。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21794瀏覽量

605129 -

基站

+關(guān)注

關(guān)注

17文章

1402瀏覽量

66879

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ARM、MCU、DSP、FPGA、SOC各是什么?區(qū)別是什么?

小型蜂窩基站長(zhǎng)期演進(jìn)軟件中的挑戰(zhàn)

小型蜂窩基站的實(shí)現(xiàn)

基站市場(chǎng)多核DSP會(huì)取代ASIC/FPGA嗎

FPGA與DSP競(jìng)爭(zhēng)新一代基站設(shè)施

FPGA和DSP在無(wú)線基站中的組合

ARM、MCU、DSP、FPGA、SoC的區(qū)別是什么

小型蜂窩基站面臨的挑戰(zhàn)

FPGA和DSP組合在無(wú)線基站中的應(yīng)用

基于FPGA和DSP的微小型捷聯(lián)慣導(dǎo)系統(tǒng)的設(shè)計(jì)

德州儀器推出面向小型蜂窩基站及宏基站的多標(biāo)準(zhǔn)SoC

基于FPGA和DSP組合在無(wú)線基站中的應(yīng)用分析

Altera徹底改變基于FPGA的浮點(diǎn)DSP

如何通過(guò)高性能CPU和FPGA可重編程的SoC架構(gòu)應(yīng)對(duì)5G挑戰(zhàn)

SoC FPGA的DSP能力應(yīng)對(duì)新興的小型基站需求

SoC FPGA的DSP能力應(yīng)對(duì)新興的小型基站需求

評(píng)論