Altium Designer 24.10.1

發(fā)布時(shí)間:2024年10月10日

Altium Designer 24.10.1離線包

15天免費(fèi)試用 Altium Designer

原理圖輸入改進(jìn)

支持正常模式下的空子部件

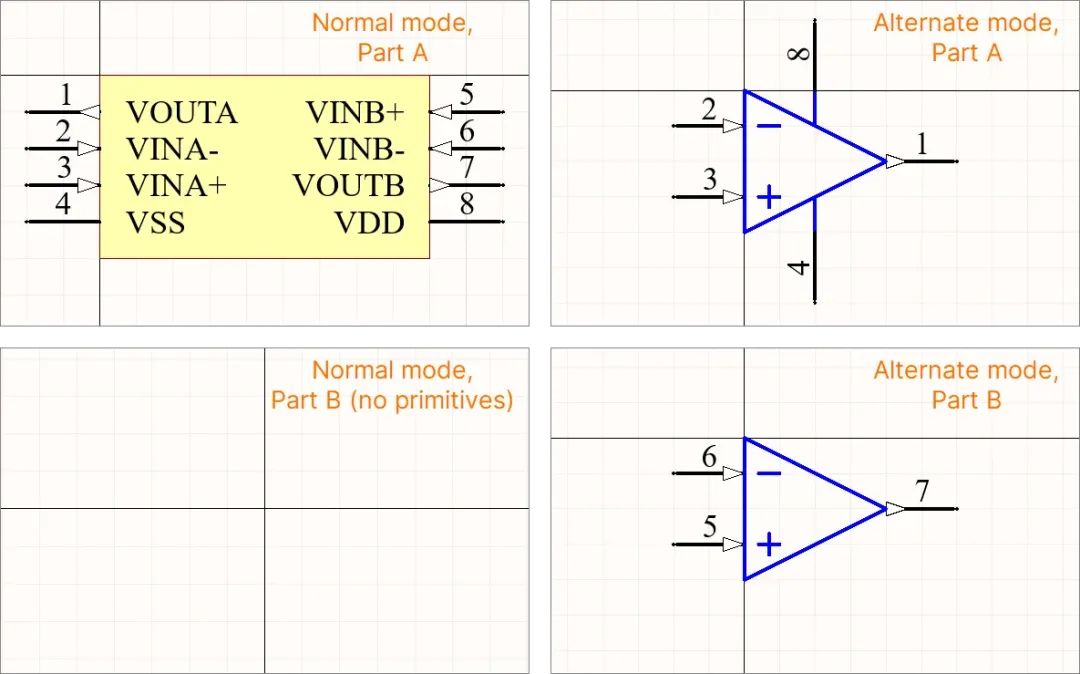

改進(jìn)了單部件/多部件符號(hào)的處理功能,并將適用于Alternate顯示模式的相同特性和功能擴(kuò)展至Normal顯示模式。例如,現(xiàn)在可以在Normal顯示模式下以單個(gè)符號(hào)表示元件,而在其Alternate模式下則以兩個(gè)符號(hào)表示,如下圖所示。

如果一個(gè)多部件元件僅在一個(gè)子部件中定義了基元,則當(dāng)該子部件被放置在原理圖圖紙上時(shí),無(wú)論當(dāng)前處于何種顯示模式下以及無(wú)論哪些子部件包含基元(無(wú)論是否包含第一個(gè)子部件),其位號(hào)標(biāo)識(shí)符后綴均將被隱藏。

如果多部件元件在其視圖模式(Normal或Alternate模式)下包含空子部件,則在放置過(guò)程中這些子部件將被忽略。

如果一個(gè)元件包含沒(méi)有基元的子部件,且這些子部件未被放置在原理圖上,則在進(jìn)行設(shè)計(jì)確認(rèn)時(shí)無(wú)論處于何種顯示模式下,元件違規(guī)中均不會(huì)出現(xiàn)任何Unused子部件。

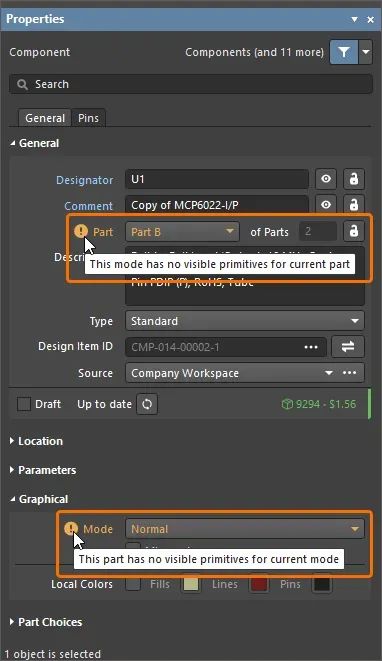

此外,現(xiàn)在還可以將部件或顯示模式更改為不含任何基元的模式。當(dāng)選定空子部件或顯示模式時(shí),Properties面板上的相應(yīng)入口旁邊即會(huì)顯示一個(gè)警告圖標(biāo)。

如需了解更多信息,請(qǐng)參閱 Searching for & Placing Components頁(yè)面。

PCB改進(jìn) Wire Bonding(開放測(cè)試階段)

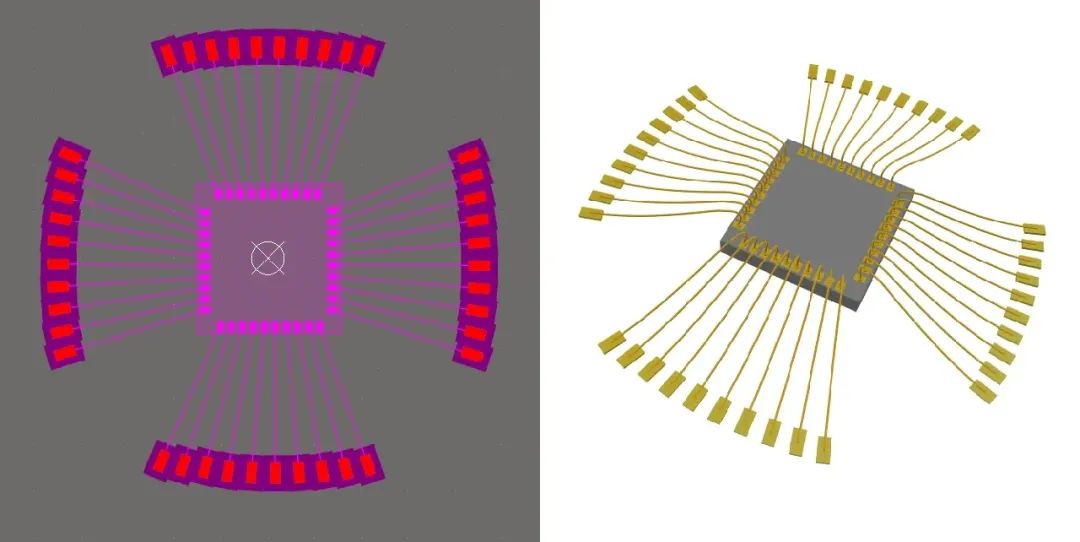

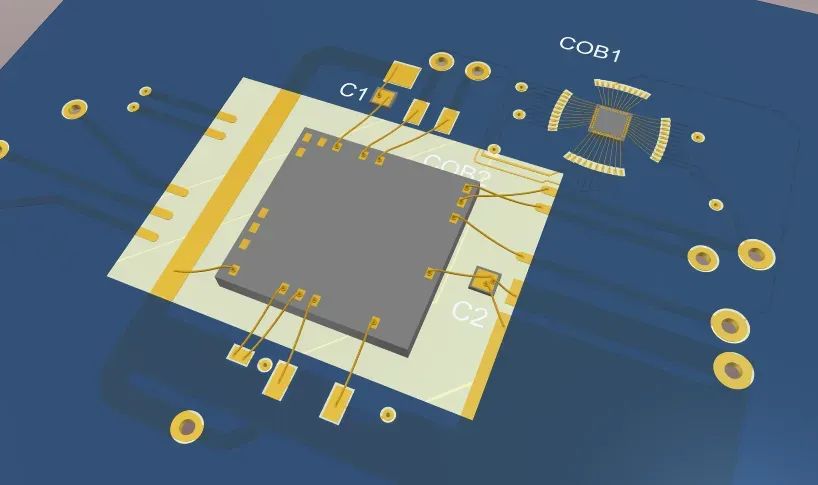

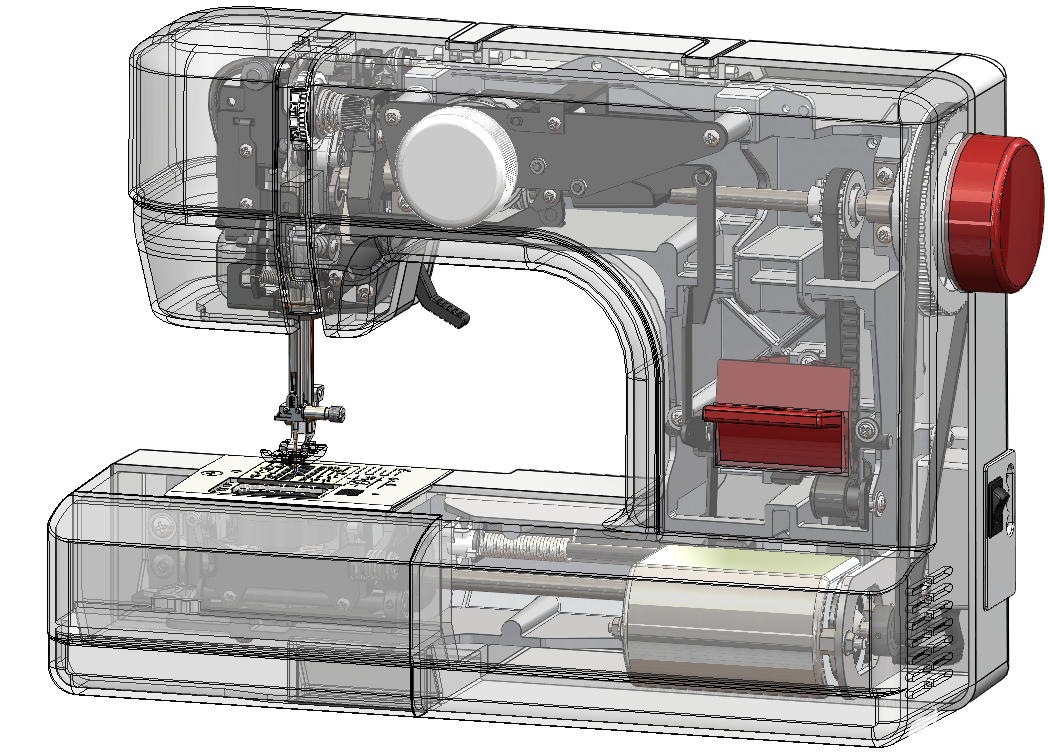

在本次發(fā)布中,添加了對(duì)使用Wire Bonding和板上芯片(CoB)技術(shù)開展混合電路板設(shè)計(jì)的支持。可通過(guò)此功能,使用定義的Die Pads(對(duì)應(yīng)于原理圖符號(hào)的引腳)創(chuàng)建元件。在將其放置到原理圖上并(通過(guò)ECO)與PCB同步后,即可使用Bond Wires將其連接到主電路板的常規(guī)焊盤(或任何銅層)上。當(dāng)連接到常規(guī)焊盤上時(shí),該焊盤將類似于Bond Finger焊盤。 可以使用作為元件封裝組成部分定義的die焊盤、bond finger焊盤和bond wires,定義一個(gè)完整的簡(jiǎn)單封裝。

支持在使用預(yù)定義Die 元件層對(duì)(Top Die / Bottom Die)時(shí),添加Die焊盤。請(qǐng)注意,當(dāng)將一個(gè)Die焊盤放置在擠壓3D體(和 Top Die / Bottom Die層)上時(shí),其將被自動(dòng)放置在該3D體的Overall Height上。

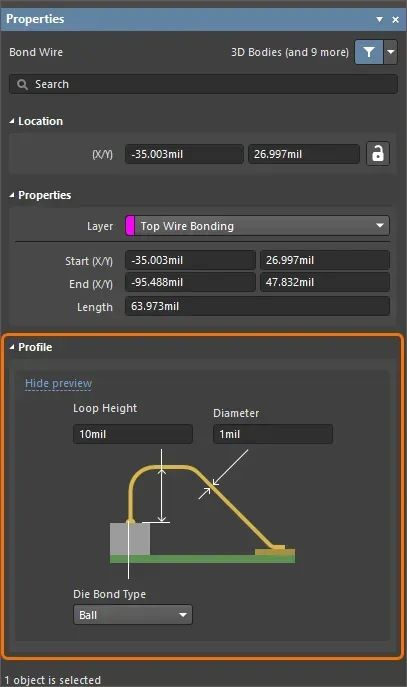

放置(Die焊盤與bond finger焊盤之間,Die焊盤與Die焊盤之間的)bond wires時(shí),可使用預(yù)定義的Wire Bonding元件層對(duì)(Top Wire Bonding / Bottom Wire Bonding)。請(qǐng)使用Place ? Bond Wire命令或者 在Active Bar上,放置bond wire。請(qǐng)使用Properties面板Profile區(qū)域中的字段,指定bond wire的Loop Height和Diameter的期望值,以及Die Bond Type (Ball或Wedge)。

在Active Bar上,放置bond wire。請(qǐng)使用Properties面板Profile區(qū)域中的字段,指定bond wire的Loop Height和Diameter的期望值,以及Die Bond Type (Ball或Wedge)。

可以將連接bond wires的常規(guī)焊盤(bond finger焊盤),與bond wires對(duì)齊。為此,請(qǐng)選定bond wires和與之連接的bond finger焊盤,右鍵單擊選定內(nèi)容,然后從右鍵單擊菜單中選擇Pad Actions ? Align Bond Finger with Bond Wire命令。

在二維和三維視圖中具有wire bonding功能的封裝示例。

當(dāng)使用Chip-on-Board法時(shí),還可以手動(dòng)放置bond wire,以將芯片的die焊盤連接到主電路板的任何銅層上。Bond wire將繼承其源die焊盤的網(wǎng)絡(luò)。既可以從同一個(gè)die焊盤上引出多條Bond wire,亦可以在主電路板的同一銅層上結(jié)束多條Bond wire。

具有wire bonding功能的PCB示例。

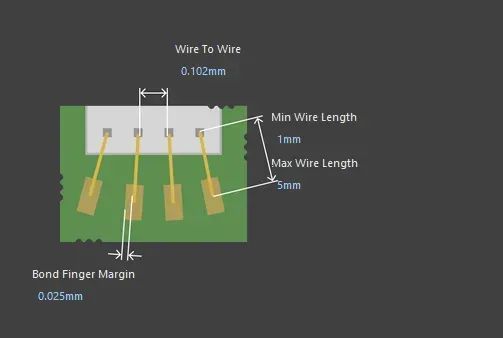

在Routing類別中,添加了一條支持wire bonding的新Wire Bonding 設(shè)計(jì)規(guī)則,當(dāng)從PCB和PCB Rules and Constraints Editor對(duì)話框中進(jìn)行訪問(wèn)時(shí)(使用先前方法進(jìn)行設(shè)計(jì)規(guī)則定義和管理時(shí)),可以在Constraint Manager的 All Rules視圖中定義該規(guī)則。可以根據(jù)該規(guī)則,針對(duì)相鄰bond wires之間的允許距離(Wire To Wire)、 Min和Max Wire Length以及Bond Finger Margin——即,bond wires與其所連接的bond finger焊盤邊緣之間的距離/填充,進(jìn)行約束定義。批量DRC支持Wire Bonding設(shè)計(jì)規(guī)則。電氣規(guī)則檢查(Un-Routed Net和Short Circuit)同樣支持Wire Bonding。

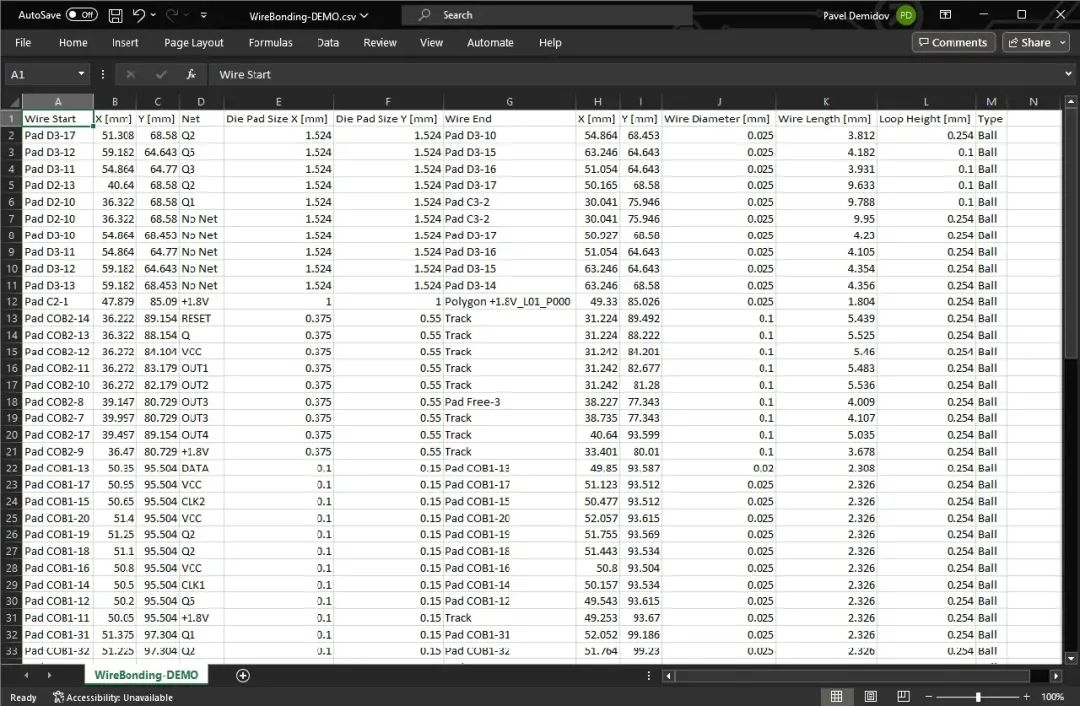

對(duì)于制造文檔,Draftsman支持在其常規(guī)電路板裝配視圖(用于主Chip-on-Board法)和 元件視圖(用于已在封裝內(nèi)完整定義wire bonding‘封裝’的情形)中進(jìn)行wire bonding。在生成常規(guī)PCB打印時(shí),還支持wire bonding信息。 能夠(以CSV格式)生成一份提供 die 焊盤和bond finger焊盤信息的 wire bonding表報(bào)告。請(qǐng)使用輸出作業(yè)文件Assembly Outputs區(qū)域的Wire Bonding Table Report輸出,添加該類型的新輸出,或者從PCB編輯器的主菜單中選定File ? Assembly Outputs ? Wire Bonding Table Report命令來(lái)生成該報(bào)告。

此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了PCB.Wirebonding選項(xiàng)時(shí)可用。 如需了解更多信息,請(qǐng)參閱Wire Bonding 頁(yè)面。

差分對(duì)相位匹配(開放測(cè)試階段)

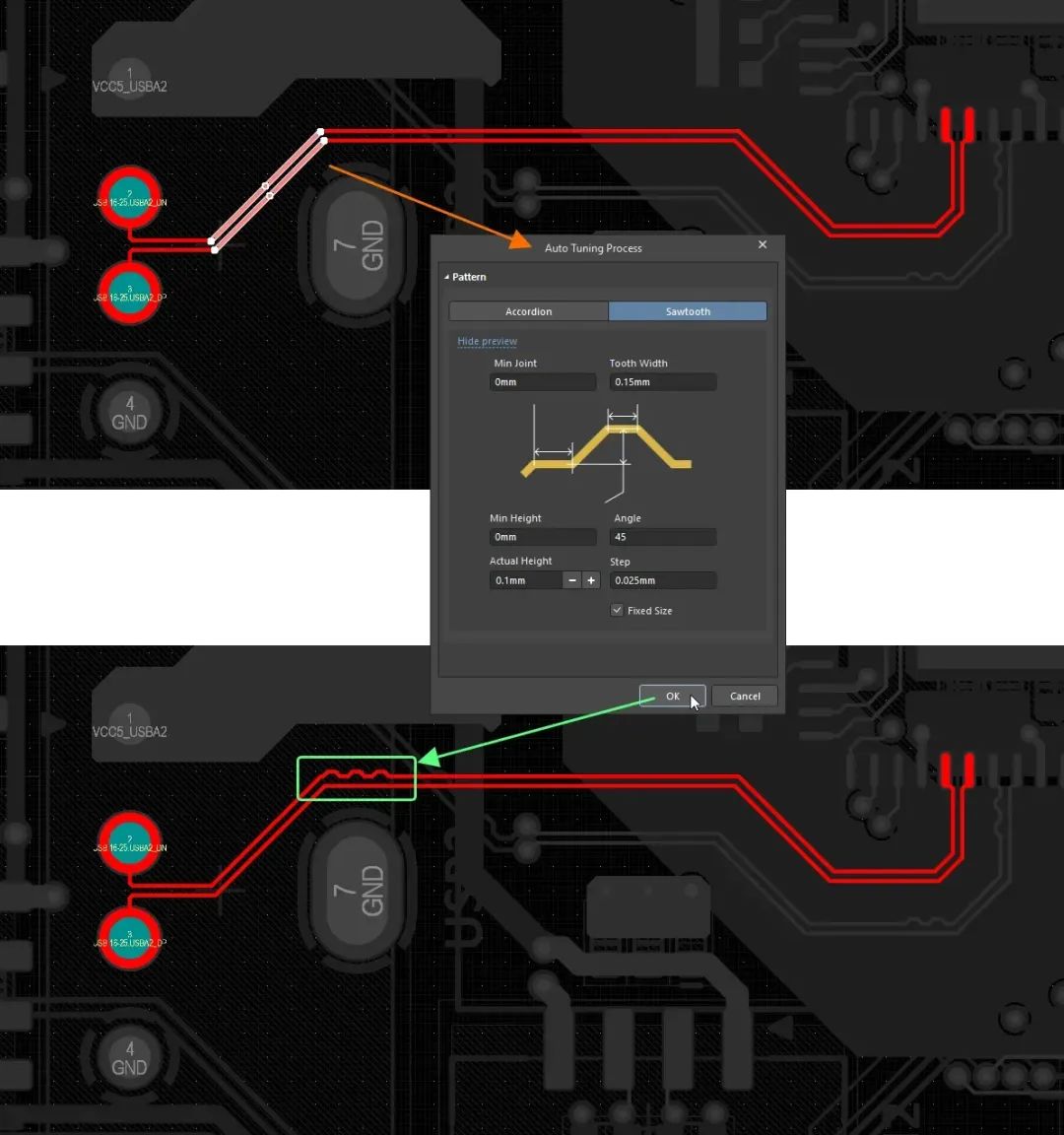

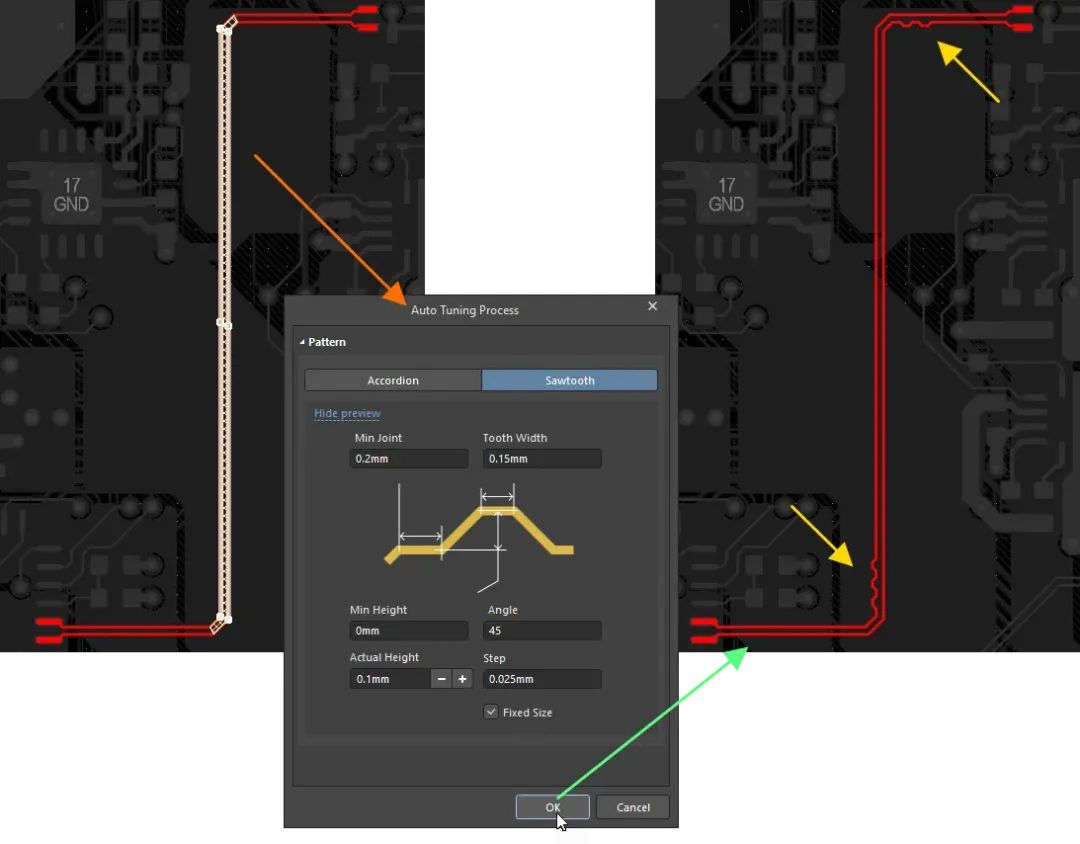

本次發(fā)布包括在進(jìn)行差分對(duì)長(zhǎng)度自動(dòng)調(diào)整時(shí),啟用差分對(duì)兩側(cè)之間的相位匹配的功能。 為了根據(jù)相關(guān)Matched Lengths約束在所需差分對(duì)兩側(cè)之間實(shí)施相位匹配,并選定Within Differential Pair Length選項(xiàng),請(qǐng)選定這些差分對(duì)的基元,然后從主菜單中選擇Route ? Automatic Length Tuning命令。在打開的Auto Tuning Process對(duì)話框中,打開一個(gè)新的Sawtooth選項(xiàng)卡,然后根據(jù)需要配置鋸齒模式參數(shù)。在該對(duì)話框中單擊OK鍵后,鋸齒調(diào)整模式將被添加到差分對(duì)兩側(cè),以均衡其長(zhǎng)度。

此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了PCB.TraceTuning.PhaseTuning選項(xiàng)時(shí)可用。 如需了解更多信息,請(qǐng)參閱Length Tuning頁(yè)面。

差分對(duì)動(dòng)態(tài)相位匹配(開放測(cè)試階段)

本次發(fā)布提供了針對(duì)差分對(duì)動(dòng)態(tài)相位匹配的支持,以確保順利進(jìn)行高速PCB設(shè)計(jì)。為了能夠以最高效率進(jìn)行差分信號(hào)傳輸,需要進(jìn)行差分對(duì)靜態(tài)相位匹配(均衡差分對(duì)兩側(cè)的長(zhǎng)度)和動(dòng)態(tài)相位匹配(沿著差分對(duì)的整個(gè)長(zhǎng)度進(jìn)行相位匹配)。

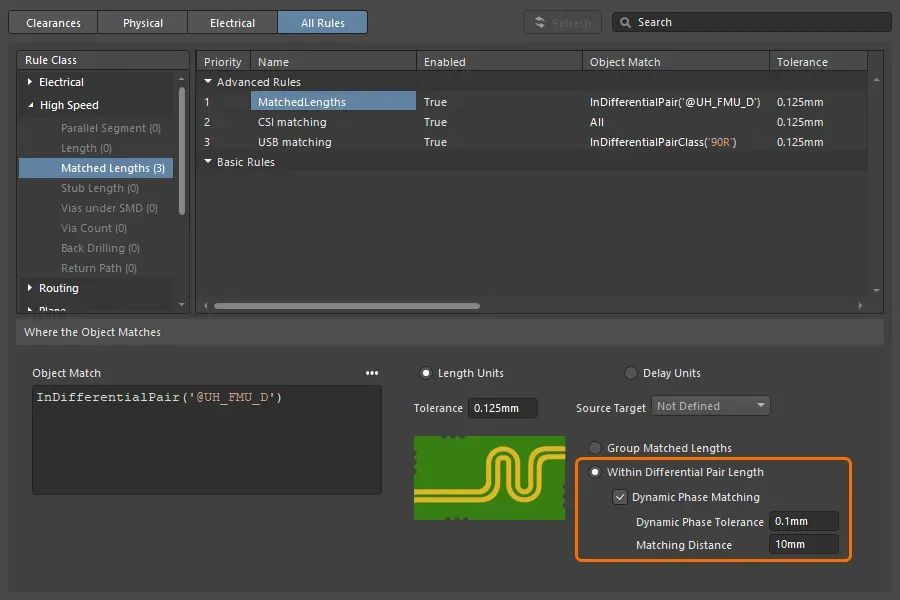

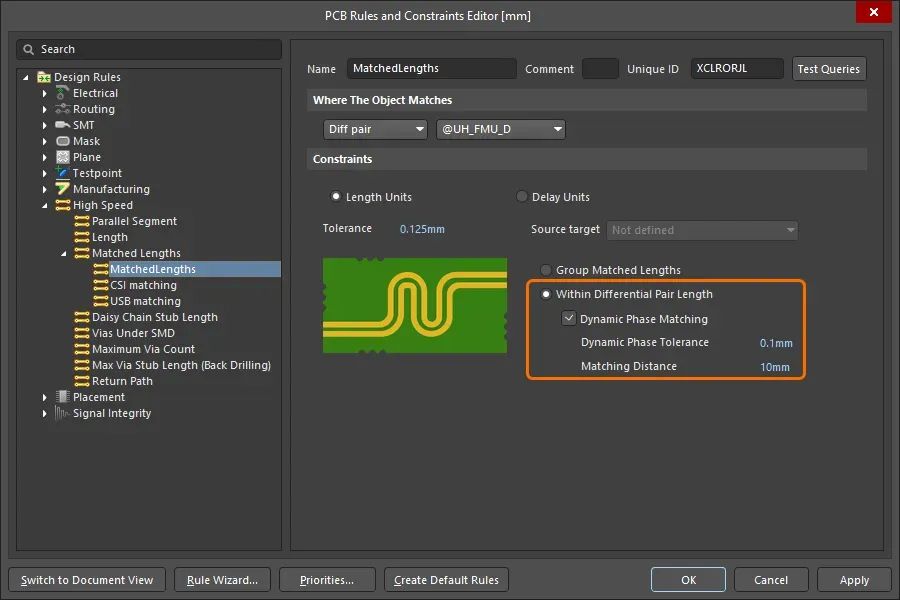

實(shí)施新的動(dòng)態(tài)相位匹配約束和相位補(bǔ)償自動(dòng)調(diào)整后,即可避免耗時(shí)的相位失配檢測(cè)和消除。 擴(kuò)展后,Matched Length設(shè)計(jì)規(guī)則具備了指定動(dòng)態(tài)相位匹配約束的功能。選定Within Differential Pair Length選項(xiàng)后,即會(huì)出現(xiàn)一個(gè)新的Dynamic Phase Matching復(fù)選框。可以在啟用該復(fù)選框后,定義以下約束:

Dynamic Phase Tolerance / Dynamic Phase Delay Tolerance – 即,差分對(duì)內(nèi)線路之間的允許相位失配程度,超過(guò)該失配程度即需進(jìn)行補(bǔ)償。

Matching Distance – 超出公差后必須進(jìn)行補(bǔ)償?shù)木嚯x。

在規(guī)則中選定Length Units或Delay Units后,即可以毫米或皮秒為單位對(duì)上述約束進(jìn)行定義。 Constraint Manager的All Rules視圖(從PCB中進(jìn)行訪問(wèn))和PCB Rules and Constraints Editor 對(duì)話框(使用先前方法進(jìn)行設(shè)計(jì)規(guī)則定義和管理時(shí))均支持此項(xiàng)增強(qiáng)規(guī)則。

在Constraint Manager中配置的動(dòng)態(tài)相位匹配約束

在PCB Rules and Constraints Editor對(duì)話框中配置的動(dòng)態(tài)相位匹配約束

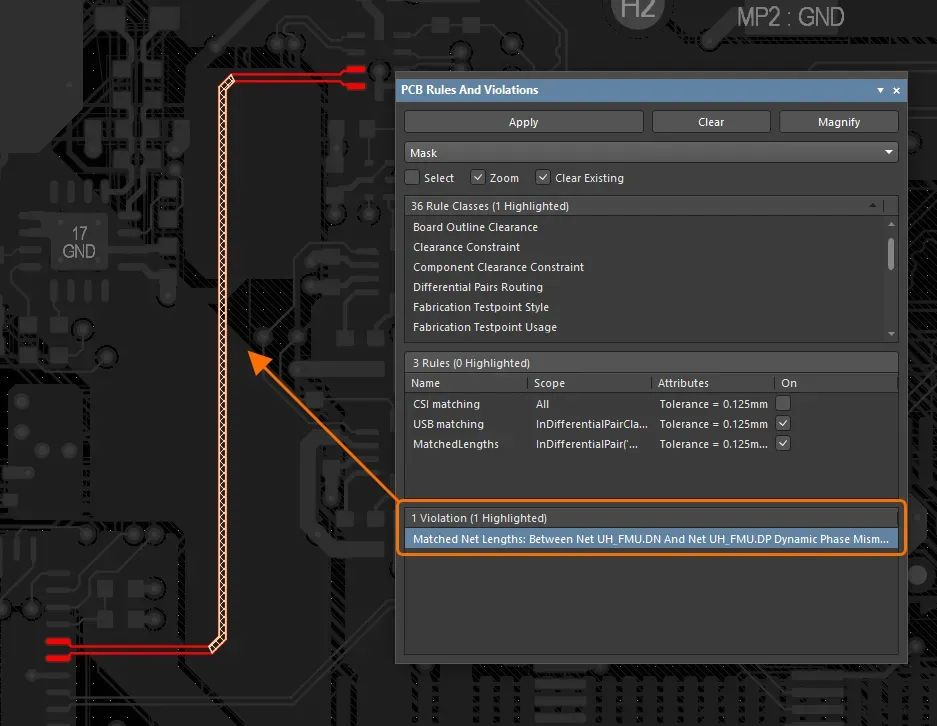

將在設(shè)計(jì)區(qū)內(nèi)的相應(yīng)導(dǎo)線上,以陰影模式標(biāo)記檢測(cè)到的規(guī)則違規(guī)(陰影將從檢測(cè)到的相位失配點(diǎn)——即超出定義公差處開始)。

可以使用Automatic Length Tuning工具,消除動(dòng)態(tài)相位匹配的違規(guī)。選定所需差分對(duì)(差分對(duì)的任何線路),然后從主菜單中選擇Route ? Automatic Length Tuning命令。在打開的Auto Tuning Process對(duì)話框的Sawtooth選項(xiàng)卡上,根據(jù)需要設(shè)置相位匹配參數(shù),然后單擊OK鍵,以添加進(jìn)行差分對(duì)動(dòng)態(tài)相位匹配所需的鋸齒模式。請(qǐng)注意,需要考慮已布線差分對(duì)兩端焊盤的電氣類型,因此如果指定了源/負(fù)載,則需要通過(guò)沿著差分對(duì)向適當(dāng)?shù)姆较蛞苿?dòng)來(lái)進(jìn)行調(diào)整。

此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了PCB.Rules.DiffpairPhaseMatching選項(xiàng)時(shí)可用。 如需了解更多信息,請(qǐng)參閱High Speed Rule Types頁(yè)面。

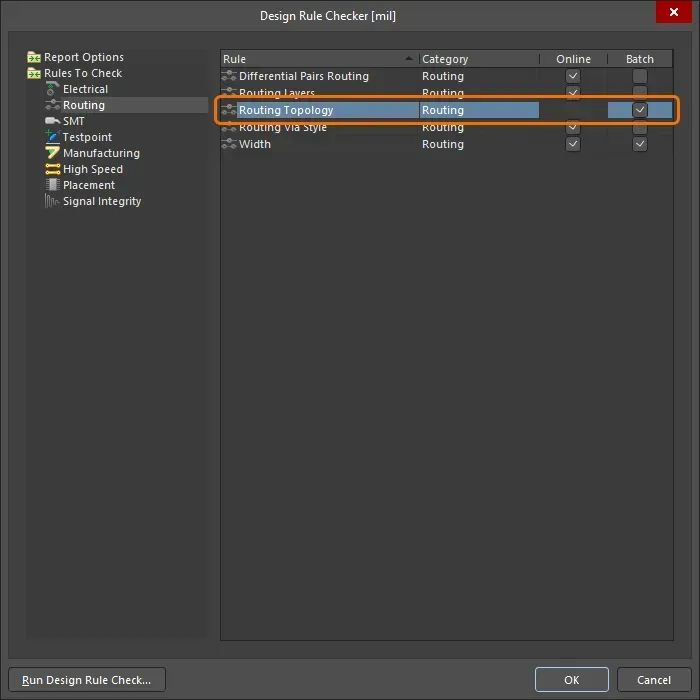

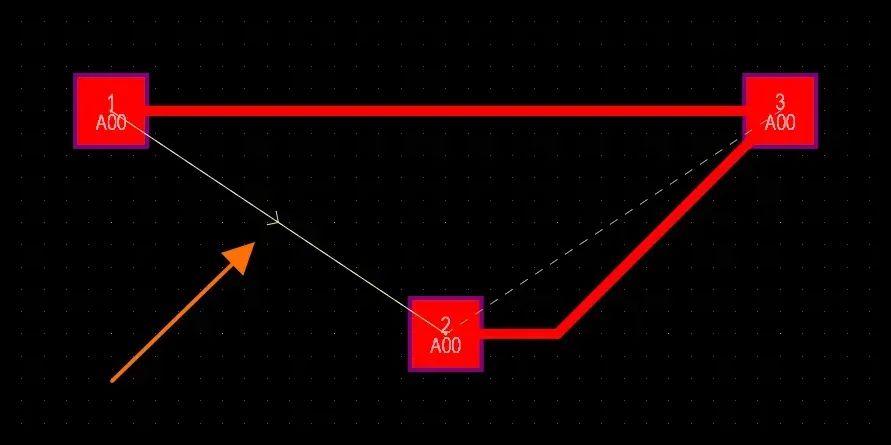

布線拓?fù)浣Y(jié)構(gòu)DRC支持(開放測(cè)試階段)

現(xiàn)在可以在Batch DRC過(guò)程中,檢查使用From-Tos定義的自定義拓?fù)浣Y(jié)構(gòu)的實(shí)現(xiàn)情況。請(qǐng)?jiān)贒esign Rule Checker對(duì)話框(Tools ? Design Rule Check)中,啟用Routing Topology設(shè)計(jì)規(guī)則類型的Batch選項(xiàng),以進(jìn)行違規(guī)檢測(cè)。

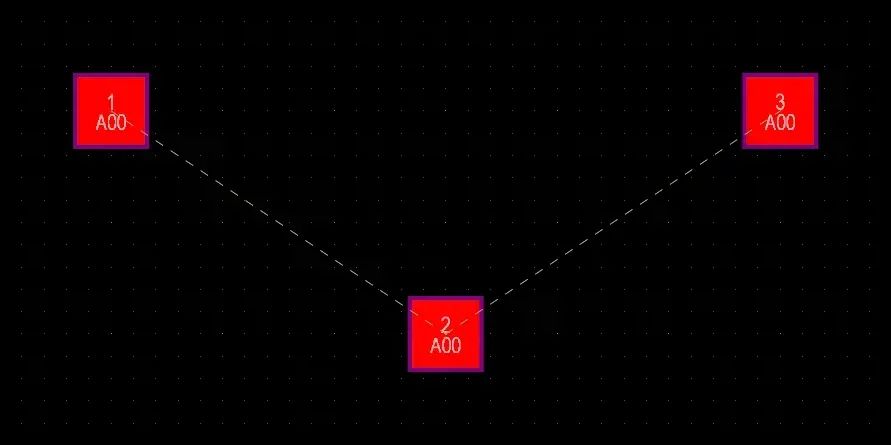

如果From-To的焊盤之間存在電氣連接,且最短路徑中包含該網(wǎng)絡(luò)的至少一個(gè)其他焊盤,則會(huì)檢測(cè)到違規(guī)。

在三個(gè)焊盤之間創(chuàng)建兩個(gè)From-Tos – 即,焊盤1與焊盤2之間以及焊盤2與焊盤3之間

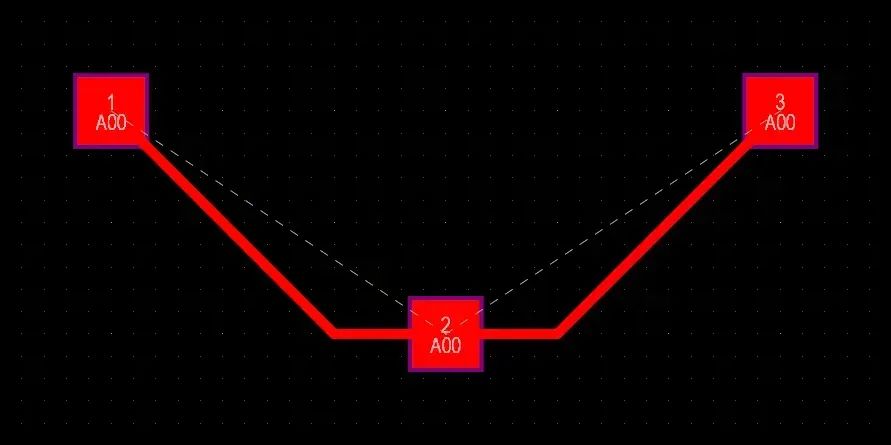

根據(jù)From-Tos的配置創(chuàng)建布線 - 焊盤1與焊盤2之間以及焊盤2與焊盤3之間均進(jìn)行了布線。未檢測(cè)到涉及Routing Topology規(guī)則的任何違規(guī)。

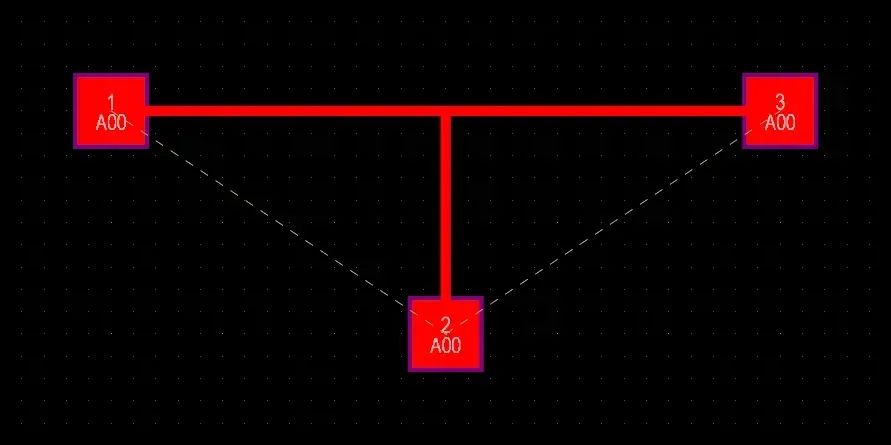

以T型分支方式創(chuàng)建布線。根據(jù)From-To的配置,路徑中不存在任何額外焊盤,因此不會(huì)檢測(cè)到涉及Routing Topology規(guī)則的任何違規(guī)。

在焊盤1與焊盤3之間以及焊盤2與焊盤3創(chuàng)建布線。該布線不會(huì)與From-To配置進(jìn)行匹配,因?yàn)樵诤副P1與焊盤2之間的路徑上存在一個(gè)額外焊盤3,因此會(huì)在焊盤1與焊盤2之間的From-To上檢測(cè)一條到涉及Routing Topology規(guī)則的違規(guī)。

對(duì)于包含大量焊盤(超過(guò)20個(gè))或基元(超過(guò)1024個(gè))的網(wǎng)絡(luò),不會(huì)檢測(cè)到違規(guī)。 此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了PCB.Rules.CheckRoutingTopology選項(xiàng)時(shí)可用。 如需了解更多信息,請(qǐng)參閱Understanding Connectivity on Your PCB 頁(yè)面。

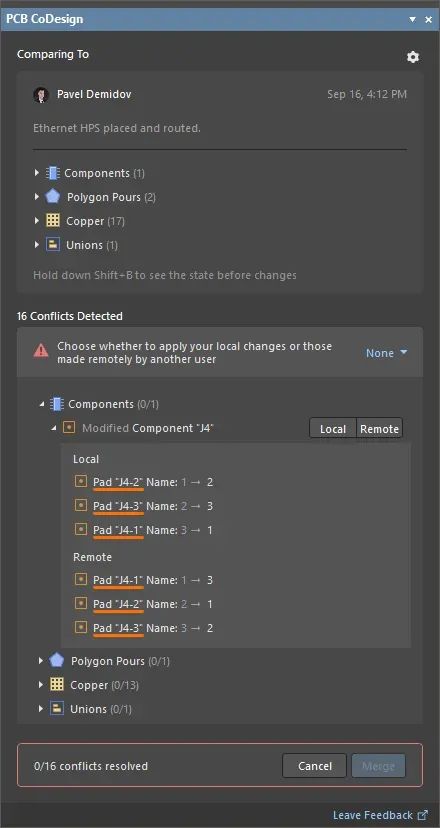

PCB CoDesign改進(jìn) 顯示存在沖突的基元名稱

當(dāng)檢測(cè)到組對(duì)象的基元之間存在沖突時(shí),現(xiàn)在會(huì)在PCB CoDesign面板的沖突列表中顯示這些基元的名稱。如下圖所示,將在基元屬性之前顯示組對(duì)象(元件焊盤)內(nèi)存在沖突的基元名稱。

如需了解更多信息,請(qǐng)參閱PCB CoDesign 頁(yè)面。

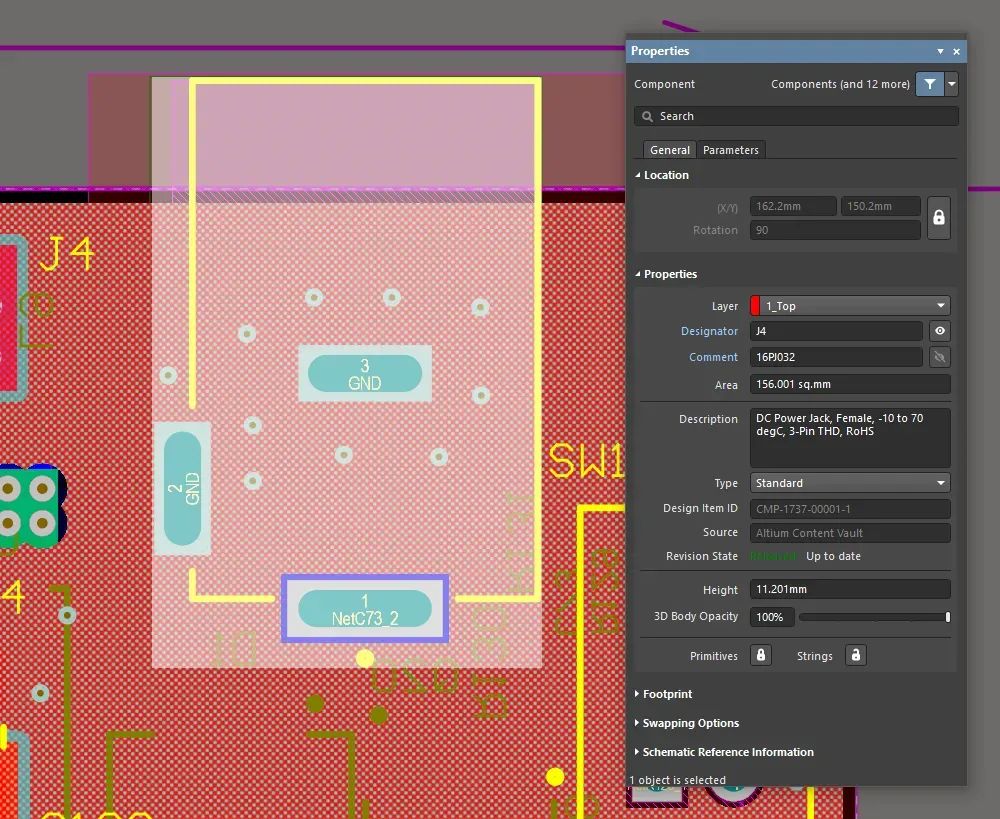

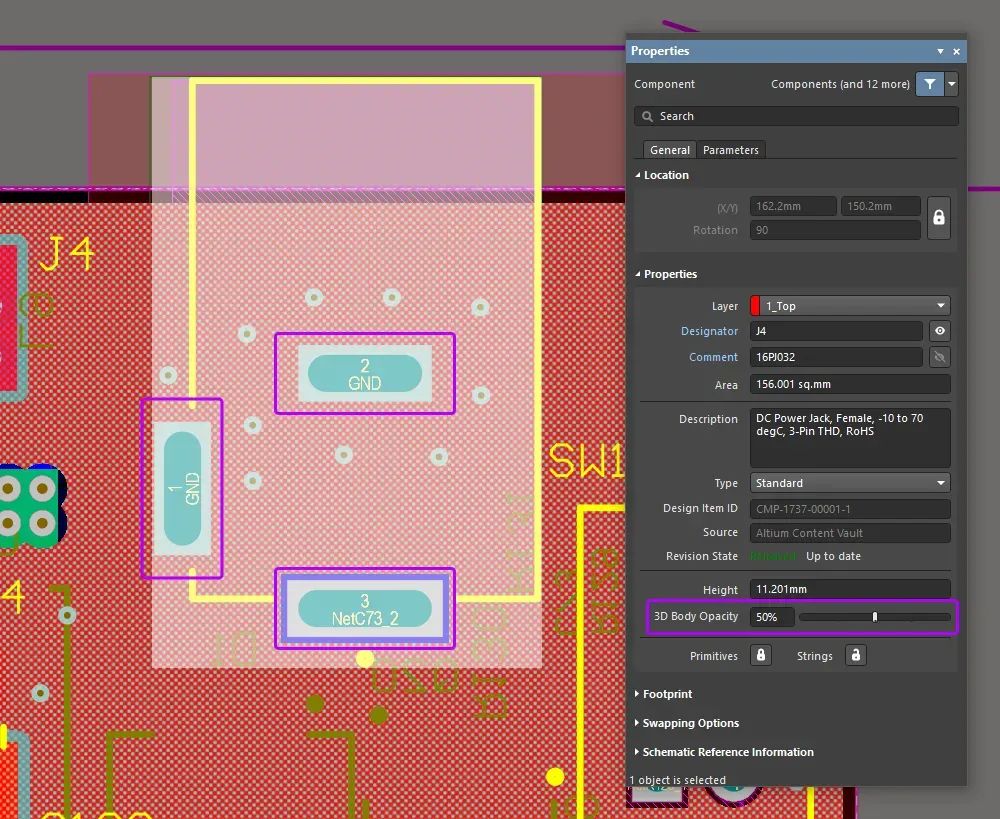

合并對(duì)象屬性

當(dāng)從兩側(cè)更改相同對(duì)象屬性且屬性值內(nèi)不存在沖突時(shí),這些更改將不再產(chǎn)生沖突,并且可以進(jìn)行合并,從而顯著減少對(duì)象沖突數(shù)量。

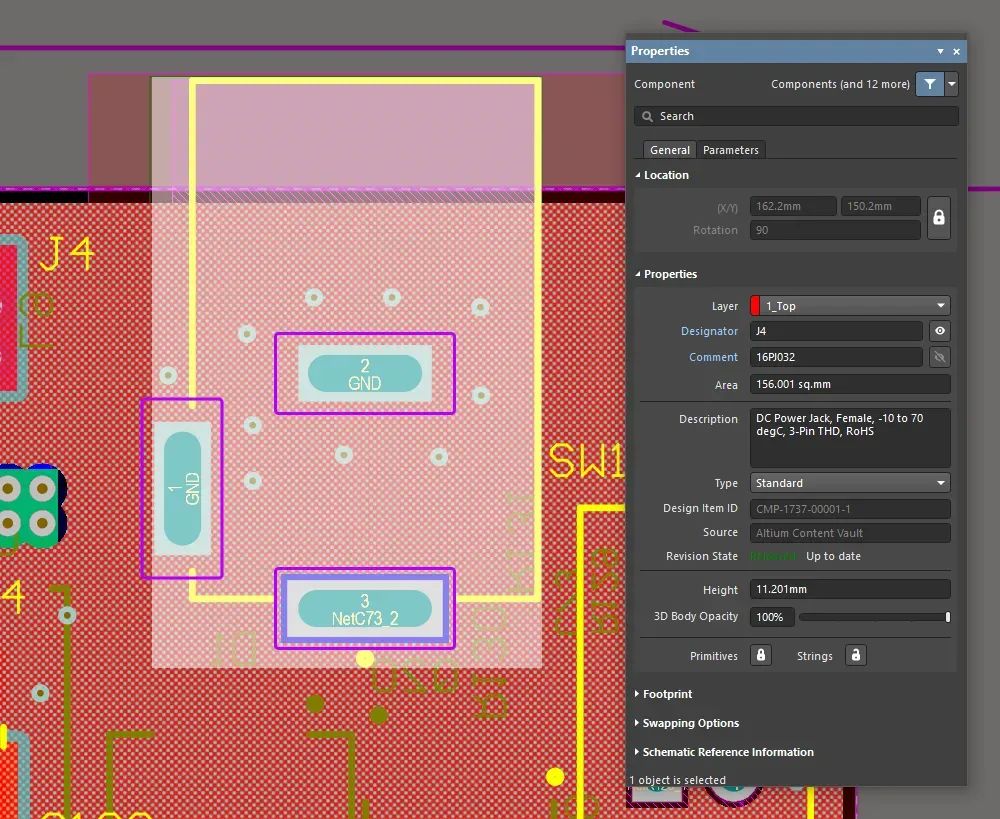

此處顯示了PCB文檔基礎(chǔ)版本中元件J4的PCB面積和屬性。

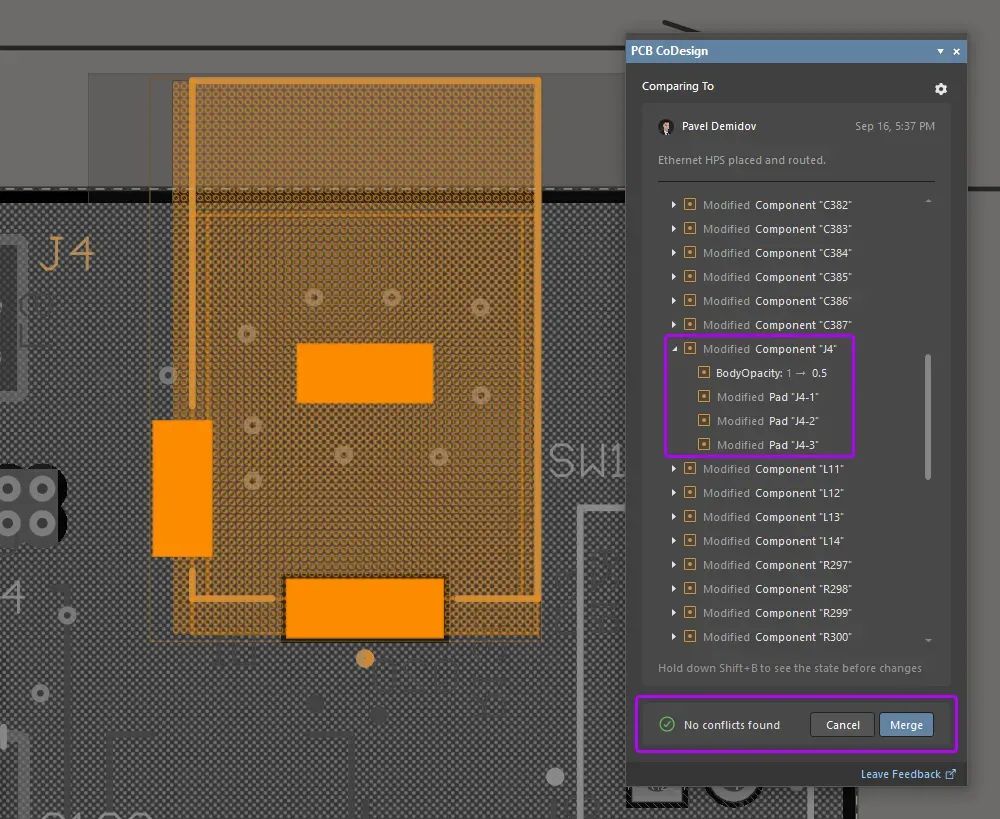

在PCB的遠(yuǎn)程版本中,更新了J4的3D體透明度和焊盤編號(hào)。

在PCB的本地工作副本中,以與遠(yuǎn)程版本相同的方式更新了J4的焊盤編號(hào)。

使用PCB CoDesigner面板進(jìn)行比較后,J4中的更改不會(huì)引起沖突。這些更改可以合并到PCB的本地副本中。

如需了解更多信息,請(qǐng)參閱PCB CoDesign頁(yè)面。

約束管理器改進(jìn) 遷移至Constraint Manager的功能(開放測(cè)試階段)

本次發(fā)布中包括從PCB Rules and Constraints Editor對(duì)話框一次性單向遷移到Constraint Manager的功能。 請(qǐng)使用PCB和原理圖編輯器主菜單中的Design ? Migrate Project to Constraint Manager Flow命令。此時(shí)將打開Migration Required對(duì)話框,提示即將進(jìn)行遷移,且在單擊該 按鈕后將無(wú)法撤消遷移。PCB設(shè)計(jì)規(guī)則和原理圖指令均將轉(zhuǎn)移到Constraint Manager中的相應(yīng)約束中。順利完成遷移后,將(在進(jìn)行遷移時(shí)編輯器處于活動(dòng)狀態(tài)的上下文中)打開Constraint Manager。

按鈕后將無(wú)法撤消遷移。PCB設(shè)計(jì)規(guī)則和原理圖指令均將轉(zhuǎn)移到Constraint Manager中的相應(yīng)約束中。順利完成遷移后,將(在進(jìn)行遷移時(shí)編輯器處于活動(dòng)狀態(tài)的上下文中)打開Constraint Manager。

如果在PCB Rules and Constraints Editor對(duì)話框中尚不存在具有默認(rèn)范圍的設(shè)計(jì)規(guī)則(例如,不存在范圍為All的Width規(guī)則),則將在進(jìn)行遷移時(shí)在Constraint Manager中創(chuàng)建該規(guī)則。 此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了ConstraintManager.ProjectMigrationWizard選項(xiàng)時(shí)可用。 如需了解更多信息,請(qǐng)參閱Defining Design Requirements Using the Constraint Manager頁(yè)面。

指令改進(jìn)

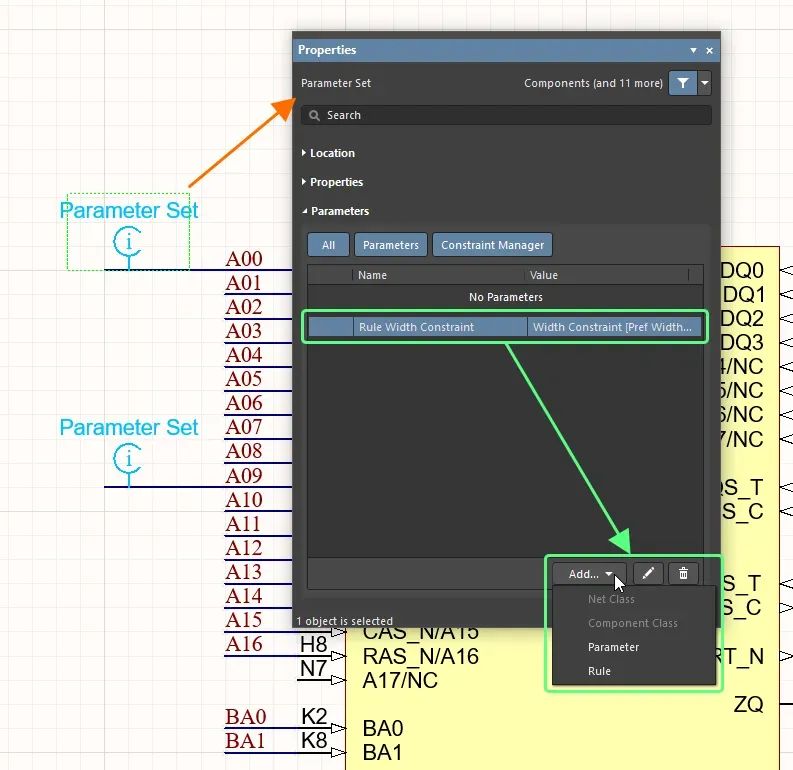

添加、更新和刪除已導(dǎo)入指令的約束 對(duì)于已導(dǎo)入指令,現(xiàn)在可以使用Properties面板為其添加、更新和刪除約束。

如需在Constraint Manager中對(duì)數(shù)據(jù)進(jìn)行更改,請(qǐng)?jiān)趶脑韴D側(cè)進(jìn)行訪問(wèn)時(shí),單擊Constraint Manager右上角的 按鈕。 如需了解更多信息,請(qǐng)參閱Defining Design Requirements Using the Constraint Manager頁(yè)面。

按鈕。 如需了解更多信息,請(qǐng)參閱Defining Design Requirements Using the Constraint Manager頁(yè)面。

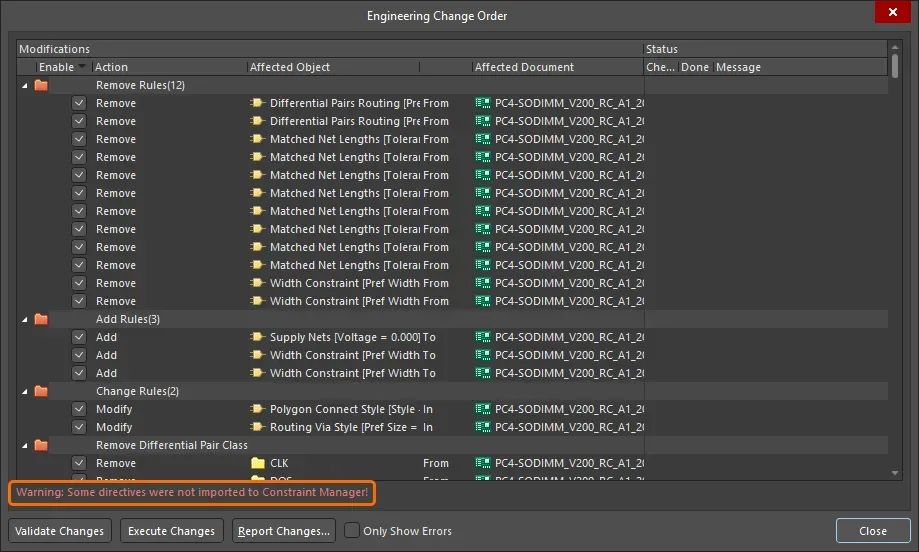

ECO內(nèi)的差異警告

如果在通過(guò)制定ECO將更改從原理圖傳遞到PCB時(shí),原理圖上存在先前未導(dǎo)入的指令,則會(huì)顯示警告。

如需了解更多信息,請(qǐng)參閱Defining Design Requirements Using the Constraint Manager頁(yè)面。

線束設(shè)計(jì)改進(jìn)

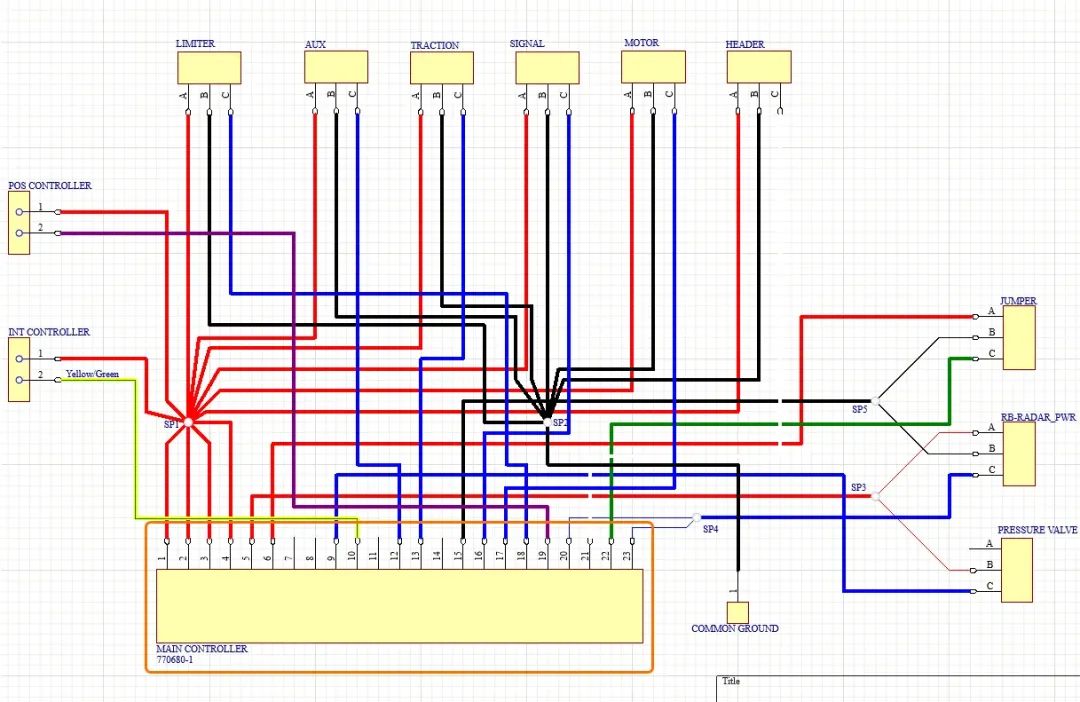

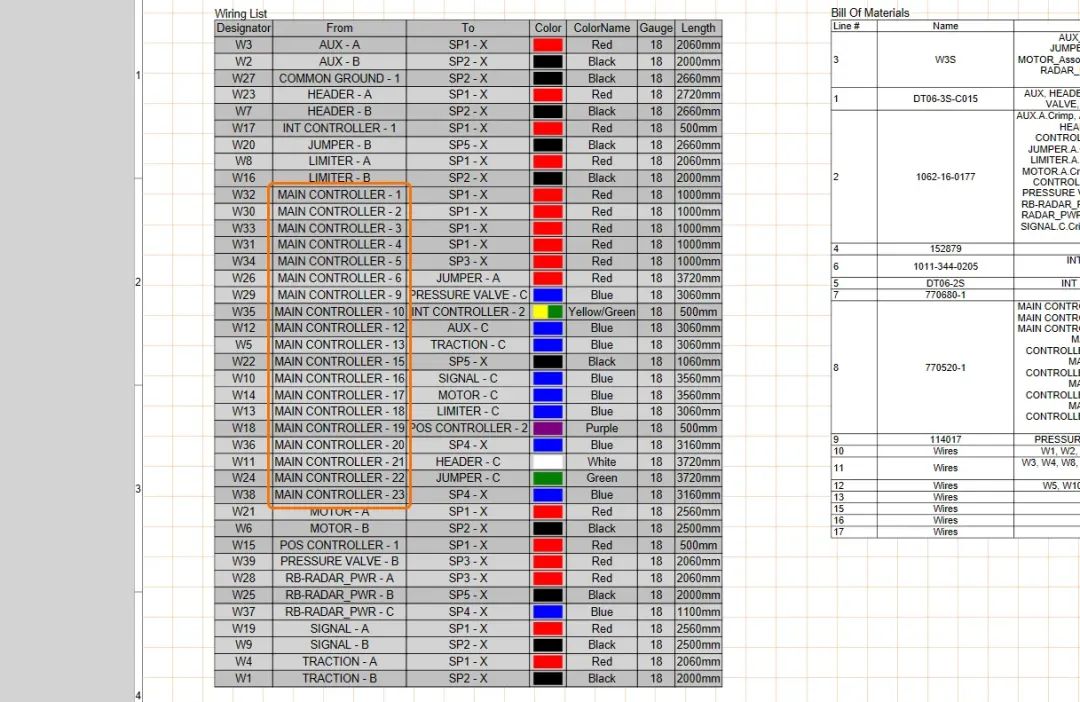

導(dǎo)線的自動(dòng)分組

對(duì)于Bulkhead Connector(具有最多型腔的連接器),將針對(duì)線束制造文檔(*.HarDwf)內(nèi)的接線列表進(jìn)行自動(dòng)分組,以確保在From列中正確分組其所有型腔。

在此設(shè)計(jì)中,由于元件MAIN CONTROLLER具有最多型腔,因此其被視為Bulkhead Connector。

在制造圖中,MAIN CONTROLLER的所有型腔均將在From列中進(jìn)行分組。

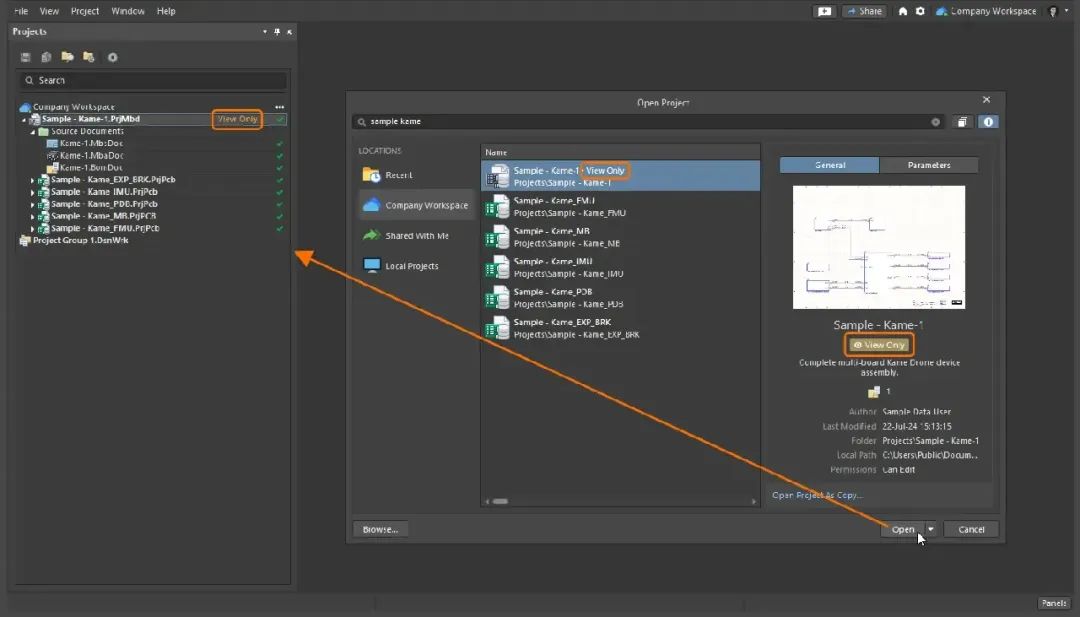

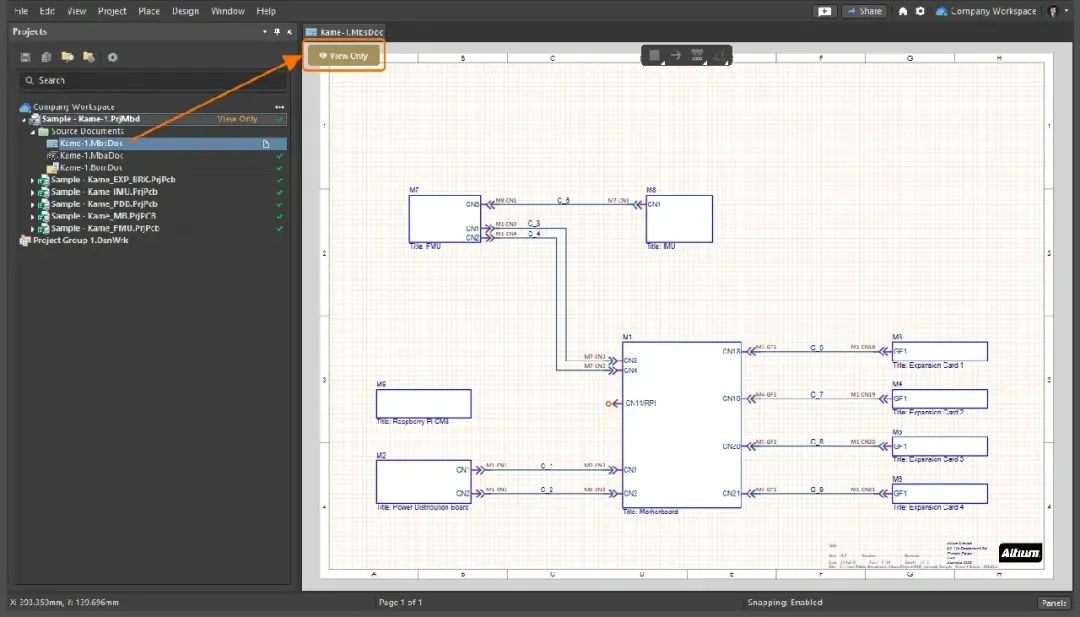

平臺(tái)改進(jìn) 線束和多板設(shè)計(jì)的僅供查看模式(開放測(cè)試階段)

針對(duì)Harness和Multi-board項(xiàng)目及其相關(guān)文檔,引入了僅供查看模式。將其引入后,現(xiàn)在可以查看和探索以前可能無(wú)法訪問(wèn)的功能,并與處理上述類型項(xiàng)目的同事進(jìn)行協(xié)作。 在僅供查看模式下,不得對(duì)項(xiàng)目和文檔進(jìn)行更新,亦不得對(duì)其進(jìn)行訪問(wèn)。當(dāng)在僅供查看模式下打開某個(gè)項(xiàng)目時(shí),Projects面板將顯示View Only,如下圖所示。

Multi-board項(xiàng)目的僅供查看模式示例。該項(xiàng)目將在Open Project對(duì)話框和Projects面板中被標(biāo)記為View Only。

當(dāng)打開項(xiàng)目的源文檔時(shí)(如此處Multi-board原理圖文檔所示),其同樣會(huì)被標(biāo)記為View Only,因此該文檔無(wú)法進(jìn)行修改。

盡管您無(wú)法修改任何內(nèi)容,但可以生成PDF等源文檔輸出以及來(lái)自關(guān)聯(lián)OutJobs的已定義輸出。

此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了System.ViewOnlyMode.Support選項(xiàng)時(shí)可用。 如需了解更多信息,請(qǐng)參閱Designing with Multiple PCBs和Harness Design 頁(yè)面。

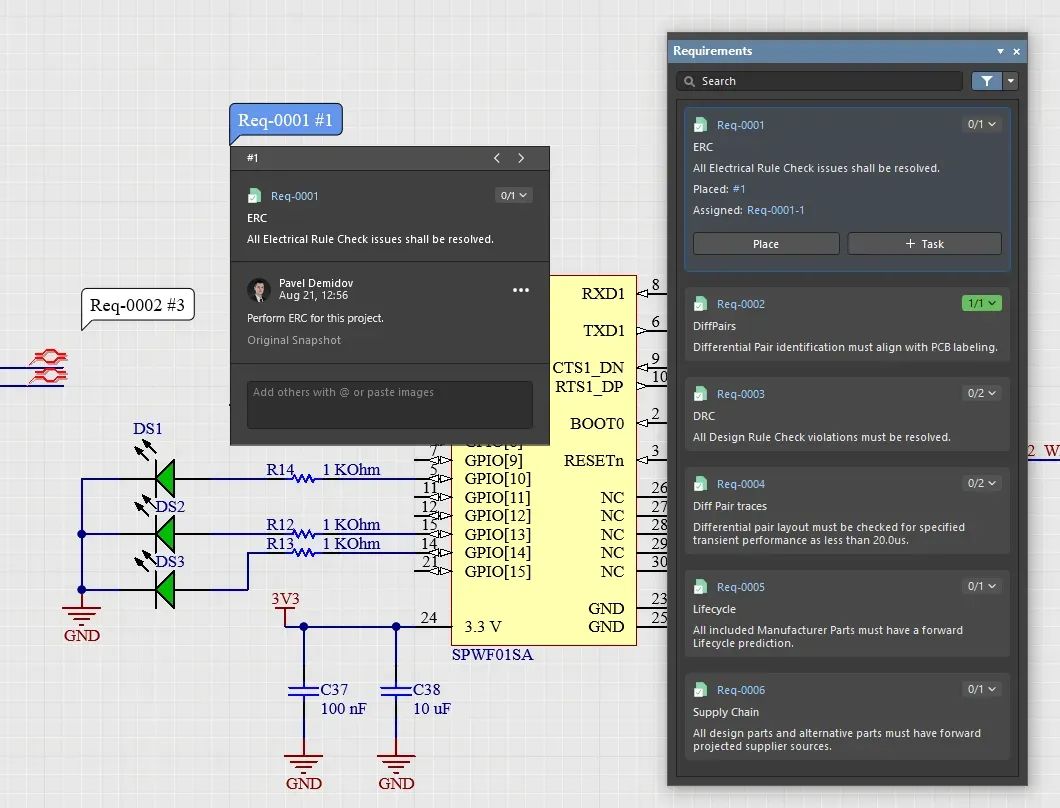

數(shù)據(jù)管理改進(jìn) 要求管理(開放測(cè)試階段)

本次發(fā)布中針對(duì)存儲(chǔ)在連接的Altium 365 Workspace中的PCB設(shè)計(jì)項(xiàng)目,提供了通過(guò)Requirements and Systems Portal處理已定義系統(tǒng)要求的功能。后者是一種高級(jí)工程管理應(yīng)用程序,用于在系統(tǒng)設(shè)計(jì)開發(fā)階段確保規(guī)格和性能的合規(guī)性。

當(dāng)針對(duì)Altium 365 Workspace啟用時(shí),Requirements and Systems Portal將通過(guò)交換設(shè)計(jì)數(shù)據(jù)和正式的Requirement實(shí)例,與PCB設(shè)計(jì)項(xiàng)目進(jìn)行集成。可以將在Requirements and Systems Portal中創(chuàng)建的系統(tǒng)要求,作為活動(dòng)實(shí)例放置在設(shè)計(jì)文檔中,然后作為任務(wù)進(jìn)行引用,并最終將其標(biāo)記為已驗(yàn)證狀態(tài),以確認(rèn)該要求的合規(guī)性。

在Altium Designer中,將通過(guò)Requirements 面板進(jìn)行要求管理。可以將已放置的要求,實(shí)時(shí)提供給對(duì)文檔擁有共享訪問(wèn)權(quán)限的合作用戶,并將其保存到獨(dú)立于項(xiàng)目的Workspace,而不以任何方式更改其組成文檔。

此功能處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用了EDMS.Requirements選項(xiàng)時(shí)可用。

如需了解更多信息,請(qǐng)參閱Working with Requirements頁(yè)面。

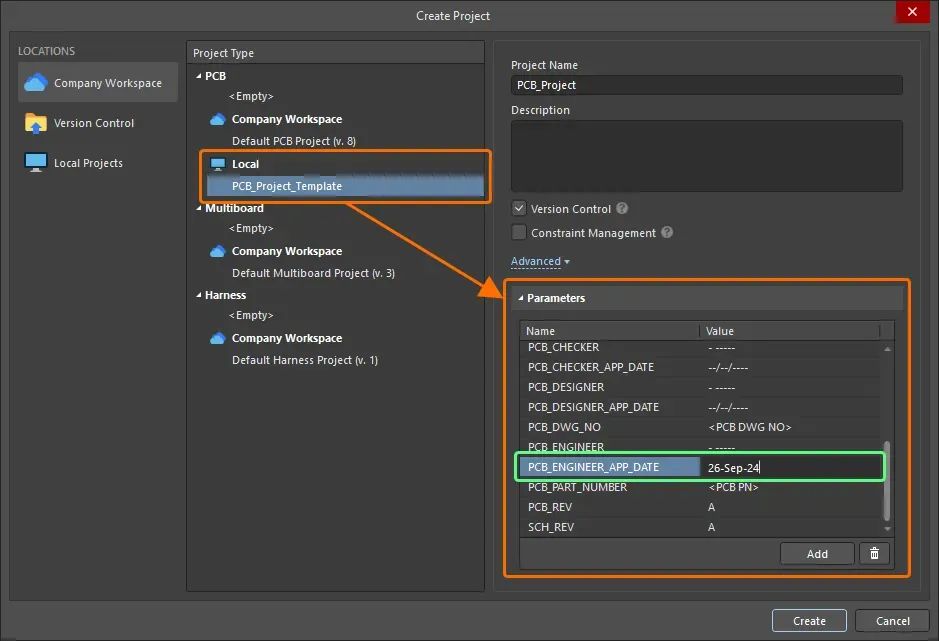

從本地模板中更改項(xiàng)目參數(shù)的功能

在使用Create Project對(duì)話框(File ? New ? Project)創(chuàng)建新項(xiàng)目時(shí),現(xiàn)在可以更改或刪除選定的本地項(xiàng)目模板的參數(shù)(名稱和/或值)。

如需了解更多信息,請(qǐng)參閱Creating Projects and Documents頁(yè)面。

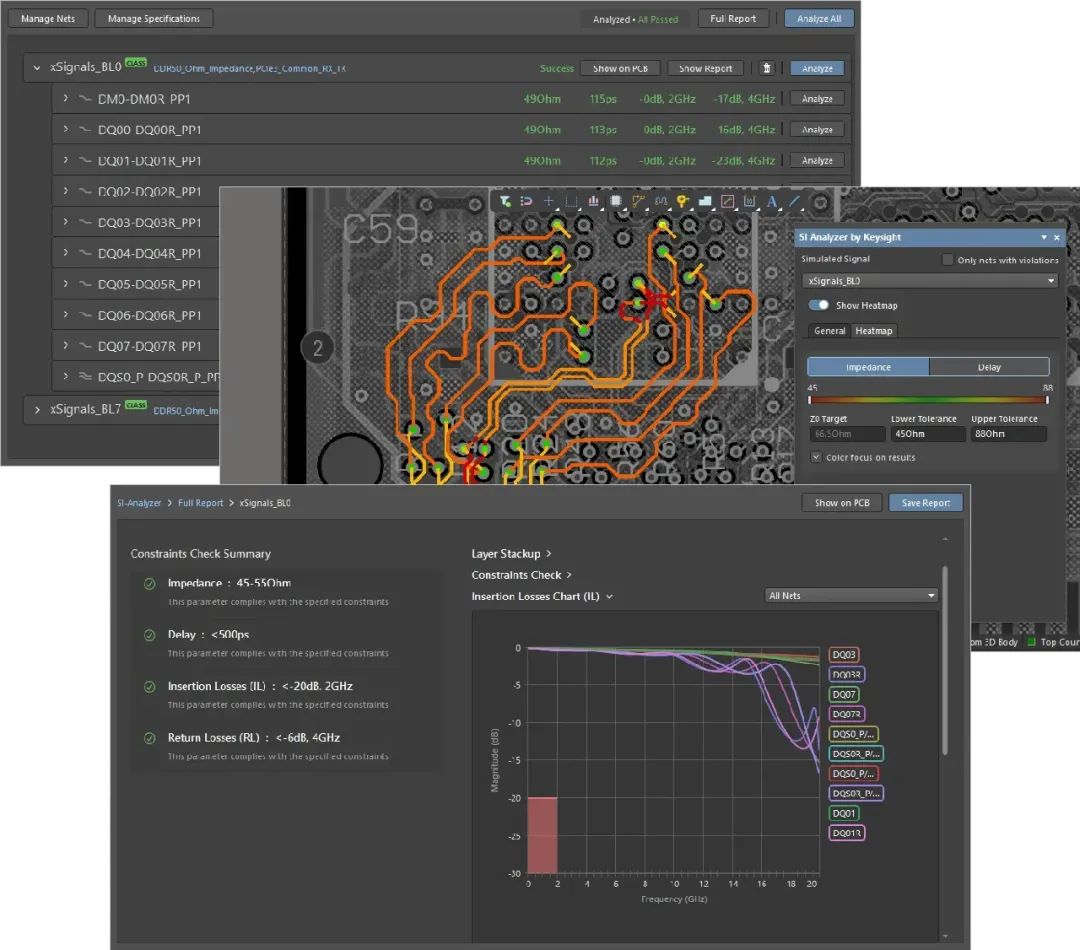

SI Analyzer by Keysight(開放測(cè)試階段)

越來(lái)越多的現(xiàn)代電子設(shè)備采用了高速PCB設(shè)計(jì),而信號(hào)速度亦隨著技術(shù)的發(fā)展而不斷提升(DDR6為17 GHz,而QSFP++則為400 Gbps)。因此,確保信號(hào)完整性(SI)成為高速設(shè)計(jì)中的一個(gè)關(guān)鍵步驟。如果無(wú)法滿足接口開發(fā)人員的要求,則很可能會(huì)在后續(xù)設(shè)計(jì)階段引起制造和性能問(wèn)題。

為了向PCB設(shè)計(jì)人員提供信號(hào)完整性分析工具,我們現(xiàn)在推出了一種新的解決方案 – SI Analyzer by Keysight。Keysight SI Analyzer將作為軟件擴(kuò)展提供,并且可以直接在Altium Designer環(huán)境中使用,以確保能夠在完成布局后針對(duì)最重要的高速設(shè)計(jì)參數(shù)進(jìn)行一系列的SI檢查:

Impedance

Delay

Insertion Losses (IL)

Return Losses (RL)

此功能處于Open Beta階段,且僅在安裝了SI Analyzer by Keysight擴(kuò)展時(shí)可用。只要持有有效的Altium Designer許可證,即可創(chuàng)建新的分析文檔,添加/配置網(wǎng)絡(luò)以進(jìn)行分析,以及查看現(xiàn)有SI分析結(jié)果和生成SI分析報(bào)告。如需進(jìn)行新的SI分析,則需要獲取有效的Signal Analyzer by Keysight許可證。如果在運(yùn)行新的SI分析時(shí)尚未獲取Signal Analyzer by Keysight許可證,則可以使用打開的對(duì)話框申請(qǐng)14天免費(fèi)試用。 如需了解更多信息,請(qǐng)參閱SI Analyzer by Keysight頁(yè)面。

Altium Designer 24.10中完全公開的功能

以下功能現(xiàn)已在本次發(fā)布中正式公開:

焊盤孔間距檢查改進(jìn) – 自24.1版開始提供

封裝鏡像阻止 – 自24.5版開始提供

更多版本發(fā)布說(shuō)明

-

原理圖

+關(guān)注

關(guān)注

1300文章

6356瀏覽量

234816 -

altium

+關(guān)注

關(guān)注

47文章

949瀏覽量

118211 -

元件

+關(guān)注

關(guān)注

4文章

942瀏覽量

36753 -

Designer

+關(guān)注

關(guān)注

0文章

122瀏覽量

35829

原文標(biāo)題:Altium Designer 24.10.1 版本發(fā)布,新功能說(shuō)明

文章出處:【微信號(hào):AltiumChina,微信公眾號(hào):Altium】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Altium Designer 24.7.2版本新功能圖解說(shuō)明

Altium Designer 24.10.1版本新功能解析

Altium Designer 24.10.1版本新功能解析

評(píng)論