其實工作了這么久后,真的發現現在的工程師太依賴軟件庫了,做一個成熟的項目可以,稍微新一點,沒做過的,沒現成的代碼的項目,就不敢接了。一來是風險控制,二來還是技術太菜!

其實技術很簡單,超級簡單,大學做實驗時候,在開發板,做什么紅外報警,32位密碼鎖,還有無繩電話等,拉一套學長的代碼,調試一下,燒到板子,就OK了。用帶我的張老師的話說“加個殼,你們就可以注冊個商標創業開公司了。”

以前覺得技術NB,銷售LJ。現在回頭一看,銷售才是王道啊,技術什么的,拉個虎皮就能出產品了,慢慢升級質量也會上去。只要有銷路,土豪做朋友。

吐槽完了,還是出點干貨吧。現在的COMS sensor 完全不顧人眼最適的800W像素,1200W,1300W不停向上搞。那么問題來了:這么高像素的IC,要達到30幀/S,這傳輸速率要多給力啊,所以,mipi傳輸協議打敗了串口,并口的傳輸方式,成為現在的新寵。

下面就介紹一下mipi協議及一些常規故障排除。不要問我為什么懂,畢竟COMS芯片FAE的工作不是白做的,現在呆過的第一家公司已經上市了,祝福啊。對于在上市前夕離開開公司的事情,我真是一點不后悔啊。%>_<%?

MIPI ——Mobile industry process interface多家移動開發或者應用商共同籌劃接口標準聯盟節約成本,加快產品開發速度內容豐富,顯示、照相機、電源管理、射頻、存儲接口等等

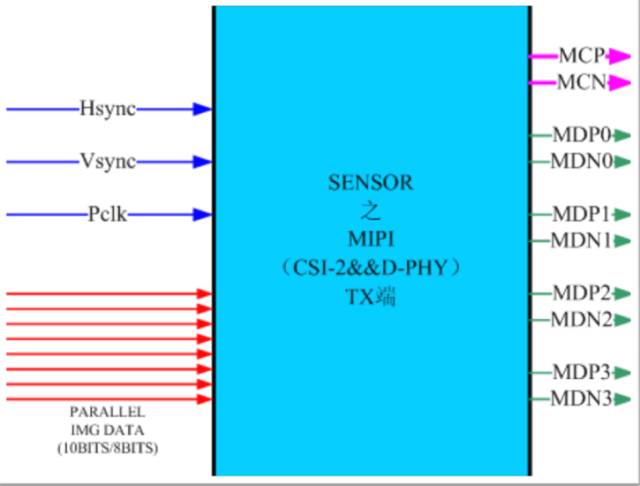

CIS(cmos image sensor)中僅用到了mipi協議中的csi-2(camera serial interface二代,標識生成要求)和D-phy(物理層,輸出通道要求)

Camera端做transmitter,平臺端做receiver簡而言之 mipi的作用就是:1.數據并行轉換成串行;2.功能復用,節約傳輸線;3.相對提高傳輸品質和速度;4.增加傳輸距離;5.適用新的平臺需求;

為什么mipi那么NB,下面對比一下就照了。

并口需要Vsync:幀同步信號Hsync:行同步信號和8條數據線,但這10根線,mipi只需要5根。所以,我行,我來!

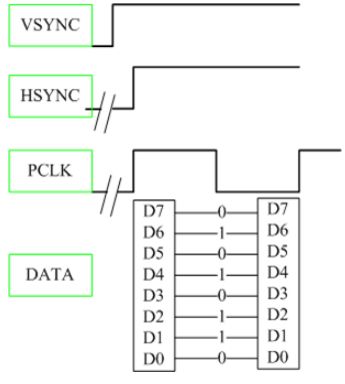

Clock和 data中體現差分即低位先出,故如此表示,差分信號P高N低表1,P低N高表0.現在對mipi大概有點小小的概念了。再給你看看她的照片,保證你喜歡。MIPI 輸出長什么樣?

當當當當~~

幀頭標識、幀尾標識(分別由vsync上升下降沿生成)行頭標識、行尾標識(分別由hsync上升下降沿生成)有效數據長包。包含行標識,所以可以省略line_sync短包相對于并口傳輸,即是將vsync、hsync與數據共通道復用傳輸。

總之一句話,能用軟件解決的一定不要動硬件,能動手的一定不要動嘴。人生哲理。什么?不要看PS過的照片!好吧,下面發個素顏照。

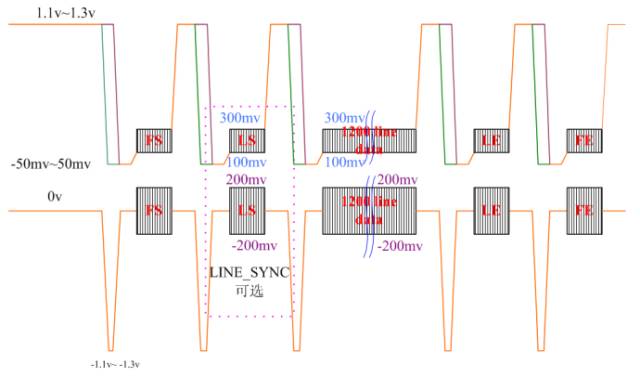

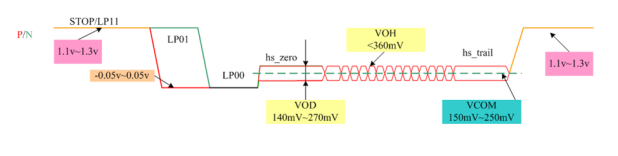

是不是美如畫。而mipi的信號符合其通信協議,規定其起始電壓在1.1~1.3V,等等,如下圖(我比較懶,不服來辯)。這是其電氣要求。

然后軟件方面,如下圖:

字節(byte)為基本傳輸單元,每個byte中有8位(bit)Sync dyte:用來同步數據開始,告知接下來為有效數據DATA TYPE:該包傳輸的是什么格式的數據YUV422(1E)/RAW8(2A)/RAW10(2B)WC(16bits)= PAYLOAD中的byte數量(即輸出窗口的1行中有多少個字節,也即列數。注意raw10為列數的1.25倍,raw12為列數的1.5倍)ECC:校驗datatype和wc是否出錯Payload=image dataCSC:PAYLOAD數據傳輸校驗*由于插入了許多數據標識,所以會影響hb或者vb的最小值MIPI DPHY 終端概念

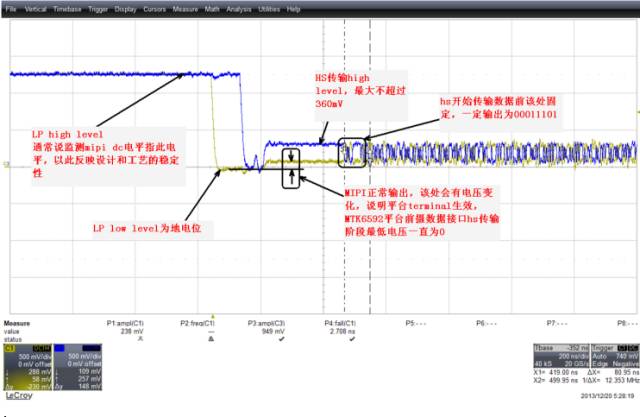

mipi的信號線是一對差分線,理論上可以高電平傳一個數據,低電平也傳一個,速度又快,功耗又小。很多時候,平臺端的mipi時序和Sensor端如果不匹配,就會出問題。硬件問題的話,就亮信號!

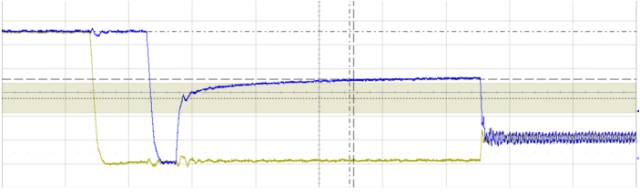

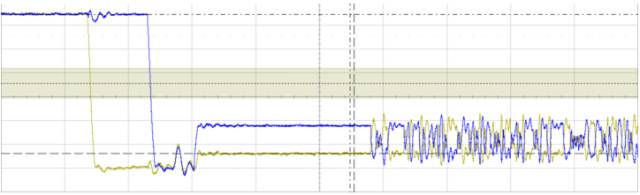

Term未連接情況信號時這樣滴。正常的是這樣滴:

Sensor輸出在設計時已經考慮,應用時主要是FPC或者PCB走線影響通常要求:差分對內兩線等長,盡量少折線,方向一致;差分對間地線走地,減小串擾;線上過孔最少;至少一側有鋪地;線長最長不超過20cm;盡量遠離天線;目的:阻抗匹配、阻抗連續,減少信號損失,獲得較高的信號完整性;減少信號間耦合,保證信號完整性;減少與其他射頻信號的相互作用,保證各信號的質量;Settle count主要是hs_prepare+hs_zero時間與其匹配;通常設定T_settle count為T_(hs_prepare+hs_zero)/2;是平臺設定參數,通常不改默認值,與pclk頻率有關;

不匹配會引起的問題:卡頓;不出圖;不規則滾屏、拍照分屏

調節方法:增大或者減小T_hs_prepare、hs_zero,參數最小值為1,有時需要調的很不可思議才可行,這是需要配成manual模式。

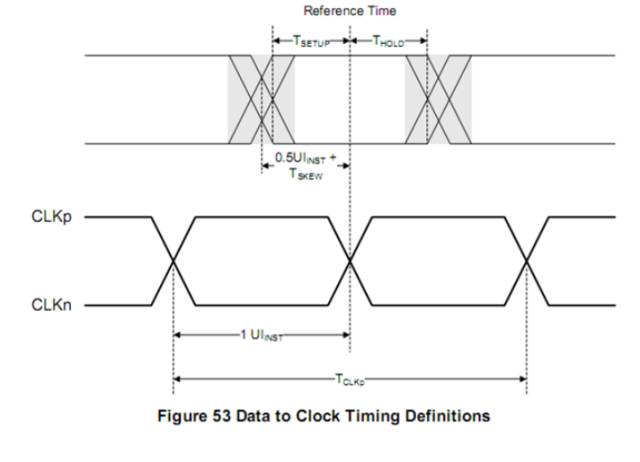

DDR采樣,即在時鐘的上升和下降沿均采集數據,保證高速傳輸又可以有效降低時鐘頻率,要求時鐘和數據相位為正交關系。實際中因為負載差異,會限制時鐘的建立速度,同時數據的不規律輸出(不是確定的輸出序列),所以對setup或者hold時間要求不同。可能造成誤碼,引起麻點,嚴重時會丟行。

數據傳輸速率,單位為bps(bit per second)

mipi_data=pclk_tot*10(raw10)=pclk_tot*8 (raw8)

pclk_tot=數字輸出并行時鐘pclk * 數字通道數Mmipi N通道,每通道數據率=mipi_data/NMipi時鐘速度=每通道數據率/2= mipi_data/4

-

嵌入式開發

+關注

關注

18文章

1035瀏覽量

47660 -

MIPI

+關注

關注

11文章

312瀏覽量

48730

原文標題:嵌入式開發之mipi協議學習

文章出處:【微信號:qrsworld,微信公眾號:嵌入式單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

焊接機器人常見故障及排查

BGA封裝常見故障及解決方法

航空插頭常見故障的解決方法及拆卸技巧

mipi傳輸協議常見故障排查及解決

mipi傳輸協議常見故障排查及解決

評論