Hi,根據之前大家的反饋,這一章就來簡單介紹一下CDC也就是跨時鐘域可能存在的一些問題以及基本的跨時鐘域處理方法。

跨時鐘域的問題主要存在于異步時鐘信號之間。首先同步時鐘和異步時鐘的主要區別在于同步時鐘是同源的,有一個確定的相位關系,在綜合約束的保證下同步時鐘路徑可以盡可能的去滿足setup/hold的要求。同步時鐘在CDC中屬于同一個時鐘域。

而異步時鐘來自不同的晶振源,他們之間沒有一個確定的相位關系,也就是說如果一個條路徑的起點和終點寄存器由異步時鐘驅動,沒有任何辦法來保證信號在何時會到達終點寄存器,這樣可能引發一系列的問題,比如亞穩態。我們知道對于同步時鐘信號,在綜合工具以及后端工具中有時鐘約束,可以解決同步時鐘路徑的setup/hold,而對于異步信號,在綜合以及后端中都設為false path,也就是說沒有辦法從工具的角度進行解決。在這種情況下,就需要從設計層面來解決這個問題,避免這些路徑的違例對電路功能造成影響。

Synopsys提供的Spyglass工具可以用于檢測系統中存在的CDC路徑,并且分析其可能產生的問題,在綜合之前進行CDC的檢測以及相關設計的修改,可以最大程度地避免這些問題。下面我們來看下幾種CDC可能造成的問題以及相應的檢測和簡單的解決方案。

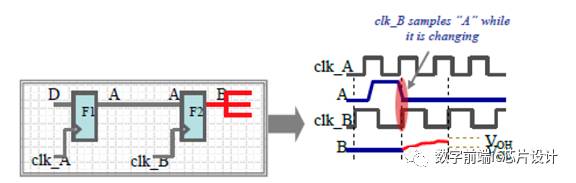

1.metastability

亞穩態是跨時鐘域中最主要的一個問題,因為在一條時鐘路徑中我們無法預知信號會在何時到達終點寄存器,那么有可能信號就會造成setup/hold的違例

上圖所示的例子是一個很典型的metastability 問題。由于A信號在F2寄存器的setup違例,造成的亞穩態會在F2的下接負載中進行傳播。

對于亞穩態問題,針對具體信號的功能,一般有不同的處理。

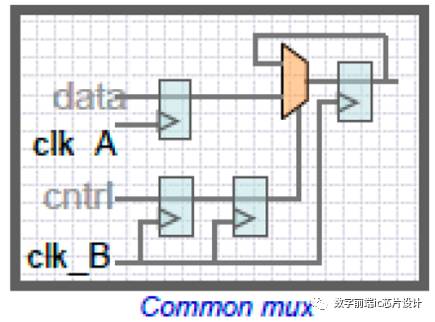

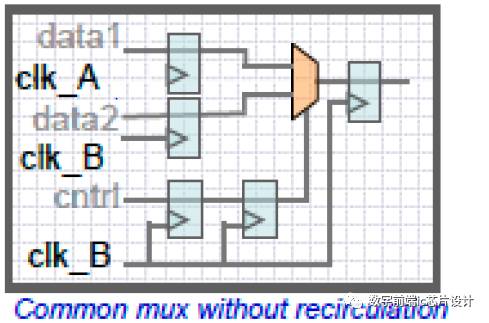

對于多bit的data信號,我們可以使用使能技術,也就是通過一個使能信號來判斷data信號是否已經穩定,當使能信號有效的時候說明data處于穩定狀態,在這種情況下終點寄存器才對信號進行采樣,可以保證沒有setup/hold違例。而使能信號一般使用double FF的方法來進行同步。下面是一些簡單的data同步電路的例子:

在該電路中Cntrl信號通過兩級寄存器同步,通過mux來控制data的采樣,注意到這里使用的是recirculate的mux

當然也可以不適用recirculate的mux,mux的另一個輸入同樣來自終點時鐘域。

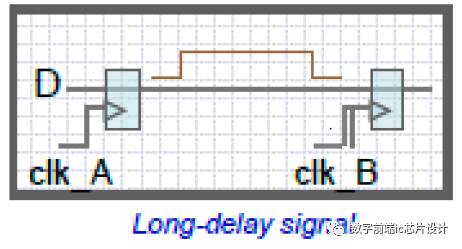

此外還可以通過long-delay,也就是給信號長的延時來保證信號能在指定的時間到達。

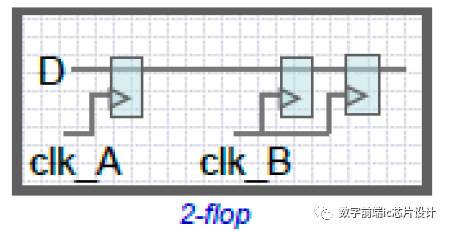

如果是控制信號,我們可以直接使用double FF的方法,也就是多級寄存器同步的方法來進行同步。這是因為控制信號位數較少,不需要額外使用使能信號資源。

上圖是個最基本的兩級flop的同步器,原理很簡單,我們默認亞穩態會在一個時鐘周期之內解決,因此從第一級flop輸入的亞穩態到第二級flop就穩定了。因為這是一個1-bit的信號,所以如果第一個時鐘亞穩態穩定的值不是我們預估的值,比如1->0的跳變,亞穩態最后結果是1,那么0的穩定值也會在下一個周期到達第二級flop。

以上是一些最基本的信號同步器,根據具體design的不同,可以設置不同的同步邏輯,但同步邏輯的基本思路都類似,通過控制信號來保證來自時鐘源A的信號在穩定的情況下才被來自時鐘源B的終點寄存器采樣,而控制信號因為多為單bit,一般都使用兩級寄存器來采樣。

2. fast-slow CDC

除了亞穩態之外,如果信號起始時鐘源頻率比終點時鐘源高很多,那么可能就會導致信號的丟失。

在上圖的例子中,雖然A信號到B信號之間使用了同步器,但是如果時鐘域A的頻率過高,很容易造成信號的丟失。對此,我們需要使用額外的結構來保證A信號不丟失。

常用的方法有兩種,一是使用定制化的電路,使A->B之間有至少一個B周期的延時。

另一個是使用控制信號,控制信號的信息來自B時鐘域的反饋信號,當B成功完成一次有效采樣之后,才讓A讀取下一個信號。針對不同的具體電路有不同的設計方案,這里就不一一列出。

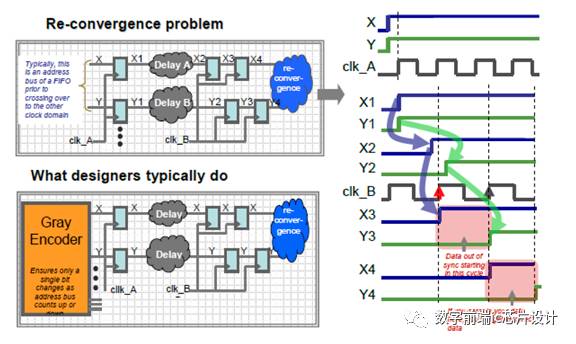

3. multi-bit data correlation

對于多bit的data信號,如果采用每個bit分別同步的方法,由于每個bit到達同步器的延時不同,可能造成采樣時刻多bit的信號corelation有問題。

在上圖所示例子中,由于每個bit到達2-FFs同步器的時間不同,如果這幾位bit同時跳變,可能在第一拍采樣的時候采到的不是我們想要的結果。

對此,我們可以使用格雷碼,來確保對于多bit信號每次只有一位bit發生了跳變。另外可以使用使能信號,在所有bit的信號都穩定之后,才進行同步采樣。

4. FIFO

我們可以使用FIFO來完成跨時鐘域的信號轉換,下圖是一個簡單的FIFO例子

FIFO會占用比較多的資源,但對于跨時鐘域問題能夠有很好的保證。對于FIFO,我們可以使用DesignWare中已經搭建好的標準單元,這是經過驗證的可綜合的FIFO。在Spyglass中,我們也可以對FIFO的正確性進行驗證。

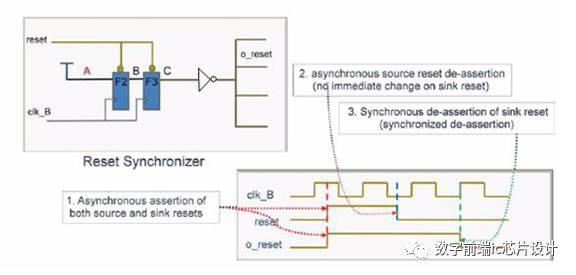

5.reset synchronization

復位信號是一個系統中最重要的幾種信號。復位信號的同步也是系統中很關鍵的一個環節。對于復位信號的同步,我們有一個經典的標準設計方案

從上圖中我們可以看到,我們采用了異步復位同步釋放地方法。這里并不是直接將復位信號進行兩級同步。

以上就是CDC的一些基本問題和經典的解決方案,針對不同設計我們可以有不同的解決方法,而通過Spyglass,我們可以在綜合之前對CDC的問題進行一個完整的檢測。希望以上對大家的設計有所幫助。

-

CDC

+關注

關注

0文章

57瀏覽量

17836

原文標題:關于跨時鐘域的分析和簡單的解決方案

文章出處:【微信號:ic_frontend,微信公眾號:數字前端ic芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CDC509/516/2509/2510/2516的高速時鐘分配設計技術

介紹一個IC設計錯誤案例:可讀debug寄存器錯誤跨時鐘

cdc路徑方案幫您解決跨時鐘域難題

cdc路徑方案幫您解決跨時鐘域難題

評論