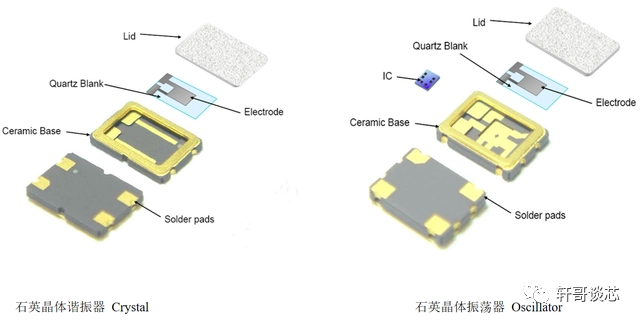

1.晶振與晶體的區別

1) 晶振是有源晶振的簡稱,又叫振蕩器。英文名稱是oscillator。晶體則是無源晶振的簡稱,也叫諧振器。英文名稱是crystal.

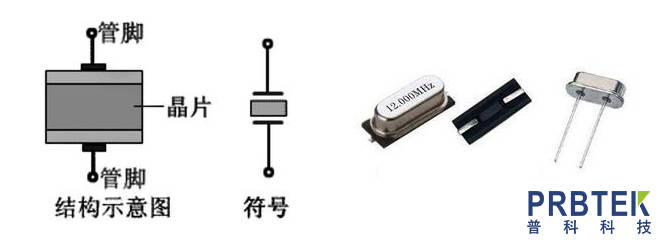

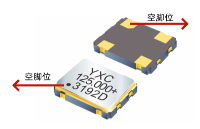

2) 無源晶振(晶體)一般是直插兩個腳的無極性元件,需要借助時鐘電路才能產生振蕩信號。常見的有49U、49S封裝。3) 有源晶振(晶振)一般是表貼四個腳的封裝,內部有時鐘電路,只需供電便可產生振蕩信號。一般分7050、5032、3225、2520幾種封裝形式。

2.MEMS硅晶振與石英晶振區別

MEMS硅晶振采用硅為原材料,采用先進的半導體工藝制造而成。因此在高性能與低成本方面,有明顯于石英的優勢,具體表現在以下方面:

1) 全自動化半導體工藝(芯片級),無氣密性問題,永不停振。

2) 內部包含溫補電路,無溫漂,-40—85℃全溫保證。

3) 平均無故障工作時間5億小時。

4) 抗震性能25倍于石英振蕩器。

5) 支持1-800MHZ任一頻點,精確致小數點后5位輸出。

6) 支持1.8V、2.5V、2.8V、3.3V多種工作電壓匹配。

7) 支持10PPM、20PPM、25PPM、30PPM、50PPM等各種精度匹配。

8) 支持7050、5032、3225、2520所有標準尺寸封裝。

9) 標準四腳、六腳封裝,無需任何設計改動,直接替代石英振蕩器。

10) 支持差分輸出、單端輸出、壓控(VCXO)、溫補(TCXO)等產品種類。

11) 300%的市場增長率,三年內有望替代80%以上的石英振蕩器市場。

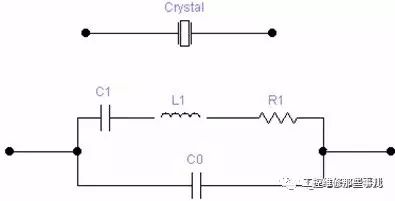

3.晶體諧振器的等效電路

上圖是一個在諧振頻率附近有與晶體諧振器具有相同阻抗特性的簡化電路。其中:C1為動態電容也稱等效串聯電容;L1為動態電感也稱等效串聯電感;R1為動態電阻也稱等效串聯電阻;C0為靜態電容也稱等效并聯電容。這個等效電路中有兩個最有用的零相位頻率,其中一個是諧振頻率(Fr),另一個是反諧振頻率(Fa)。當晶體元件實際應用于振蕩電路中時,它一般還會與一負載電容相聯接,共同作用使晶體工作于Fr和Fa之間的某個頻率,這個頻率由振蕩電路的相位和有效電抗確定,通過改變電路的電抗條件,就可以在有限的范圍內調節晶體頻率。

4.關鍵參數

4.1 標稱頻率指晶體元件規范中所指定的頻率,也即用戶在電路設計和元件選購時所希望的理想工作頻率。

4.2 調整頻差基準溫度時,工作頻率相對于標稱頻率的最大允許偏離。常用ppm(1/106)表示。

4.3 溫度頻差在整個溫度范圍內工作頻率相對于基準溫度時工作頻率的允許偏離。常用ppm(1/106)表示。

4.4 老化率指在規定條件下,由于時間所引起的頻率漂移。這一指標對精密晶體是必要的,但它“沒有明確的試驗條件,而是由制造商通過對所有產品有計劃抽驗進行連續監督的,某些晶體元件可能比規定的水平要差,這是允許的”(根據IEC的公告)。老化問題的最好解決方法只能靠制造商和用戶之間的密切協商。

4.5 諧振電阻(Rr)指晶體元件在諧振頻率處的等效電阻,當不考慮C0的作用,也近似等于所謂晶體的動態電阻R1或稱等效串聯電阻(ESR)。這個參數控制著晶體元件的品質因數,還決定所應用電路中的晶體振蕩電平,因而影響晶體的穩定性以致是否可以理想的起振。所以它是晶體元件的一個重要指標參數。一般的,對于一給定頻率,選用的晶體盒越小,ESR的平均值可能就越高;絕大多數情況,在制造過程中并不能預計具體某個晶體元件的電阻值,而只能保證電阻將低于規范中所給的最大值。

4.6 負載諧振電阻(RL)指晶體元件與規定外部電容相串聯,在負載諧振頻率FL時的電阻。對一給定晶體元體,其負載諧振電阻值取決于和該元件一起工作的負載電容值,串上負載電容后的諧振電阻,總是大于晶體元件本身的諧振電阻。

4.7 負載電容(CL)與晶體元件一起決定負載諧振頻率FL的有效外界電容。晶體元件規范中的CL是一個測試條件也是一個使用條件,這個值可在用戶具體使用時根據情況作適當調整,來微調FL的實際工作頻率(也即晶體的制造公差可調整)。但它有一個合適值,否則會給振蕩電路帶來惡化,其值通常采用10pF、15pF 、20pF、30pF、50pF、∝等,其中當CL標為∝時表示其應用在串聯諧振型電路中,不要再加負載電容,并且工作頻率就是晶體的(串聯)諧振頻率Fr。用戶應當注意,對于某些晶體(包括不封裝的振子應用),在某一生產規范既定的負載電容下(特別是小負載電容時),±0.5pF的電路實際電容的偏差就能產生±10×10-6的頻率誤差。因此,負載電容是一個非常重要的訂貨規范指標。

4.8 靜態電容(C0)等效電路靜態臂里的電容。它的大小主要取決于電極面積、晶片厚度和晶片加工工藝。

4.9 動態電容(C1)等效電路中動態臂里的電容。它的大小主要取決于電極面積,另外還和晶片平行度、微調量的大小有關。

4.10 動態電感(L1)等效電路中動態臂里的電感。動態電感與動態電容是一對相關量。

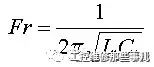

4.11 諧振頻率(Fr)指在規定條件下,晶體元件電氣阻抗為電阻性的兩個頻率中較低的一個頻率。根據等效電路,當不考慮C0的作用,Fr由C1和L1決定,近似等于所謂串聯(支路)諧振頻率(Fs)。這一頻率是晶體的自然諧振頻率,它在高穩晶振的設計中,是作為使晶振穩定工作于標稱頻率、確定頻率調整范圍、設置頻率微調裝置等要求時的設計參數。

4.12 負載諧振頻率(FL)指在規定條件下,晶體元件與一負載電容串聯或并聯,其組合阻抗呈現為電阻性時兩個頻率中的一個頻率。在串聯負載電容時,FL是兩個頻率中較低的那個頻率;在并聯負載電容時,FL則是其中較高的那個頻率。對于某一給定的負載電容值(CL),就實際效果,這兩個頻率是相同的;而且這一頻率是晶體的絕大多數應用時,在電路中所表現的實際頻率,也是制造廠商為滿足用戶對產品符合標稱頻率要求的測試指標參數。

4.13 品質因數(Q)品質因數又稱機械Q值,它是反映諧振器性能好壞的重要參數,它與L1和C1有如下關系:Q=wL1/R1=1/wR1C1 如上式,R1越大,Q值越低,功率耗散越大,而且還會導致頻率不穩定。反之Q值越高,頻率越穩定。

4.14 激勵電平(Level of drive)是一種用耗散功率表示的,施加于晶體元件的激勵條件的量度。所有晶體元件的頻率和電阻都在一定程度上隨激勵電平的變化而變化,這稱為激勵電平相關性(DLD),因此訂貨規范中的激勵電平須是晶體實際應用電路中的激勵電平。正因為晶體元件固有的激勵電平相關性的特性,用戶在振蕩電路設計和晶體使用時,必須注意和保證不出現激勵電平過低而起振不良或過度激勵頻率異常的現象。

4.15 激勵電平相關性(DLD)由于壓電效應,激勵電平強迫諧振子產生機械振蕩,在這個過程中,加速度功轉化為動能和彈性能,功耗轉化為熱。后者的轉換是由于石英諧振子的內部和外部的摩擦所造成的。摩擦損耗與振動質點的速度有關,當震蕩不再是線性的,或當石英振子內部或其表面及安裝點的拉伸或應變、位移或加速度達到臨界時,摩擦損耗將增加。因而引起頻率和電阻的變化。

加工過程中造成DLD不良的主要原因如下,其結果可能是不能起振:

1) 諧振子表面存在微粒污染。主要產生原因為生產環境不潔凈或非法接觸晶片表面;

2) 諧振子的機械損傷。主要產生原因為研磨過程中產生的劃痕。

3) 電極中存在微粒或銀球。主要產生原因為真空室不潔凈和鍍膜速率不合適。

4) 裝架是電極接觸不良;

5) 支架、電極和石英片之間存在機械應力。

4.16 DLD2(單位:歐姆)不同激勵電平下的負載諧振電阻的最大值與最小值之間的差值。(如:從0.1uw~200uw,總共20步)。

4.17 RLD2(單位:歐姆)不同激勵電平下的負載諧振電阻的平均值<與諧振電阻Rr的值比較接近,但要大一些>。(如:從0.1uw~200uw,總共20步)。

4.18 寄生響應所有晶體元件除了主響應(需要的頻率)之外,還有其它的頻率響應。減弱寄生響應的辦法是改變晶片的幾何尺寸、電極,以及晶片加工工藝,但是同時會改變晶體的動、靜態參數。

寄生響應的測量

1) SPDB 用DB表示Fr的幅度與最大寄生幅度的差值;

2) SPUR 在最大寄生處的電阻;

3) SPFR 最小電阻寄生與諧振頻率的距離,用Hz或ppm表示。

5. 晶體振蕩器的分類

5.1 Package石英振蕩器(SPXO)不施以溫度控制及溫度補償的石英振蕩器。頻率溫度特性依靠石英振蕩晶體本身的穩定性。

5.2 溫度補償石英振蕩器(TCXO)附加溫度補償回路,減少其頻率因周圍溫度變動而變化之石英振蕩器。

5.3 電壓控制石英振蕩器(VCXO)控制外來的電壓,使輸出頻率能夠變化或調變的石英振蕩器。

5.4 恒溫槽式石英振蕩器(OCXO)以恒溫槽保持石英振蕩器或石英振蕩晶體在一定溫度,控制其輸出頻率在周圍溫度下也能保持極小變化量之石英振蕩器。除了以上四種振蕩器外,隨著PLL、Digital、Memory技術的應用,其他功能的多元化石英振蕩器也快速增加。

-

晶體

+關注

關注

2文章

1369瀏覽量

35516 -

晶振

+關注

關注

34文章

2899瀏覽量

68221

原文標題:晶振與晶體的參數詳解

文章出處:【微信號:pcb_repaired,微信公眾號:工控維修那些事兒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

多方面了解晶體和晶振的區別(定義 參數 電路 分類)

多方面了解晶體和晶振的區別(定義 參數 電路 分類)

評論