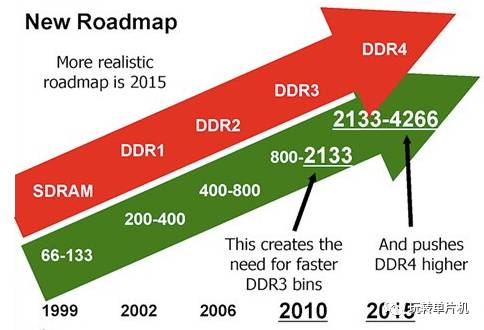

(Double Data Rate Fourth SDRAM):DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達2133~3200MT/s。DDR4 新增了4 個Bank Group 數據組的設計,各個Bank Group具備獨立啟動操作讀、寫等動作特性,Bank Group 數據組可套用多任務的觀念來想象,亦可解釋為DDR4 在同一頻率工作周期內,至多可以處理4 筆數據,效率明顯好過于DDR3。 另外DDR4增加了DBI(Data Bus Inversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,讓DDR4內存在更快速與更省電的同時亦能夠增強信號的完整性、改善數據傳輸及儲存的可靠性。

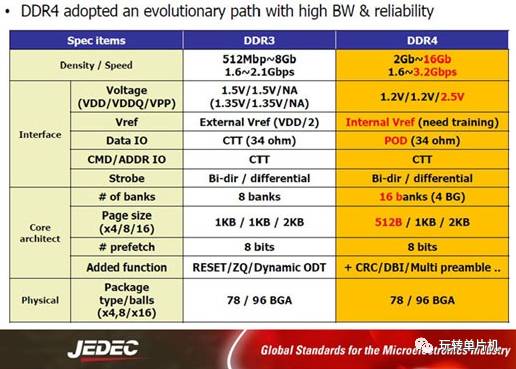

以下兩張圖可以清晰對比DDR3以及DDR4的參數差異:

|

|

POD 和SSTL的比較

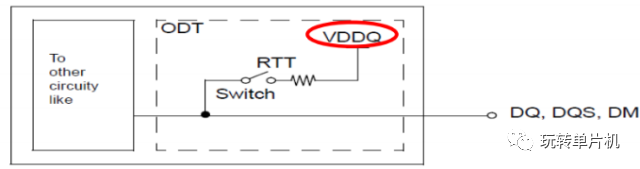

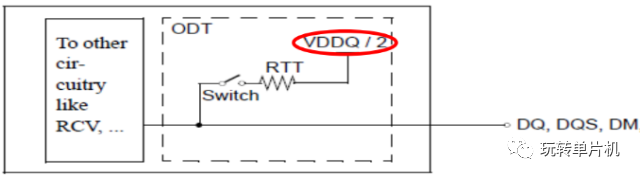

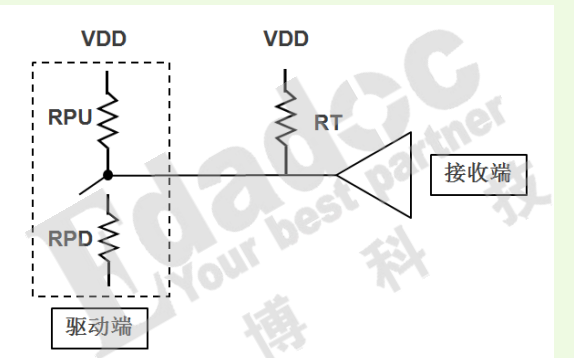

POD作為DDR4新的驅動標準,最大的區別在于接收端的終端電壓等于VDDQ,而DDR3所采用的SSTL接收端的終端電壓為VDDQ/2。這樣做可以降低寄生引腳電容和I/O終端功耗,并且即使在VDD電壓降低的情況下也能穩定工作。其等效電路如圖1(DDR4), 圖2(DDR3)。

圖1 POD ((Pseudo Open Drain)

圖2 SSTL(Stub Series Terminated Logic)

這樣修改的優點是:

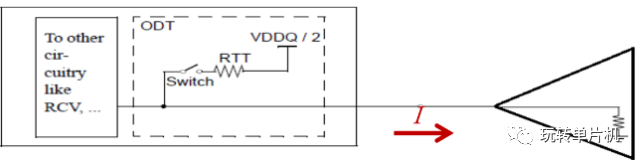

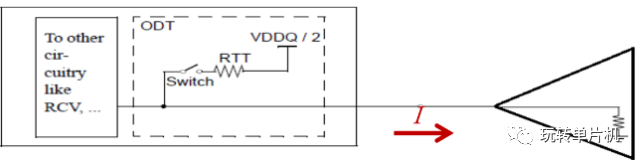

可以看出,當DRAM在低電平的狀態時,SSTL和POD都有電流流動

圖3 DDR4

圖4 DDR3

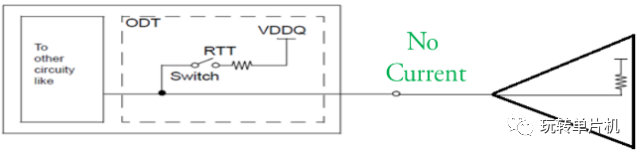

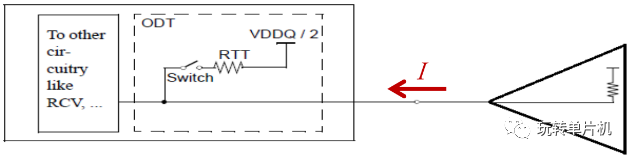

而當DRAM為高電平的狀態時,SSTL繼續有電流流動,而POD由于兩端電壓相等,所以沒有電流流動。這也是DDR4更省電的原因

圖5 DDR4

圖6 DDR3

BG設計原因

到了DDR4的時代,JESD組織認為,數據預取的增加變得更為困難,所以推出了Bank Group的設計。

Bank Group架構是什么樣的,有何優勢呢?具體來說就是每個Bank Group可以獨立讀寫數據,這樣一來內部的數據吞吐量大幅度提升,可以同時讀取大量的數據,內存的等效頻率在這種設置下也得到巨大的提升。DDR4架構上采用了8n預取的Bank Group分組,包括使用兩個或者四個可選擇的Bank Group分組,這將使得DDR4內存的每個Bank Group分組都有獨立的激活、讀取、寫入和刷新操作,從而改進內存的整體效率和帶寬。如此一來如果內存內部設計了兩個獨立的Bank Group,相當于每次操作16bit的數據,變相地將內存預取值提高到了16n;如果是四個獨立的Bank Group,則變相的預取值提高到了32n。

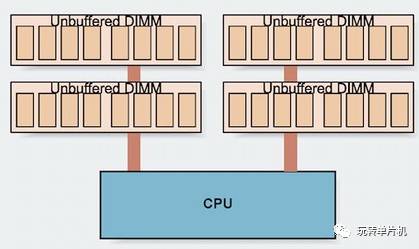

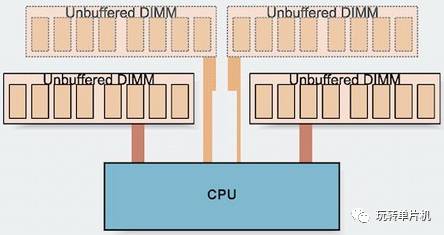

| DDR3 Multi-drop bus | DDR4 Point to Point |

|

|

在DDR3內存上,內存和內存控制器之間的連接采用是通過多點分支總線來實現。這種總線允許在一個接口上掛接許多同樣規格的芯片。我們都知道目前主板上往往為雙通道設計四根內存插槽,但每個通道在物理結構上只允許擴展更大容量。這種設計的特點就是當數據傳輸量一旦超過通道的承載能力,無論你怎么增加內存容量,性能都不見的提升多少。這種設計就好比在一條主管道可以有多個注水管,但受制于主管道的大小,即便你可以增加注水管來提升容量,但總的送水率并沒有提升。因此在這種情況下可能2GB增加到4GB你會感覺性能提升明顯,但是再繼續盲目增加容量并沒有什么意義了,所以多點分支總線的好處是擴展內存更容易,但卻浪費了內存的位寬。(通過這個理解帶寬)

數據總線倒置 (DBI)

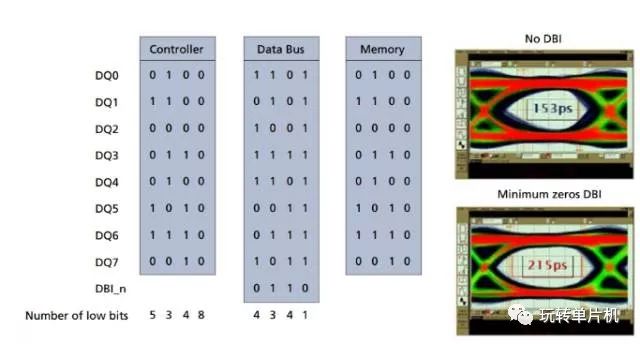

如上面描述,根據POD的特性,當數據為高電平時,沒有電流流動,所以降低DDR4功耗的一個方法就是讓高電平盡可能多,這就是DBI技術的核心。舉例來說,如果在一組8-bit的信號中,有至少5-bit是低電平的話,那么對所有的信號進行反轉,就有至少5-bit信號是高電平了。DBI信號變為低表示所有信號已經翻轉過(DBI信號為高表示原數據沒有翻轉)。這種情況下,一組9根信號(8個DQ信號和1個DBI信號)中,至少有五個狀態為高,從而有效降低功耗。

圖7 DBI Example

參考電壓Vref

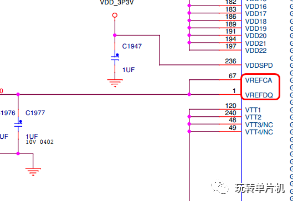

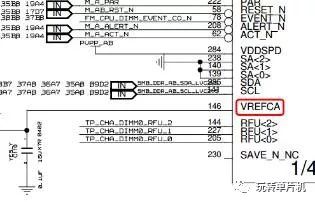

眾所周知,DDR信號一般通過比較輸入信號和另外一個參考信號(Vref)來決定信號為高或者低,然而在DDR4中,一個Vref卻不見了,先來看看下面兩種設計,可以看出來,在DDR4的設計中,VREFCA和DDR3相同,使用外置的分壓電阻或者電源控制芯片來產生,然而VREFDQ在設計中卻沒有了,改為由芯片內部產生,這樣既節省了設計費用,也增加了Routing空間。

圖9 DDR3設計

圖10 DDR4設計

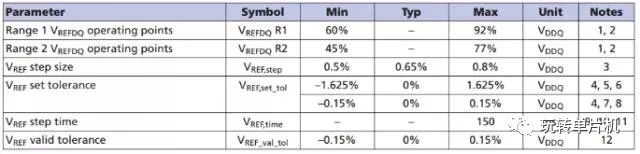

DRAM內部VREFDQ通過寄存器(MR6)來調節,主要參數有Voltage range, step size, VREF step time, VREF full step time ,如下表所示。

表4 參考電壓

每次開機的時候,DRAM Controller都會通過一系列的校準來調整DRMA端輸入數據信號的VREFDQ,優化Timing和電壓的Margin,也就是說,VREFDQ 不僅僅取決于VDD, 而且和傳輸線特性,接收端芯片特性都會有關系,所以每次Power Up的時候,VREFDQ的值都可能會有差異。

-

DDR3

+關注

關注

2文章

276瀏覽量

42354 -

DDR4

+關注

關注

12文章

322瀏覽量

40881 -

DBI

+關注

關注

0文章

6瀏覽量

6936

原文標題:DDR4總結純干貨分享

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR4與DDR3的不同之處 DDR4設計與仿真案例

DDR4相比DDR3的相關變更點

ddr4和ddr3內存的區別,可以通用嗎

SDRAM,DDR3,DDR2,DDR4,DDR1的區別對比及其特點分析

DDR3和DDR4的設計與仿真學習教程免費下載

DDR4相比DDR3的變更點

DDR,DDR2,DDR3,DDR4,LPDDR區別

PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用

ddr3及ddr4的差異對比

ddr3及ddr4的差異對比

評論