作者:Kevin Smith, Silicon Labs

您好,歡迎來到Timing 101秒懂時鐘系列技術文章,本系列文章為Silicon Labs(亦稱“芯科科技”)時鐘技術專家特別開辟的專欄。我們的目標是介紹和綜述應用定時組件或IC(也稱為“時鐘芯片”)方面的技術主題。時鐘芯片通過時鐘波形傳送頻率和相位信息,并且在某些情況下可以分組化定時信息。

在這篇文章中將介紹一個常見的設置測量的狀況,當最初使用抖動衰減器時,其測試結果可能是意想不到的。首先綜述一些必要的背景材料,然后展示問題及其根本原因,最后提出改進的測試設置。

簡而言之,時鐘是具有用于在同步數字系統中采樣數據的數字信號電平的周期性信號。換句話說,時鐘提供了在同步數字電路或系統中采樣和順序處理數據所需的“心跳”或節奏。它們通常但不總是在50%或近50%的占空比。

理想時鐘將提供完美的指定頻率和相位來優化此過程。然而,實際的時鐘具有定時抖動,其可以被定義為時鐘邊沿與其理想值的短期變化。關心同步數字系統的時鐘抖動的一個原因是它可以進入定時裕度,從而影響數據的可靠性和有效性。

還有一個對應于抖動的頻域:相位噪聲。相位噪聲測量時鐘的隨機短期相位波動。這表明時鐘的純度。

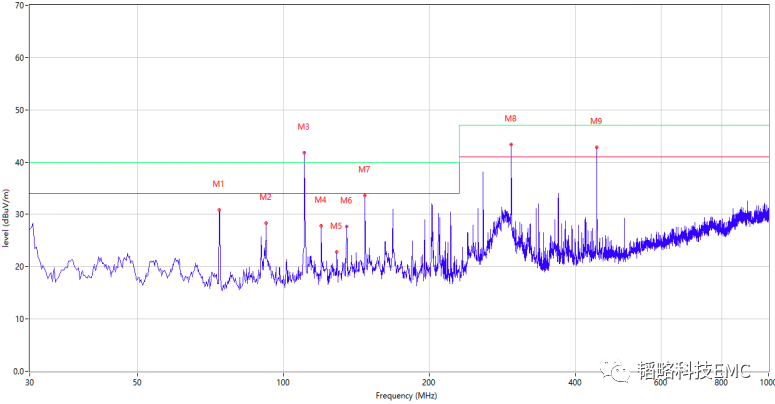

簡而言之,這里有一個L(f)的圖。顯示了在載波頻率偏移的情況下,一相調制邊帶的噪聲功率與載波功率的關系。例如,在100kHz時為-70dBc / Hz,在20MHz下為-150dBc / Hz。 dBc / Hz單位是指相對于每赫茲帶寬的載波功率的功率(dB)。相位噪聲通常使用相位噪聲分析儀或具有相位噪聲選項的頻譜分析儀進行測量。

通常在同一圖上顯示的是非隨機的短期時鐘相位波動,稱為spurs或spurious。這些spurious,表示為分立組件,單位為dBc。

與其他系統分析一樣,我們通常會發現在頻域中更容易理解時鐘設備和時鐘分配網絡或時鐘樹。

必須使用,或至少從相對噪聲大或抖動的時鐘開始的工作并不罕見。這些可能出于許多原因。例如,當時鐘是:

·從串行數據流中恢復

·源自噪聲大的IC,如FPGA或噪聲大的PC板

·衍生自TCXO或OCXO,具有良好的漂移規格,否則會出現抖動

·“間隙”,意味著為了同步的目的缺少邊緣

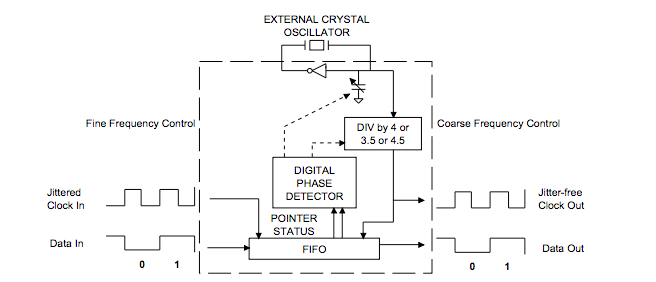

在這種情況下,我們需要一種特定類型的時鐘器件,抖動衰減器或“抖動清除器”來衰減或最小化相位噪聲并超出感興趣的偏移頻率。然后將所得到的輸出時鐘分配到需要改進抖動性能的設備。

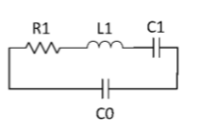

抖動衰減器的特征在于它們本質上是具有“低通”抖動傳遞函數的窄帶鎖相環(PLL)。這就是這些器件衰減頻率大于PLL環路帶寬(BW)的抖動分量。現代的抖動衰減器通常具有從0.1Hz到高達1或幾kHz的寬范圍內的可編程環路BW。

相比之下,另一類時鐘芯片,即時鐘發生器,是主要用于從低抖動源的時鐘乘法的寬帶PLL。這些設備通常具有大約100s kHz到1MHz的固定環路帶寬。

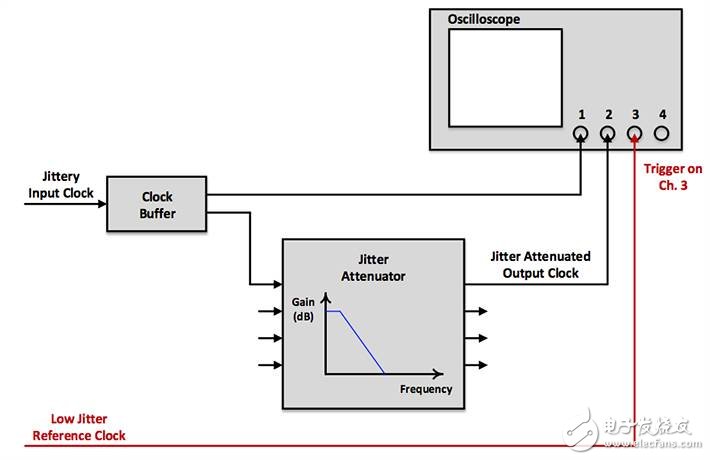

那么問題來了?客戶經常會和我們聯系,并寫下像我們正在測試你的一個時鐘芯片,并比較輸出時鐘和輸入時鐘,但抖動很大。我們總是會發現,測試設置歸結為如下所示:示波器被抖動輸入時鐘觸發。

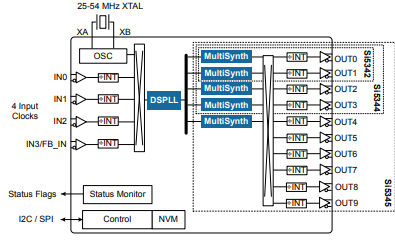

結果通常看起來與下面所示的相似。在這個例子中,抖動衰減器是一個Si5347,其環路BW = 100Hz。頂部的黃色軌跡是輸入時鐘,該信號是來自信號發生器的25 MHz正弦波,信號發生器采用1 kHz FM,100 Hz偏差。底部的綠色軌跡是輸出時鐘,只是為了保持簡單,也是25 MHz。

輸出時鐘應該不那么抖動,抖動是否衰減?這是抖動衰減時鐘的情況。

考慮到前面所述的測量設置,必須有三個因素來觀察這個明顯的問題:

1.輸入時鐘抖動。

2.輸出時鐘抖動不大。換句話說,抖動衰減器正在做它的工作。

3.輸出時鐘通過與輸入時鐘比較由輸入時鐘觸發。

現在您應該能夠認識到基本的問題,即使其隱藏在更復雜的應用程序中。

請注意,如果您在輸出時鐘上觸發,那么輸入時鐘將看起來抖動很大。見下文。哪個時鐘出現抖動只是一個觸發視角的問題。在不知道哪個時鐘更加不穩定的前提下,這種特定的范圍測量并不是決定性的。

您可以通過抖動衰減器的環路帶寬來獲得有關此特定測試配置的真實情況的信息。嘗試縮小和擴大BW,然后觀察范圍內的結果。

假設有一個抖動的輸入時鐘,你通常應該看到,加寬BW使得輸出時鐘顯示出比輸入時鐘更小的抖動。這是因為加寬BW意味著PLL將更多的跟蹤輸入時鐘,抖動和其他。在下面的圖4中,Si5347的環路寬度已經擴大到4 kHz。基本上沒有抖動衰減,與輸入時鐘相比,輸出時鐘沒有顯示出抖動。

相反,縮小BW會使輸出時鐘與輸入時鐘相比更加抖動。這是因為較窄的環路BW對應于更多的抖動衰減。具有諷刺意味的是,這種測試配置中的抖動衰減器是非常成功的,這是問題的根本原因。如果輸出時鐘只是跟蹤輸入時鐘,則觸發源將是無關緊要的。在下圖中,Si5347的環路寬度被縮小到100 Hz。

抖動衰減時鐘通常不同于其抖動輸入時鐘,高于和超出任何頻率縮放。如果其頻譜發生明顯變化,則在測量和比較每個時鐘的相位噪聲時應該相對明顯。然而,如前所述,這需要專門的設備,如相位噪聲分析儀或具有相位噪聲選項的頻譜分析儀。

如果你有一個范圍,那么同時比較抖動輸入和抖動衰減輸出時鐘的更好方法是什么?找到仲裁的第三方。換句話說,找到或生成與抖動參考時鐘相關的整數,并且與輸入和輸出時鐘同步。然后使用其作為輸入和輸出時鐘的觸發的參考。請參見下圖中修訂的測試設置圖。現在,您可以在時域中同時明確比較輸入和輸出時鐘的抖動。

以下是幾個示例圖,其中所有示波器走線如前所述為25 MHz。頂部的黃色軌跡是抖動(調頻)輸入時鐘,中間的綠色軌跡是抖動衰減器的輸出時鐘。底部的藍色軌跡是用作觸發的新的低抖動參考時鐘。首先,在下圖中,抖動衰減器的環路BW為4 kHz,輸出時鐘像輸入時鐘一樣抖動。

在第二種情況下,在下圖中,抖動衰減器的環路BW為100 Hz,輸出時鐘的抖動要小得多。在這個特定的例子中,當環路BW從4 kHz降低到100 Hz時,抖動衰減時鐘周期與周期抖動的標準偏差從8.2 ps下降到1.1 ps。

-

相位噪聲

+關注

關注

2文章

181瀏覽量

22907 -

抖動衰減

+關注

關注

0文章

2瀏覽量

3623

原文標題:秒懂時鐘: 抖動衰減時鐘設計與應用技巧 – Part 1

文章出處:【微信號:SiliconLabs,微信公眾號:Silicon Labs】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Silicon Labs推Si539x抖動衰減器 簡化高速網絡時鐘設計

使用抖動衰減器常見設置測量狀況的原因

時鐘抖動的基礎

Si5345和SI5344及SI5342系列抖動衰減時鐘倍增器的數據手冊免費下載

抖動衰減時鐘設計與應用技巧資料下載

時鐘抖動和時鐘偏斜講解

差分探頭對時鐘測試影響

差分探頭對時鐘測試的影響

簡述時鐘抖動的產生原因

時鐘抖動與相位噪聲的關系

高性能抖動衰減器和時鐘發生器的推薦晶體、TCXO和OCXO參考手冊(之一)

教你如何在如何對時鐘抖動衰減測試設置

教你如何在如何對時鐘抖動衰減測試設置

評論