【LLC眾籌】張飛60小時精通半橋LLC諧振電源設計教程,眾籌最后6天! >點此立即眾籌<

不斷增加的開關電源功率密度,已經受到了無源器件尺寸的限制。 采取高頻運行,可以大大降低無源器件,如變壓器和濾波器的尺寸。 但是過高的開關損耗勢必成為高頻運行的一大障礙。 為了降低開關損耗和容許高頻運行,諧振開關技術已經得到了發展。這些技術采用正弦方式處理電力,開關器件能夠實現軟轉換。 使得開關損耗與噪聲大為降低。

在各種類型的諧振轉換器中,最簡單和最普遍的諧振轉換器為 LC 串聯諧振轉換器,其中整流器-負載網絡與 LC 諧振網絡串聯,如 圖 1 [2-4]所示。 在該電路結構中,LC諧振網絡與負載一起形成分壓器。 通過改變驅動電壓Vd的頻率,可以改變該諧振網絡的阻抗。輸入電壓在諧振網絡阻抗與反射負載之間進行分壓。由于分壓作用,LC 串聯諧振轉換器的 DC 增益總是小于1。在輕載條件下,相比諧振網絡的阻抗而言,負載阻抗很大。全部輸入電壓都被施加到負載上。 這使得輕載下很難調節輸出。 在空載時,為了能夠調節輸出,理論上諧振頻率應該為無限大。

為了打破串聯諧振轉換器的限制,LLC諧振轉換器已經獲得提出[8-12]。 LLC 諧振轉換器是一種改進型的LC 串聯諧振轉換器,通過在變壓器初級繞組放置一個并聯電感而得以實現,如圖 2所示。 采用并聯電感可以增加初級繞組的環流,有利于電路運行。 由于這個概念不直觀,在該拓撲首次提出時沒有受到足夠的重視。 然而在開關損耗相比通態損耗占主導比重的高輸入電壓應用中,卻有利于效率的提高。

在大多數實際設計中,該并聯電感采用變壓器的勵磁電感。 LLC諧振轉換器的電路圖與LC串聯諧振轉換器的電路圖十分相似。 唯一的差別在于:勵磁電感的取值不同。 LLC諧振轉換器的勵磁電感遠遠大于LC串聯諧振轉換器的勵磁電感(Lr),LLC諧振轉換器中的勵磁電感為Lr的3-8倍,通常通過增加變壓器的氣隙來獲得。

LLC諧振轉換器具有許多超越串聯諧振轉換器的優點。它能夠在較寬的電源和負載波動范圍內調節輸出,而開關頻率波動卻較小。 在整個工作范圍內,能夠獲得零電壓開關(ZVS)。 全部固有的寄生參數均可以用于實現軟開關,包括所有半導體器件的結電容、變壓器漏感與勵磁電感。

包括LLC諧振轉換器工作原理的解釋、變壓器與諧振網絡的設計、元器件的選型。 給出設計實例,逐條地解釋設計過程,有助于進行LLC諧振轉換器的設計。

LLC 諧振轉換器與基波近似

圖 3中給出了半橋 LLC 諧振轉換器的原理簡圖,圖中,Lm指勵磁電感,用作并聯電感,Lr指串聯諧振電感,Cr 指諧振電容。圖 4給出了 LLC 諧振轉換器的典型波形。 假定:工作頻率與諧振頻率相同,后者決定于 Lr 與Cr.之間的諧振。 由于勵磁電感相對較小,形成相當量的勵磁電流(Im),在初級繞組續流,并不參與電能的傳輸。初級電流(Ip)為勵磁電流與次級電流反射到初級的電流之和。

一般情況下,LLC 諧振拓撲包括 3 級電路,如圖 3所示,即方波發生器、諧振網絡和整流器網絡。

? 方波發生器負責產生方波電壓Vd,通過50%占空比交替驅動開關Q1 和Q2 來實現。 通常,在連續切換中會引入一個較小的死區時間。 方波發生器可以構造成全橋或半橋類型。

? 諧振網絡包括一只電容、變壓器漏感和勵磁電感。 諧振網絡濾除高次諧波電流。 在本質上,即使方波電壓施加到諧振網絡上,也只有正弦電流容許流過該諧振網絡。 電流(Ip)滯后于施加到諧振網絡上的電壓(即方波電壓(Vd)的基波分量被施加到半橋的圖騰柱上),容許MOSFET零電壓開通。 如圖 4所示,當 MOSFET 電壓為零時MOSFET 開通,此時電流流經反并聯二極管。

? 整流器網絡產生直流電壓,采用整流器二極管和電容對交流電進行整流器。 整流器網絡可以設計成帶有容性輸出濾波器的全波整流器橋或中心抽頭配置。

諧振網絡的濾波作用可以采用基波近似原理,獲得諧振轉換器的電壓增益,這需要假定方波電壓的基波分量輸入到諧振網絡,并傳輸電能至輸出端。 由于次級端整流電路可作為阻抗變壓器,所以其等效負載電阻與實際負載電阻并不相同。圖 5所示為該等效負載電阻的推導方式。 初級電路由正弦電流源Iac代替,方波電壓VRI出現在整流器的輸入端。 由于|Iac|的平均值為輸出電流 Io,則Iac可以描述為

注:Vo指輸出電壓。

由于VRI的各次諧波分量不涉及功率傳輸,交流等效負載電阻可以采用(VRIF/ Iac)計算:

考慮到變壓器匝比(n=Np/Ns),則初級等效負載電阻可

以描述為

采用等效負載電阻,可以得到交流等效電路,如圖 6

FF

所示,圖中Vd 和VRO 分別指驅動電壓Vd 和反射輸出電壓VRO (nVRI)的基波分量。

利用式5中得到的等效負載電阻,可以推導出LLC諧振轉換器的特性。 利用圖 6所示的交流等效電路,可得電壓增益M的計算公式:

圖7給出了 Q 值不同且 m=3、fo=100kHz 且fp=57kHz

時,式 6 表達出的增益。 由圖 7可見,當開關頻率處于諧振頻率fo附近時,LLC 諧振轉換器顯示的電壓增益特性幾乎獨立于負載。 這是LLC型的諧振轉換器超出傳統串聯諧振轉換器非常突出的優勢。 因此,想當然地使得轉換器運行在諧振頻率附近,降低開關頻率波動。

LLC 諧振轉換器的工作范圍受制于峰值增益(可達最大增益),該增益標示有‘*’(如圖 7所示)。 需要說明的是,峰值電壓增益不會出現在fo 或 fp.附近。 獲得峰值電壓增益的頻率位于fp和fo之間,如圖 7所示。 隨著負載變輕,Q值下降,峰值增益頻率移向fp,峰值增益隨之下降。 因此對于諧振網絡設計而言,滿載條件為最壞情況。

集成變壓器的考慮事項

對于實際設計,通常需要采用集成變壓器的概念設計實現磁器件(串聯電感與并聯電感),其中將漏感用作串聯電感,勵磁電感用作并聯電感。 當采用這種方法構造磁元件時,需要將圖 6中的等效電路改進成圖8,這是因為不僅在初級,而且在次級都存在有漏感。不考慮變壓器次級的漏感時往往會導致設計出錯。

在處理實際變壓器時,提倡采用具有Lp 和 Lr的等效電路,因為通過分別開路和短路次級繞組,在初級可以很容易地測得這些電感取值。 在實際變壓器中,Lp和Lr可分別在次級端繞組開路和短路的條件下在初級側測得。

在圖 9中,引入了一個虛擬增益 MV,這個增益是由次級端漏電感導致的。 采用圖9改進后的圖 9等效電路,調整式6的增益表達式,可以得到集成變壓器的增益表達式:

工作模式與可達最大增益考慮事項

LLC 諧振轉換器的工作頻率可以低于或高于諧振頻率(fo),如圖 10所示。圖 11給出了每種工作模式下變壓器初級與次級的電流波形。 在低于諧振頻率下(情況I )工作,容許次級整流器二極管實現軟換流,盡管此時環流相比較大。 隨著工作頻率降低,偏離 ID諧振頻率,環流大大增加。 盡管在高于諧振頻率下(情況II )工作,容許環流降低,但是整流器二極管不能實現軟換流。 對于高輸出電壓應用中,例如等離子顯示屏(PDP),提倡采用低于諧振頻率下工作,因為這類應用場合中整流器二極管的反向恢復損耗相當

大。 低于諧振頻率下工作,對于負載波動而言,還具有較窄的頻率范圍,因為甚至在空載條件下運行,其工作頻率受限制低于諧振頻率。

另一方面,在上諧振工作時,相比在下諧振工作時,通態損耗較小。 對于低輸出電壓的應用場合,例如液晶顯示器(LCD)TV或膝上適配器,表現出良好的效率。 因為這類應用場合中,次級整流器二極管適合采用肖特基二極管,此時反向恢復問題已無關重要。 然而,在上諧振頻率工作時,在輕載下工作會使開關頻率大量增加。 上諧振工作時,需要采用頻率跳躍功能,防止開關頻率劇烈上升

最大增益與峰值增益需求

高于峰值增益頻率下,諧振網絡的輸入阻抗呈感性,諧振網絡的輸入電流 (Ip)滯后于施加在諧振網絡的電壓(Vd). 這樣 MOSFET 可以實現零電壓開通 (ZVS),如圖 12所示。 低于峰值增益頻率下,諧振網絡的輸入阻抗呈容性,Ip超前Vd. 當工作在容性區間,在開關切換過程中,MOSFET的體二極管反向恢復,引起嚴重的噪聲。 進入容性區間的另外一個問題是,由于增益斜率出現反向,輸出電壓失控。 最小開關頻率應該適當地高于峰值增益頻率

LLC諧振轉換器的合適輸入電壓范圍決定于峰值電壓增益。 因此,諧振網絡的設計應確保增益曲線具有足夠的峰值增益,并能夠覆蓋整個輸入電壓范圍。 但是,低于峰值增益點,ZVS 條件會丟失,如圖 12所示。因此當確定最大增益點時,要求保留一些裕量,在負載瞬態變化和啟動階段,確保獲得穩定的ZVS工作。典型地,對于實際設計,選取最大增益的 10~20% 作為裕量,如圖 13所示。

在某一給定的條件下,即使采用增益公式6得到峰值增益,也是很難地以明確形式表達出峰值增益。 為了簡化分析與設計,可以采用仿真工具獲得峰值增益,如圖 14所示。圖中給出了不同 m 取值時,隨著Q值變化的峰值增益(可達最大增益)。 可見,通過減少m和Q值,可以獲得較高的峰值增益。 對于給定的諧振頻率 (fo)和 Q 值,降低m意味著勵磁電感減少,將導致環流增加。 自然地,應在可用增益范圍與導通損耗之間作出權衡。

FSFR系列的特征

FSFR系列產品集成有脈沖頻率調制(PFM)控制器以及專門設計用于零電壓開關(ZVS)半橋轉換器的MOSFET,外部元器件用量最少。內部控制器包括一個欠壓閉鎖、優化的高端/低端柵極驅動器、溫度補償的精密電流控制振蕩器以及自保護電路。 與分立MOSFET和PWM控制器方案相比,FSFR系列產品減少了總成本、元器件數量、尺寸和重量,與此同時卻提高了效率、生產率和系統可靠性。

設計步驟

本節提供了基于圖 17所示原理圖的設計步驟。 集成變壓器具有中心抽頭,輸入電壓來自預調節器-功率因數校正器(PFC)。 帶有 192W/24V 輸出的DC/DC轉換器已被選中作為設計實例。 設計規格如下:

- 標稱輸入電壓: 400VDC (PFC 級的輸出)- 輸出: 24V/8A (192W)

- 保持時間要求: 20 毫秒(50Hz 電源頻率)

- PFC 輸出直流電容: 220μF

[[STEP-1] 確定系統的各項指標

[[STEP-2確定諧振網絡的最大與最小電壓增益

根據上節討論,為了減少開關頻率波動,典型地,LLC諧振網絡應設計工作在諧振頻率 (fo) 附近。 鑒于LLC諧振轉換器由PFC輸出電壓供電,為使該轉換器的工作頻率設計在fo,應該適應PFC標稱輸出電壓。

由式10可見,fo處的增益為m (m=Lp/Lr).的函數。 fo處的增益決定于m值的選取。 盡管m 取值較小時,可以得到高的峰值增益,但是過小的m 取值會導致變壓器的耦合惡化和效率下降。 典型地,設置m 位于3~7,可使諧振頻率處(fo)的電壓增益為1.1~ 1.2。

m取值選擇后,PFC標稱輸出電壓時的電壓增益可以描述為:

- 磁芯: EER3542 (Ae=107 mm2)

- 骨架: EER3542(水平/分段類型)

6. 實驗驗證

為了驗證本使用說明書中設計過程的有效性,對本轉換器設計實例的進行了建立和測試。 設計實例中涉及的全部電路元件都得到了采用。

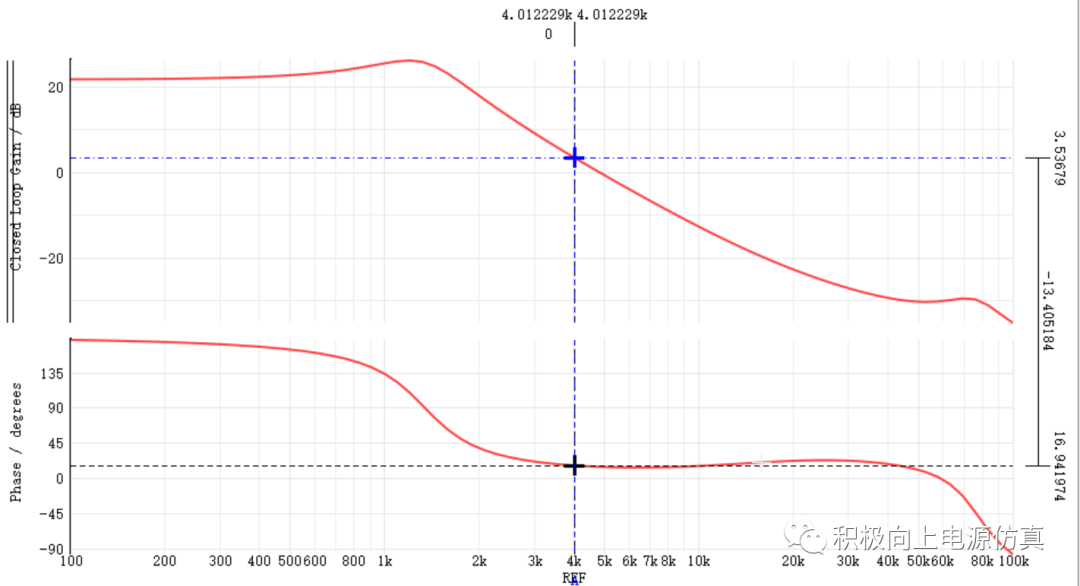

圖 30和圖 31給出了標稱輸入電壓時滿載與空載下的工作波形。 可見,由于諧振作用,在開通前,MOSFET的漏源電壓 (VDS)下降至零,實現了零電壓切換。

圖 32給出了滿載條件下諧振電容電壓和初級電流波形。 諧振電容電壓與初級端電流的峰值分別為 325V 與1.93A,這與設計過程章節中第八步的計算值非常匹配。圖 33給出了輸出短路條件下諧振電容電壓和初級端電流波形。 對于輸出短路條件,當初級電流大于3A時,過電流(OCP)發生動作。 諧振電容的最大電壓略高于計算值419V,其原因是1.5μs的關閉延時使得OCP動作電流略高于3A(參閱FSFR2100產品說明書)。

圖 34給出了滿載和空載條件下整流器二極管的電壓與電流波形。 由于雜散電感引起的電壓過沖,電壓應力略高于第九步中的計算值。圖 35 給出了滿載和空載條件下輸出電壓的紋波波形。 輸出電壓的紋波與第九步中的設計值相配。

圖 36給出了不同負載條件下效率測量結果。 滿載條件下的效率大約為94%。

圖文 I 網絡

-

LLC

+關注

關注

36文章

571瀏覽量

76987 -

諧振

+關注

關注

5文章

377瀏覽量

39653

原文標題:LLC計算最全套路

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LLC最全計算套路

LLC最全計算套路

評論