介紹

半導(dǎo)體行業(yè)不斷演變,旨在滿足用戶對移動設(shè)備和數(shù)字家庭等領(lǐng)域中每一代新產(chǎn)品的多方面需求,包括更多功能、性能、電池壽命和更低成本。半導(dǎo)體工藝技術(shù)的演進遵循摩爾定律,這是這些產(chǎn)品得以上市的主要促成因素。對整個行業(yè)來說,從基于大體積平面晶體管向FinFET三維晶體管的過渡是一個重要里程碑。這一過渡促使工藝技術(shù)經(jīng)過了幾代的持續(xù)演進,并且減小了外形尺寸,提高了速度,同時減少了泄漏。

過去,最先在先進的工藝技術(shù)中部署的絕大多數(shù)產(chǎn)品都采用以數(shù)字為中心的數(shù)據(jù)處理方式,而模擬處理方式則保留給更保守的工藝技術(shù)使用。設(shè)計人員選擇利用保守工藝中對模擬方式更加友好的特征,并且錯誤地認為模擬塊區(qū)域在先進的工藝技術(shù)中無法擴展,或者價格昂貴。

對于每個連接擁有超過10 Gbps數(shù)據(jù)吞吐量的無線連接和大量設(shè)備連接(1000億個鏈路),這些連接都需要更復(fù)雜的數(shù)字信號處理。因此,設(shè)計人員應(yīng)考慮FinFET技術(shù)在高性能、低功耗和小體積方面的優(yōu)勢。如果大部分模擬功能集成到單獨的晶片中,例如RF芯片,則它需要數(shù)據(jù)轉(zhuǎn)換器 – 模擬數(shù)字 (ADC) 和數(shù)字模擬 (DAC) 轉(zhuǎn)換器 – 作為外部模擬處理功能和內(nèi)部數(shù)字處理塊之間的接口。這些數(shù)據(jù)轉(zhuǎn)換器一般集成到數(shù)字芯片系統(tǒng) (SoC) 中,以消除對傳統(tǒng)高耗電數(shù)字接口的需求。因此,在FinFET工藝中部署數(shù)據(jù)轉(zhuǎn)換器非常重要。本文介紹設(shè)計人員如何采用針對FinFET工藝的IP而克服數(shù)據(jù)轉(zhuǎn)換器設(shè)計的挑戰(zhàn)。

針對數(shù)據(jù)轉(zhuǎn)換器設(shè)計的FinFET工藝

盡管在FinFET工藝中設(shè)計數(shù)據(jù)轉(zhuǎn)換器和其他模擬功能存在挑戰(zhàn),但將這些功能集成到FinFET工藝的SoC中也有一些關(guān)鍵的優(yōu)點:

使更多功能集成到同一個SoC中的趨勢繼續(xù)

通過將模擬和數(shù)字功能密切集成到同一個SoC中降低功耗

消除對高耗電芯片間數(shù)字接口的需求

模擬功能設(shè)計人員也可以從FinFET工藝的特征中受益:

通過使用最少的特性而減小體積(線路、晶體管等):豐富且低價的區(qū)域和高速數(shù)字門有助于實施數(shù)字輔助型模擬功能,以提高可靠性,并減少IP體積和功耗(例如,通過數(shù)字校準)

更好的通道控制:3D門增強了控制設(shè)備門的能力,并且改善了晶體管的總體特征,無論是作為交換機還是作為模擬放大器設(shè)備運行

更快的設(shè)備:由于采用具有高傳輸頻率 (Ft) 的晶體管,高速工藝消除了需要極高帶寬或高速度的模擬功能的某些設(shè)計限制

降低設(shè)備可變性:更好的設(shè)備匹配特征簡化了模擬設(shè)計,并減小了體積

FinFET設(shè)計流程中的布局和示意圖

FinFET工藝的特定特征使得為平面CMOS設(shè)計而定義的傳統(tǒng)設(shè)計流程效率低下。模擬功能設(shè)計人員必須特征所用的方法,將以下特征考慮在內(nèi):

FinFET晶體管體積的離散量化

電氣特征對布局寄生現(xiàn)象的高度依賴

金屬線路的更高電阻率和更高寄生電容

對匹配的結(jié)構(gòu)的雙重模式影響

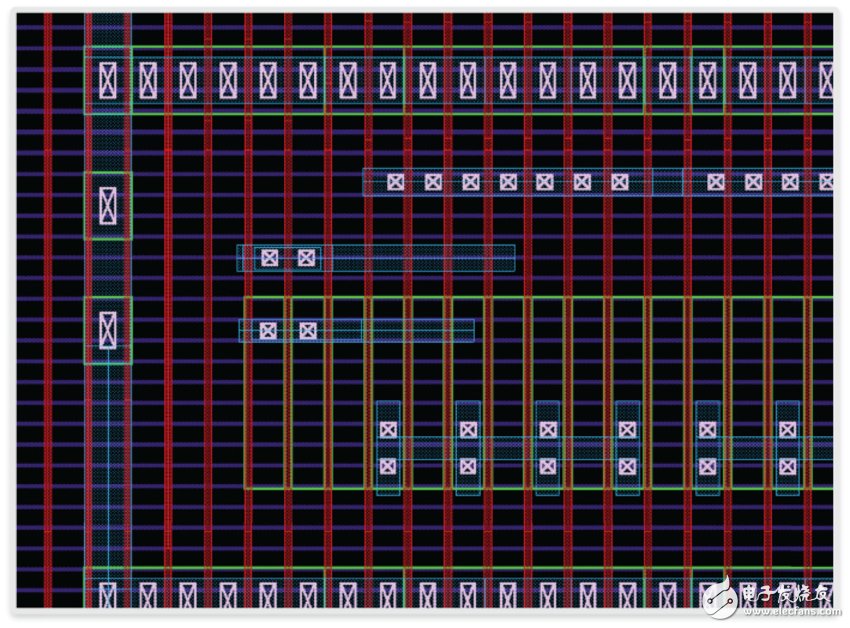

通過對定期測量的FinFET設(shè)備進行并行和串行組合而實現(xiàn)幾乎任何有效的設(shè)備寬度/長度,F(xiàn)inFET工藝的某些復(fù)雜特征(例如鰭片寬度的有限粒度)可得到有效的管理。因此,設(shè)計人員能夠以稍高的抽象化進行設(shè)計(有效的設(shè)備),以降低電氣設(shè)計的復(fù)雜度。圖1顯示了定期測量的FinFET的布局,其中,在與綠色長方形重疊的區(qū)域(活動區(qū)域),各個晶體管是垂直紅線(多晶硅)和水平藍線(鰭片)的交叉點。

圖1:常規(guī)FinFET布局示意圖

然而,電遷移、更高的負偏壓溫度不穩(wěn)定性(NBTI)和正偏壓溫度不穩(wěn)定性(PBTI) 導(dǎo)致的老化效應(yīng)迫使設(shè)計人員假設(shè)更高的設(shè)計余量,有時要以犧牲體積或性能為代價。

布局寄生結(jié)構(gòu)上設(shè)備電氣特征的復(fù)雜依賴關(guān)系導(dǎo)致電路行為對物理布局的極高依賴。這意味著在轉(zhuǎn)到布局之前需要對最終電路原理圖進行驗證的傳統(tǒng)模擬設(shè)計流程效率很低。布局寄生效應(yīng)無法通過設(shè)計的少量調(diào)整而輕松恢復(fù),而是有可能需要對電路進行完整的重新設(shè)計。

更高效的流程依賴電路物理布局的創(chuàng)建,這要在設(shè)計過程的早期進行,這樣,電路的所有迭代都基于后批注結(jié)果。

FinFET技術(shù)的物理設(shè)計規(guī)則比前幾代技術(shù)有更大的局限性。完成無誤的布局需要更多次迭代,并且比前幾代工藝需要的時間長得多。然而,通過在最初設(shè)計階段認識到:嚴格遵守所有規(guī)則進行布局迭代并不是評估對性能的寄生效應(yīng)的必然要求,前提是布局與示意圖匹配。圖2顯示了FinFET工藝中12位高速ADC的布局例子。

圖2:FinFET布局舉例:12位高速ADC

金屬堆疊與顏色

雙模式是FinFET工藝的關(guān)鍵優(yōu)勢,因為它在設(shè)備層面和金屬配線層面實現(xiàn)了更精細的形狀間距,同時具有基本相同的間距。

對于大多數(shù)模擬設(shè)計,CAD工具和設(shè)計規(guī)則允許設(shè)計人員忽略雙重模式,因為設(shè)計工具將自動對設(shè)計進行顏色標記(選擇將兩個模式/掩碼中的哪一個用于每種形狀)。然而,模擬設(shè)計中存在匹配關(guān)鍵結(jié)構(gòu),如金屬-氧化物-金屬 (MOM) 電容,或者存在關(guān)鍵信號跟蹤路徑,在這些路徑中,匹配特征可能受到采用其他方式匹配的布局中不均勻的顏色選擇影響。在這些情況下,設(shè)計人員可以實施平衡的配色,以確保最佳的匹配。圖3顯示了帶有扭曲手指結(jié)構(gòu)的MOM電容的例子,這種結(jié)構(gòu)的原因是高級工藝中的每個金屬層采用不同的設(shè)計網(wǎng)格。出于匹配目的,每個電容中相應(yīng)的手指應(yīng)組合到同一個掩碼中(顏色)。

圖3:FinFET中的MOM電容布局舉例

這些考量尤其與依賴交換電容架構(gòu)而實現(xiàn)模擬功能的設(shè)計相關(guān),例如模擬數(shù)字轉(zhuǎn)換器。類似的考量也適用于電流源間準確匹配是設(shè)備性能關(guān)鍵的電路,例如電流或電壓控制DAC。

高密度配線作為減小間距的副作用,是金屬線的電阻,并且大大提高了側(cè)邊寄生電容。在某些模擬設(shè)計中,關(guān)鍵路徑或裝置的自導(dǎo)噪音和關(guān)鍵節(jié)點上的總負荷(包括寄生)可嚴重影響電路性能。在某些情況下,這可能完全消除更先進的工藝的速度優(yōu)勢,影響系統(tǒng)性能和功耗。副作用必須及早評估,而且每個設(shè)計階段都必須根據(jù) (RCC) 布局抽象而進行模擬。

結(jié)束語

在FinFET技術(shù)中,數(shù)據(jù)轉(zhuǎn)換器和其他模擬IP塊的成功開發(fā)要求設(shè)計人員部署優(yōu)化的設(shè)計方法論,這樣才能充分利用該工藝的高速、低功耗和小提交的優(yōu)點。28nm平面CMOS設(shè)計中經(jīng)過驗證的方法論不再適用,因為這些方法論導(dǎo)致設(shè)計速度超慢,而且需要經(jīng)過太多次的設(shè)計迭代,最終導(dǎo)致性能和良品率不佳。Synopsys的DesignWare? Data Converters IP系列支持遷移技術(shù)從平面CMOS向FinFET遷移。該IP系列可幫助設(shè)計人員滿足模擬前端接口要求,同時降低物料成本,最大限度減少集成限制因素,例如配線和凸點轉(zhuǎn)移。12位高速DesignWare ADC基于SAR的架構(gòu)提供了320 MSPS的數(shù)據(jù)速率,并且提供了并行裝配選項,從而減小體積,降低功耗,并提高架構(gòu)的可擴展性。12位 DAC以 針對高信號帶寬的640 MSPS速率實現(xiàn)了低功耗。Synopsys全面的數(shù)據(jù)轉(zhuǎn)換器IP已經(jīng)集成到大量工藝的300多個SoC中,幫助設(shè)計人員降低集成風險,并加快產(chǎn)品上市速度。

-

IP

+關(guān)注

關(guān)注

5文章

1716瀏覽量

149853 -

數(shù)據(jù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

366瀏覽量

28078

發(fā)布評論請先 登錄

相關(guān)推薦

將數(shù)據(jù)轉(zhuǎn)換器IP集成到系統(tǒng)芯片簡化設(shè)計技術(shù)

基于FinFET IP的數(shù)據(jù)轉(zhuǎn)換器設(shè)計

Synopsys宣布提供經(jīng)中芯國際65nm低漏電工藝芯片驗證的DesignWare數(shù)據(jù)轉(zhuǎn)換器IP

ADC0809模數(shù)轉(zhuǎn)換器的使用詳解與程序

FinFET工藝的IP數(shù)據(jù)轉(zhuǎn)換器設(shè)計

關(guān)于汽車ADAS SoC的數(shù)據(jù)轉(zhuǎn)換器IP的介紹和應(yīng)用

串口轉(zhuǎn)換器工作方式_串口轉(zhuǎn)換器通訊模式

【單片機基礎(chǔ)】ADC0809模數(shù)轉(zhuǎn)換器詳解

克服升壓轉(zhuǎn)換器本身限制的方法

IP_數(shù)據(jù)表(A-11):雙通道 8b D/A 轉(zhuǎn)換器

IP_數(shù)據(jù)表(A-10):單/雙通道 12b D/A 轉(zhuǎn)換器

如何克服升壓轉(zhuǎn)換器本身的限制

IP_數(shù)據(jù)表(A-11):雙通道 8b D/A 轉(zhuǎn)換器

IP_數(shù)據(jù)表(A-10):單/雙通道 12b D/A 轉(zhuǎn)換器

FinFET工藝的IP克服數(shù)據(jù)轉(zhuǎn)換器設(shè)計詳解

FinFET工藝的IP克服數(shù)據(jù)轉(zhuǎn)換器設(shè)計詳解

評論