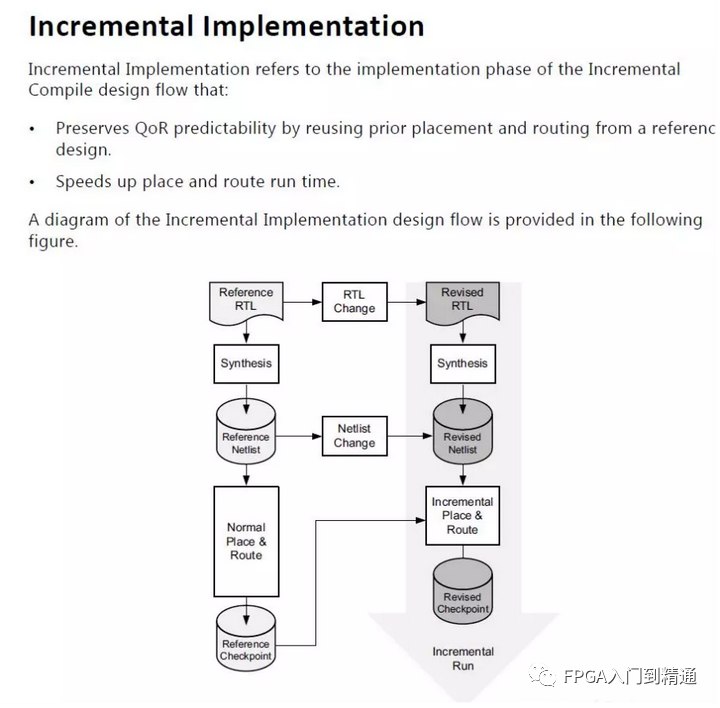

Incremental Compile增量編譯是Vivado提供的一項高階功能。目的旨在當設計微小的改變時,重用綜合和布局布線的結果,縮短編譯時間。

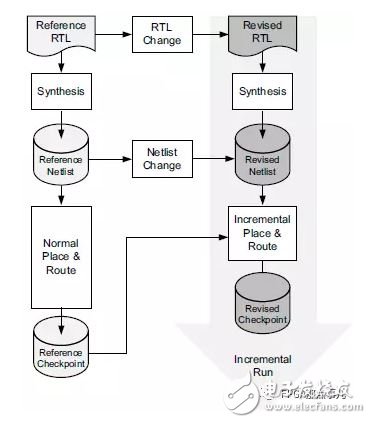

下圖是增量編譯的流程:

增量編譯需要已經編譯完成的原始設計的dcp文件作為參考,當我們在原始設計上做微小的改動時,就可以使用增量編譯的流程。這些改動包括:

- RTL代碼的微小修改

- 網表的微小修改,比如增加或者改變ILA

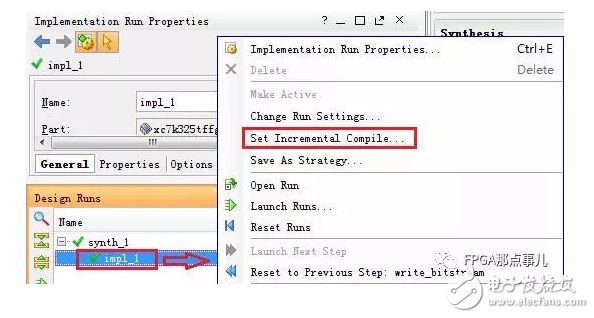

在Vivado里面,使能IncrementalCompile的方式非常簡潔,在Impl run上右鍵選擇“Set Incremental Compile…”,然后設置相應的參考dcp文件即可:

Tips:

1. 當參考設計和當前設計的相似度大于95%的時候,最適合用增量編譯技術

相似度低于75%時,工具會關閉增量編譯

2. 有些時候,即使很小的RTL改動,也會造成網表的巨大差異。比如

a) 改變HDL中的某些全局常量

b) 增加總線的位寬

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Vivado

+關注

關注

19文章

815瀏覽量

66801

發布評論請先 登錄

相關推薦

Altium如何放置compile mask(編譯屏蔽)

方法步驟如下:原理圖界面上place(放置)-->directives(指示)-->compile mask(編譯屏蔽),拖動鼠標,框住不需編譯的電路。 取消的方法:不需要刪除,之需要在編譯

發表于 09-17 14:08

誰能縮短大容量FPGA的編譯時間?增量式編譯QIC!

增量式編譯(Incremental Compilation)是ALTERA為解決大容量FPGA設計編譯時間太長的問題給出的一個新式工具!在本文中我們將闡述QIC在縮短

發表于 12-25 11:26

?5062次閱讀

Vivado Design Suite 2015.3的新功能介紹

了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量

Vivado Design Suite 2015.3新增量編譯功能介紹

了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量

Vivado綜合引擎的增量綜合流程

從 Vivado 2019.1 版本開始,Vivado 綜合引擎就已經可以支持增量流程了。這使用戶能夠在設計變化較小時減少總的綜合運行時間。

發表于 07-21 11:02

?1721次閱讀

Vivadoz中增量編譯與設計鎖定

關于增量編譯所謂增量實現,更嚴格地講是增量布局和增量布線。它是在設計改動較小的情形下參考原始設計的布局、布線結果,將其中未改動的模塊、引腳和

發表于 12-20 19:11

?6次下載

Vivado增量編譯的基本概念、優點、使用方法以及注意事項

隨著FPGA設計的復雜度不斷提高,設計人員需要選擇更為高效的設計流程來保證開發效率和減少開發成本。其中,Vivado增量編譯是一種非常重要的設計流程。本文將介紹Vivado

Xilinx Vivado使用增量實現

增量實現自從首次獲得支持以來,不斷升級演變,在此過程中已添加了多項針對性能和編譯時間的增強功能。它解決了實現階段針對快速迭代的需求,顯著節省了編譯時間,還能確保所得結果和性能的可預測性

Vivado中的Incremental Compile增量編譯技術詳解

Vivado中的Incremental Compile增量編譯技術詳解

評論