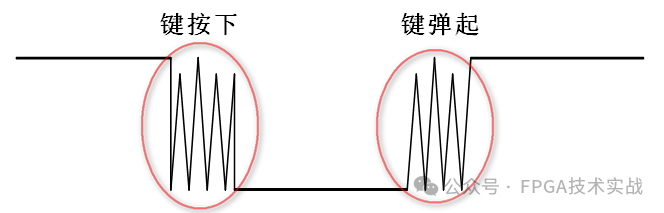

在FPGA(現場可編程門陣列)中實現按鍵消抖是一個重要的設計環節,特別是在處理用戶輸入時,由于物理按鍵的機械特性和電氣特性,按鍵在按下和釋放的瞬間會產生抖動現象,這種抖動可能導致系統錯誤地識別為多次按鍵操作。因此,實現有效的按鍵消抖機制對于提高系統的穩定性和可靠性至關重要。以下是在FPGA中實現按鍵消抖的詳細步驟和策略,包括原理、方法、代碼示例及優化建議。

一、按鍵消抖原理

按鍵消抖的原理基于按鍵在按下和釋放過程中產生的抖動現象。這種抖動通常表現為電平信號在短時間內快速變化,持續時間一般在幾毫秒到幾十毫秒之間。為了消除這種抖動對系統的影響,需要設計一個能夠識別并忽略這些短暫抖動的電路或邏輯。

二、實現方法

在FPGA中實現按鍵消抖主要有以下幾種方法:

1. 延時消抖

最簡單直接的方法是使用延時來消除抖動。當檢測到按鍵狀態變化時,不立即響應,而是等待一段時間(通常大于抖動時間)后再確認按鍵狀態。這種方法實現簡單,但占用資源較多,且延時時間固定,不夠靈活。

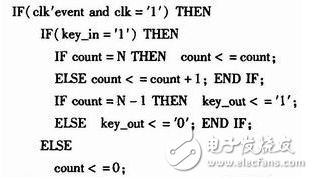

2. 計數器消抖

計數器消抖是一種更為靈活和精確的方法。當檢測到按鍵狀態變化時,啟動一個計數器開始計數。如果在這段時間內按鍵狀態再次發生變化,則認為是抖動,重置計數器;如果計數器達到預設的閾值(通常大于抖動時間),則確認按鍵狀態已穩定,進行相應的處理。這種方法可以根據實際情況調整閾值,適應不同的抖動情況。

3. 狀態機消抖

狀態機消抖是一種更為復雜但功能強大的方法。通過設計一個狀態機來跟蹤按鍵的狀態變化,并根據狀態轉移邏輯來消除抖動。狀態機通常包括空閑態、抖動態、穩定態等狀態,通過檢測按鍵的上升沿和下降沿以及計時器的值來在不同狀態之間轉移。這種方法可以精確地控制按鍵消抖的過程,并且可以根據需要添加更多的狀態和功能。

三、代碼示例

以下是一個基于計數器消抖的FPGA代碼示例(Verilog語言):

module key_debounce(

input clk, // 時鐘信號

input rst_n, // 復位信號,低電平有效

input key_in, // 按鍵輸入信號

output reg key_out // 消抖后的按鍵輸出信號

);

// 計數器參數

localparam COUNT_MAX = 20_000_000; // 假設時鐘頻率為50MHz,則20ms對應20_000_000個時鐘周期

reg [23:0] cnt; // 計數器,寬度根據最大計數值確定

reg key_prev; // 上一個時鐘周期的按鍵輸入信號

reg key_stable; // 按鍵穩定標志

// 同步按鍵輸入信號

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

key_prev <= 1'b1; // 復位時按鍵默認為未按下

end else begin

key_prev <= key_in;

end

end

// 計數器邏輯

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt <= 0;

key_stable <= 0;

end else if (key_prev != key_in) begin // 檢測到按鍵狀態變化

if (cnt < COUNT_MAX) begin

cnt <= cnt + 1;

end else begin

cnt <= 0;

key_stable <= 1; // 按鍵狀態穩定

end

end else if (key_stable) begin

// 如果按鍵已經穩定,則保持計數器為0,等待下一次狀態變化

cnt <= 0;

end

end

// 消抖后的按鍵輸出

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

key_out <= 1'b1; // 復位時輸出默認為高電平

end else if (key_stable) begin

key_out <= ~key_in; // 按鍵穩定后,根據按鍵狀態輸出低電平或保持高電平

end

end

endmodule

四、優化建議

1.選擇合適的計數器寬度

根據時鐘頻率和消抖時間要求,選擇合適的計數器寬度,以避免資源浪費和計數溢出。

2.考慮按鍵的電氣特性

不同的按鍵可能具有不同的電氣特性,如接觸電阻、釋放時間等,這些都會影響消抖效果。因此,在設計消抖邏輯時,需要考慮按鍵的電氣特性。

3. 利用狀態機設計提高靈活性

雖然計數器消抖方法已經能夠有效地處理大部分按鍵抖動問題,但狀態機設計能夠提供更高的靈活性和更強的控制能力。狀態機可以根據按鍵的不同狀態(如空閑態、抖動態、穩定態等)執行不同的操作,并且能夠更容易地處理復雜的按鍵行為,如長按、雙擊等。

在設計狀態機時,需要注意以下幾點:

- 狀態定義清晰 :明確每個狀態的含義和轉移條件,確保狀態機能夠正確地處理按鍵事件。

- 優化狀態轉移邏輯 :避免不必要的狀態轉移,減少狀態機的復雜度和功耗。

- 利用one-hot編碼 :對于狀態數量不多的情況,可以使用one-hot編碼來優化狀態機的實現,減少邏輯門的使用和提高電路的運行效率。

4. 增加防抖時間可調節性

在實際應用中,不同的按鍵或應用場景可能需要不同的防抖時間。因此,可以在FPGA設計中增加防抖時間的可調節性,以便根據不同的需求進行調整。這可以通過在FPGA配置寄存器中設置防抖時間參數,并在程序中讀取這些參數來實現。

5. 結合硬件消抖電路

雖然軟件消抖在FPGA中是一種常用且有效的方法,但在某些對穩定性和實時性要求極高的應用中,可能還需要結合硬件消抖電路來提高性能。硬件消抖電路可以通過物理方式(如RC電路)來減少按鍵抖動對系統的影響,與軟件消抖相輔相成,共同提高系統的穩定性和可靠性。

6. 進行充分的仿真和測試

在FPGA設計完成后,需要進行充分的仿真和測試來驗證按鍵消抖功能的有效性。仿真可以幫助設計師在實際硬件部署之前發現潛在的問題,并對其進行優化。測試則需要在實際硬件上進行,以確保設計在實際應用中能夠滿足性能要求。

五、總結

在FPGA中實現按鍵消抖是一個涉及硬件設計和軟件編程的復雜過程。通過選擇合適的消抖方法、優化設計細節、增加防抖時間可調節性、結合硬件消抖電路以及進行充分的仿真和測試,可以設計出穩定可靠的按鍵消抖系統。這不僅可以提高FPGA系統的用戶體驗,還可以確保系統在各種惡劣環境下的穩定運行。

-

FPGA

+關注

關注

1637文章

21841瀏覽量

608516 -

計數器

+關注

關注

32文章

2278瀏覽量

95448 -

按鍵消抖

+關注

關注

2文章

27瀏覽量

10527

發布評論請先 登錄

相關推薦

按鍵消抖電路的實現方式

VHDL—按鍵消抖

vhdl按鍵消抖程序(七種方式實現按鍵消抖)

STM單片機中的按鍵消抖和FPGA消抖

FPGA內實現按鍵消抖的方法

基于FPGA實現按鍵消抖處理

如何在FPGA中實現按鍵消抖

如何在FPGA中實現按鍵消抖

評論