1. 什么是I/O Tile?

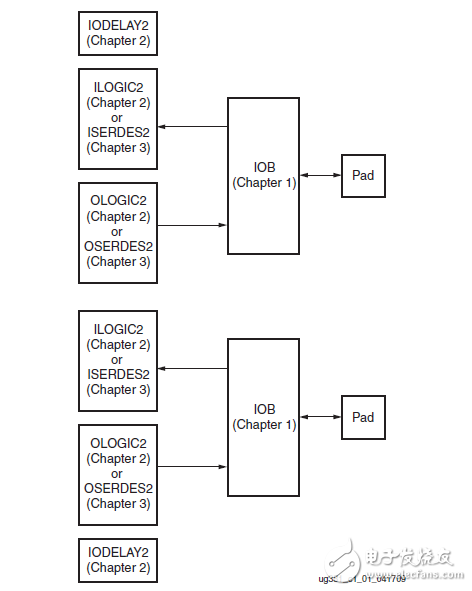

對Spartan-6系列FPGA來說,一個IO Tile包括2個IOB、2個ILOGIC、2個OLOGIC、2個IODELAY。

圖 1Spartan-6系列IO Tile結構圖

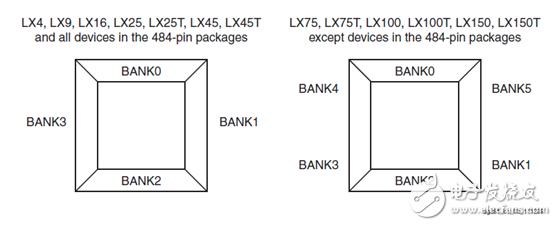

圖 2Spartan-6 FPGA I/O Banks

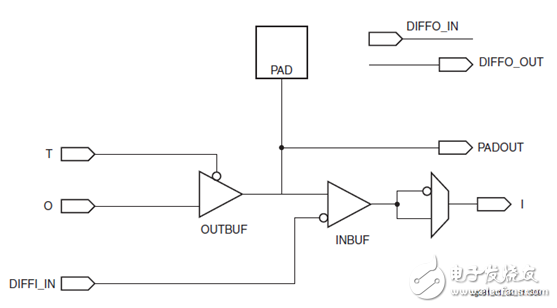

1.1. IOB結構介紹

每個IOB包含了輸入、輸出、三態驅動器;這些驅動器可以配置為不同的電平標準如LVTTL、LVCMOS等;差分IO會用到1個IO Tile里的兩個IOB。

每個IOB都被直接連接到了ILOGIC和OLOGIC,ILOGIC和OLOGIC可以被配置成ISERDES或OSERDES,。

圖 3基本IOB結構圖

1.1.1. IOB內部終端電阻

高速IO電平標準的使用可以優化電平轉換特性和信號完整性,在高速IO電平標準中往往需要使用終端電阻。終端電阻的位置應該距離接收器越近越好。

Spartan-6 FPGA為差分IO和單端IO提供了片內終端電阻,這個終端電阻位于IOB內部,使用這些終端電阻,可以避免FPGA外部再引腳處再接電阻。

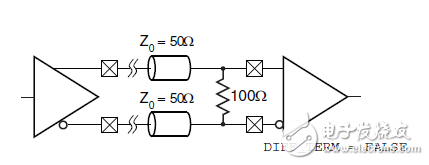

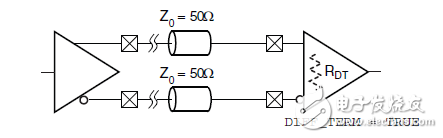

差分IO的終端電阻

Spartan-6系列為差分IO提供了100Ω的終端電阻,差分引腳的終端電阻可以通過約束文件使之使能或不使能。

圖 4差分引腳使能終端電阻

圖 5差分引腳不使能終端電阻

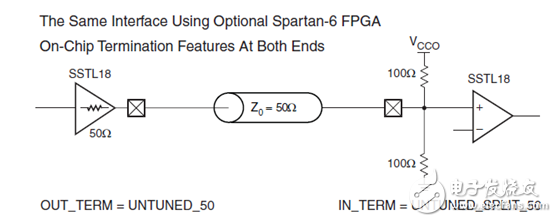

單端引腳終端電阻

單端引腳的輸入終端電阻和輸出阻抗都是可編程控制的,如下圖所示:左邊FPGA的輸出使能了50Ω的輸出阻抗,右邊的FPGA使能了輸入50%分壓電阻;在高速接口應用中,使能輸出阻抗可以減少電磁反射,Spartan-6系列FPGA輸出阻抗可選值為None、25Ω、50Ω、75Ω;輸入阻抗可設置為25%、50%、75%分壓。

圖 6單向SSTL接口使用片上終端電阻

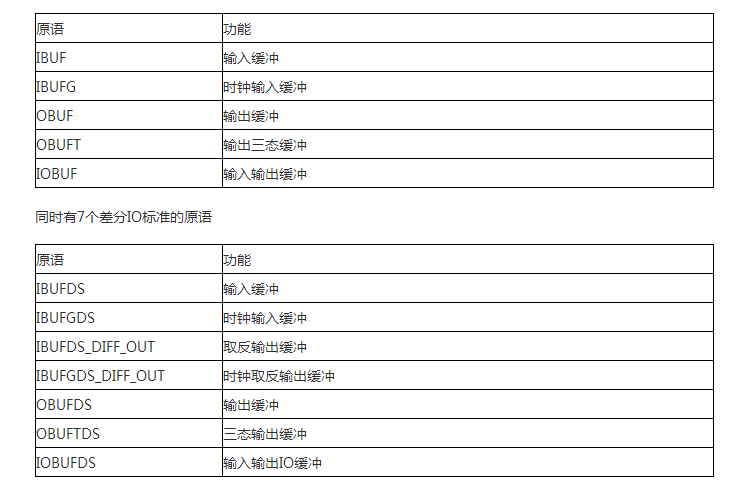

1.1.2. IOB內部可例化的原語

IOB內部有多種輸入輸出緩沖資源(buffer resource),他們可以原語的形式調用,在Spartan-6系列里,單端IO標準的原語如下5個:

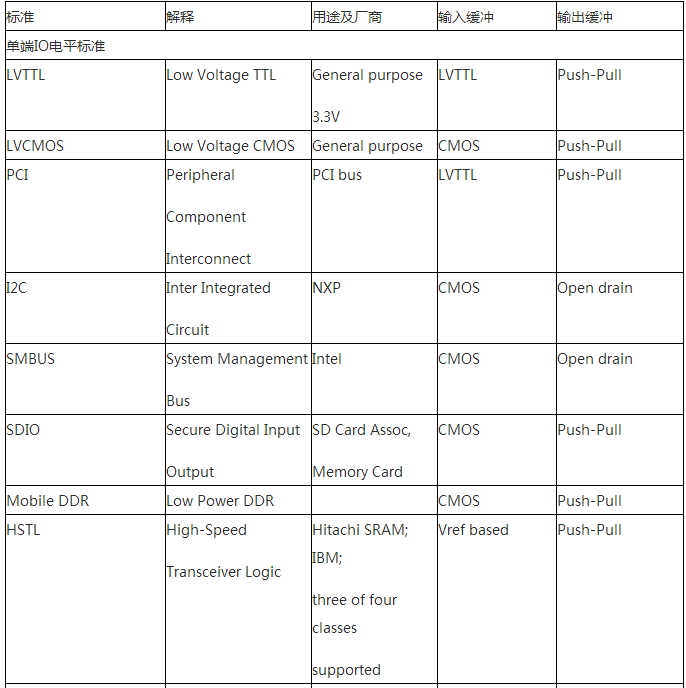

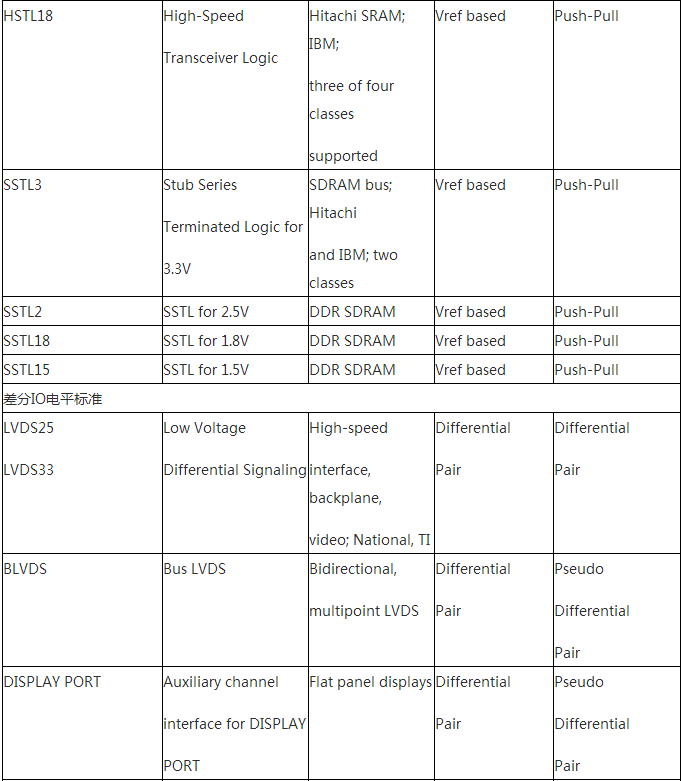

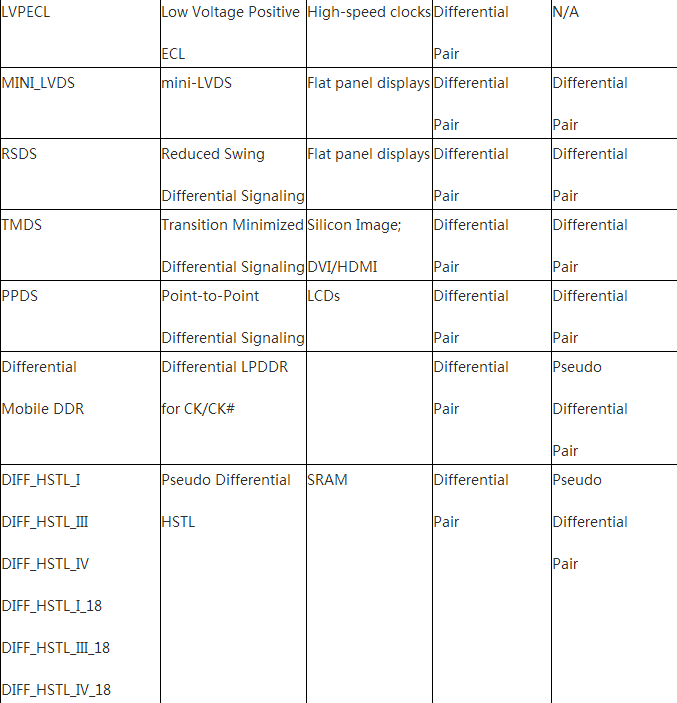

1.1.3. IOB內可用IO電平標準

IOB支持多種電平標準,用戶可以自由靈活地為自己的設計選擇合適的IO電平標準,Spartan-6系列支持的IO電平標準如下

1.1.4. FPGA配置后未使用引腳狀態/strong》

在默認情況下,在FPGA配置完成后,所有未使用的引腳將被配置成輸入,并在IOB內部經下拉電阻接地,這種未使用引腳在配置后的狀態可以通過UnusedPin BitGen option進行設定。

1.2. SelectIO 的邏輯資源

SelectIO的邏輯資源包括基本資源和高級資源,其中,基本資源包括:

Combinatorial input/output,組合輸入/輸出

3-state output control,三態輸出控制

Registered input/output,寄存器輸入輸出

Registered 3-state output control,寄存器三態輸出控制

Double Data Rate (DDR) input/output,雙倍數據率輸入輸出

DDR output 3-state control,雙倍數據率三態輸出控制

高級資源包括:

IODELAY2,為用戶提供精準的延時控制

NONE, C0, and C1 output DDR mode,輸出雙倍數據輸出

NONE, C0, and C1 input DDR mode,輸入雙倍數據輸入

ISERDES,輸入串并轉換

OSERDES,輸出并串轉換

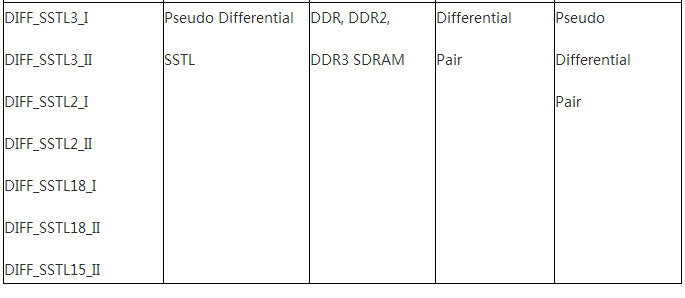

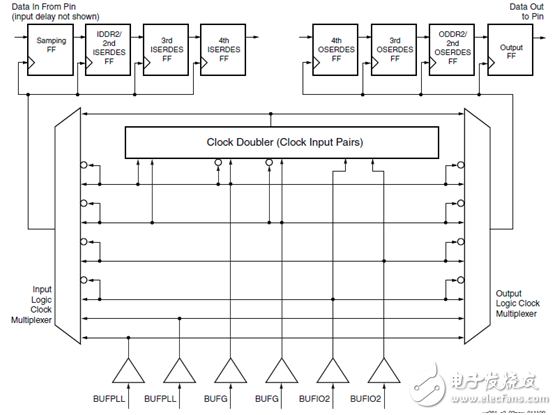

selectIOn邏輯資源被組合在一個IO Tile內部,如下圖所示,在單端模式中,master I/O buffer驅動P Pad,slave I/O buffer驅動N Pad;在差分模式中,master I/O buffer和slave I/O buffer組合起來使用,可以完成串并或者并串轉換。

圖 7一個I/OTile里的selectIO邏輯資源

1.3. Selection資源中可用的時鐘資源

所有IO的數據采集和轉換(包括串并轉換和并串轉換)、DDR傳輸等都需要一個內部SDR時鐘,為了實現這些功能,I/O接口Tile需要一個本地的時鐘倍頻器來獲取SDR時鐘。

進行DDR傳輸的倍頻器需要兩個輸入時鐘,這兩個輸入時鐘必須是下面三種情況之一:

一個全局時鐘和它的局部(IO接口資源里)取反時鐘

兩個相位相差180°的全局時鐘

兩個相位相差180°的I/O時鐘

圖 8IO接口邏輯的時鐘資源

-

Spartan-6

+關注

關注

4文章

38瀏覽量

17562

發布評論請先 登錄

相關推薦

Spartan-6的QDR接口能連接到MCB引腳嗎

請問IO標準是否與Spartan-6上的SLVS-200兼容?

賽靈思宣布Spartan-6 FPGA系列兼容PCI Exp

Spartan-6 FPGA工業影像目標設計平臺(Xilin

基于Spartan-6的FPGA SP601開發設計方案

Xilinx Spartan6 IO 電平讀書筆記

Spartan-6 FPGA的時鐘資源及結構介紹

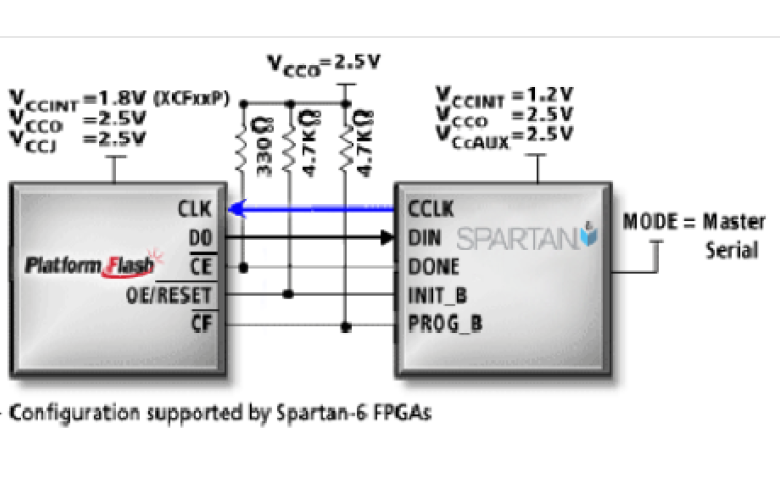

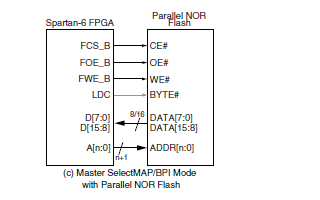

Spartan-6 FPGA Configuration User Guide

滿足 Xilinx Spartan-6 和 Virtex-6 系列的功耗要求

Xilinx Spartan-6系列封裝概述和管腳分配

Spartan-6 FPGA中的DCM功能介紹

Spartan-6 FPGA的配置教程說明

Spartan-6系列FPGA的詳細資料概述

一文詳解Spartan-6系列IO Tile結構

一文詳解Spartan-6系列IO Tile結構

評論