背景

在高速電路設計與測試領域,S參數(散射參數)扮演著至關重要的角色。然而,由于實際測試環境中存在的夾具、連接線等非電路元件的影響,直接測量得到的S參數往往無法真實反映電路本身的性能。因此,S參數去嵌技術的出現,為高速電路設計師們提供了一種有效的方法,用于從測量數據中剝離非電路元件的影響,從而獲取更為準確的電路性能參數。

原理分析

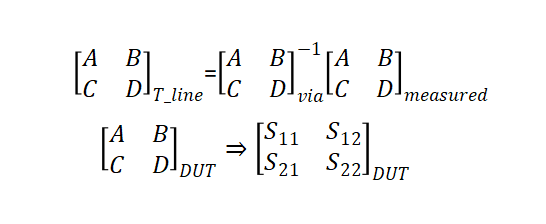

S參數去嵌技術的核心在于通過數學方法,將被測件(DUT)與測試工具組成的復合系統的S參數進行分解,以提取出被測件本身的S參數。這一過程需要深入了解測試夾具的電氣特性,以及其與被測件之間的相互作用。通過精確建模和計算,可以去除夾具對測量結果的影響,得到更為接近真實情況的電路性能參數。

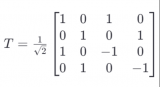

在S參數去嵌的過程中,選擇合適的去嵌方法和算法至關重要。目前,常用的去嵌方法包括開路-短路去嵌法、負載線去嵌法等。這些方法的基本原理是通過在測試電路中引入已知特性的元件(如開路、短路或特定負載),從而得到與測試相關的S參數。例如C的拓撲由A和B組成,通過乘以逆矩陣的操作,在C的總體的A參數左邊乘以一個過孔的A參數的逆矩陣就可以得到真正的傳輸線的A參數,最后再轉換回S參數。

發展與挑戰

在高速電路設計中,S參數去嵌技術的應用范圍廣泛。無論是對于單個元件的性能評估,還是對于復雜電路系統的優化設計,S參數去嵌都能提供更為準確和可靠的數據支持。通過去嵌處理后的S參數,設計師們可以更加精確地了解電路的性能特性,如傳輸損耗、反射系數、串擾等,從而進行更為有效的優化和設計。

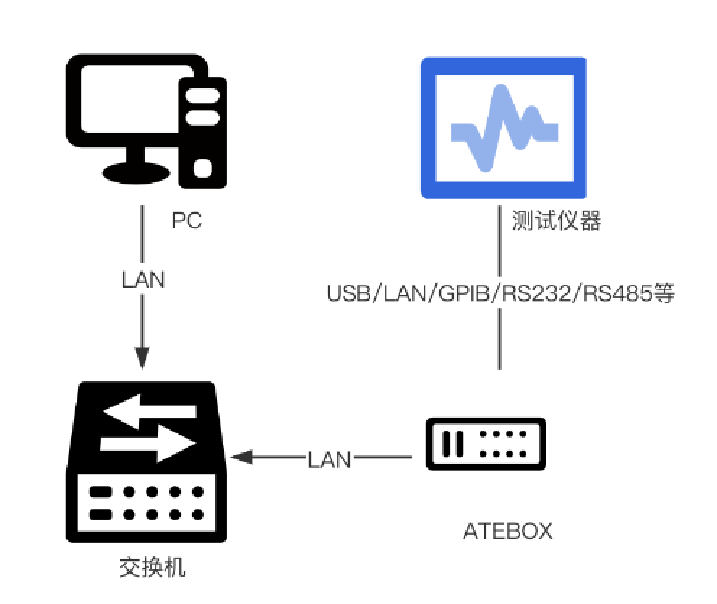

值得一提的是,隨著計算機技術不斷發展,基于軟件的S參數去嵌工具也日益成熟。這些工具能夠自動化地完成去嵌過程,大大提高工作效率和精度。同時,一些先進的去嵌算法和技術的出現,也為S參數去嵌技術的發展注入了新的活力。

然而,盡管S參數去嵌技術在高速電路設計中取得了顯著的進展,但仍存在一些挑戰和待解決的問題。例如,對于復雜的多端口電路系統,如何準確地進行去嵌處理仍然是一個難題。此外,隨著電路工作頻率的不斷提高,對去嵌技術的精度和速度也提出了更高的要求。

SIDesigner 仿真實例

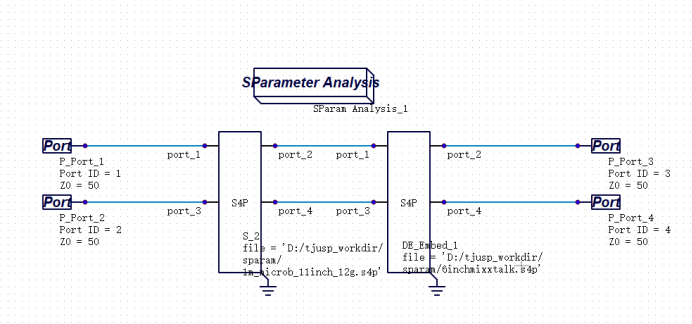

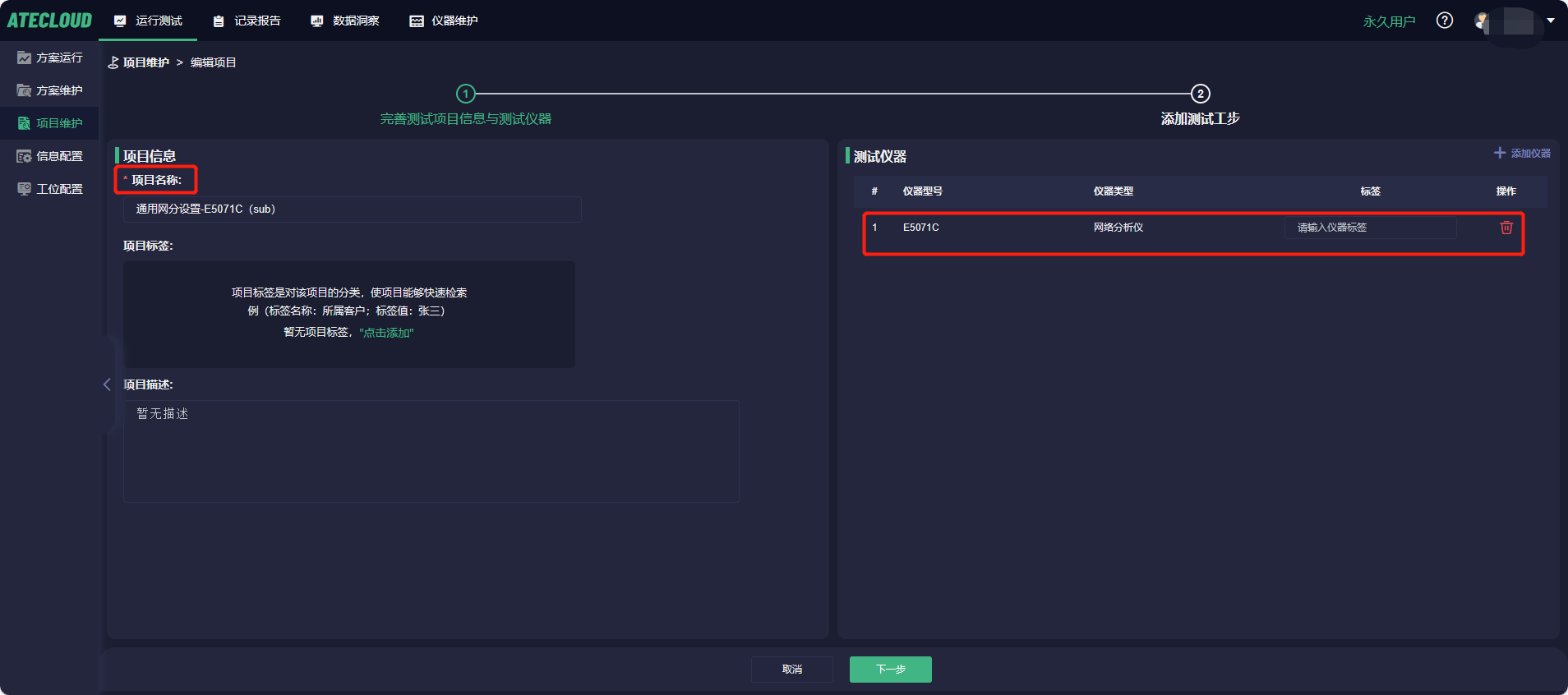

巨霖的SIDesigner提供了DE_Embed器件,可以實現S參數去嵌的功能,能夠精確剝離非電路元件影響,為高速電路設計提供準確數據支持,助力電路性能優化與升級。

(S參數去嵌電路圖)

審核編輯:劉清

-

高速電路

+關注

關注

8文章

159瀏覽量

24258 -

S參數

+關注

關注

2文章

141瀏覽量

46581 -

DUT

+關注

關注

0文章

189瀏覽量

12451

原文標題:S參數去嵌:在高速電路設計與測試中的精確化探索

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

單端S參數到混合模式S參數的仿真與轉換

元器件在電路設計中的重要性

石英晶體振蕩器的振幅條件及其在電路設計中的應用

天線自動測試系統如何自動化測試S參數,評估射頻天線性能?

S參數去嵌:在高速電路設計與測試中的精確化探索

S參數去嵌:在高速電路設計與測試中的精確化探索

評論