2024年3月28日-29日,奇捷科技(Easy-Logic Technology),作為EDA行業邏輯功能變更領域的技術引領者,受邀參加2024國際集成電路展覽會暨研討會(IIC),與來自各地的行業同仁齊聚上海張江科學會堂,共同探討行業發展,分享實戰經驗,獲得了與會者的廣泛關注和認可。

社會數字化轉型與摩爾定律放緩,是EDA與IC設計行業變革的契機,越來越多的系統級企業開始有更迫切、更定制化的芯片設計需求。在IIC上海同期舉辦的“EDA與IC設計論壇”上,奇捷科技CEO魏星博士發表了《如何利用增量式設計(ECO)降本增效》的專題演講,結合實際應用案例分享奇捷科技Function ECO的創新成果及行業干貨。

隨著數字芯片設計規格日趨復雜、產品迭代周期不斷加快,設計過程中難免會出現新的需求、發現新的錯誤,如何保證項目在出現這些意外的情況下仍然能使整個項目按計劃時間完成,已經成為眾多芯片設計公司的極大痛點,而這個問題則可以通過增量式設計來解決,業內通常把這種解決方式稱之為ECO。

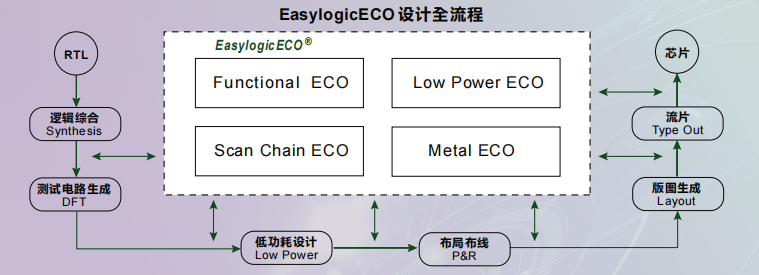

據魏星博士介紹,ECO是一種快速變更ASIC電路功能的設計方法,其通過在當前電路中增加一個很小的補丁邏輯的方法對電路進行邏輯功能變更,從而避免對電路進行完全重新設計。與動輒需要幾個月時間的重新設計相比,Function ECO可以確保項目周期,避免項目交付大幅延期從而造成各種不可預估的損失。

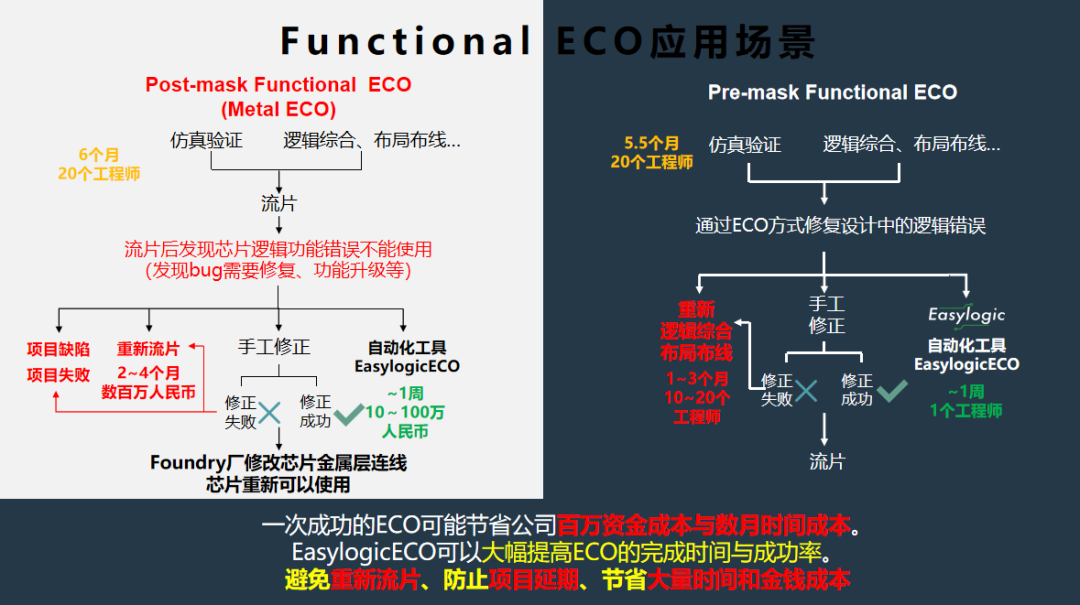

魏星博士在演講中介紹到,增量式設計流程有兩種應用場景,一種是改版升級場景,流片以后發現芯片邏輯功能錯誤,比如出現bug需要修復,或者有些新的feature想要添加進去,需要改版升級等情況,傳統設計上,我們只能重新設計,這樣會大大延長設計周期,增加設計成本,使用增量式設計流程的方法,可能只需要改動幾根金屬層的連線,從而幫助設計公司節省數月的時間成本及數百萬的資金成本;另外一種是ECO場景,到了項目設計后期,布局布線快要完成,這個時候發現RTL錯誤或者Spec變更,就需要用到ECO的方式修復設計中的邏輯錯誤,防止需要重新進行邏輯綜合和布局布線等,以保證產品在計劃時間內完成。

魏星博士演講中也列舉了一些應用實例,比如在即將Tape-out的設計項目中,發現RTL的變更,乘法器的輸入端邏輯需要進行ECO,乘法器被打散,無法在網表中輕易找到Boundary,使用其他工具或者手工ECO生成補丁太大,奇捷科技EasylogicECO解決方案采用獨特的逆向工程分析技術,從電路中找出被打散的乘法器邊界,配合人工操作,最終只需要增加700邏輯單元,順利完成時序收斂,幫助設計團隊順利完成項目。

總的來說,通過增量式設計流程,可以有效地保障項目進度,拯救已經流片的錯誤芯片,并且無需重新流片即可進行升級換代,所以一次成功的ECO,可以幫助企業節省大量的時間及金錢成本。隨著其重要性越發凸顯,如何搭建一個行之有效的ECO流程也受到越來越多企業的重視,奇捷科技未來也將身體力行,為行業帶來相關規范,幫助各芯片設計公司更精準、更有效率地解決IC設計全流程中各個階段出現的ECO問題,保證項目進度,助力企業降本增效。

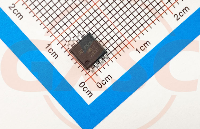

- 展位風采-

展會現場,奇捷科技工作人員與參展嘉賓詳細介紹了EasylogicECO產品功能及優勢,針對不同的業務需求及挑戰進行了深入的探討,吸引了眾多行業內專業人士駐足參觀與交流,讓參觀者更直觀地了解奇捷科技Function ECO解決方案及實際應用案例。

現場提交需求抽取禮品的互動方式,吸引了眾多現場觀展人員的熱情參與,同時我們也利用社交媒體及直播平臺,將展會動態實時分享給無法親臨現場的朋友,線上的觀眾通過評論、點贊、分享及抽獎,參與到和奇捷科技展會的互動當中,通過線上線下的聯動,讓奇捷科技有機會與更多朋友進行分享交流。

此次展會的成功舉辦,奇捷科技向更多客戶展示了其可靠且高效的Function ECO解決方案,也期待未來能與各產業同仁有更多的交流,探索更多的合作可能性,共同推動集成電路設計產業的發展和創新。

-

IC設計

+關注

關注

38文章

1299瀏覽量

104171 -

EDA技術

+關注

關注

12文章

173瀏覽量

36956 -

RTL

+關注

關注

1文章

385瀏覽量

59896

原文標題:IIC現場直擊 | 奇捷科技Function ECO 解決方案助力企業降本增效

文章出處:【微信號:Easy-LogicEDA,微信公眾號:奇捷科技EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

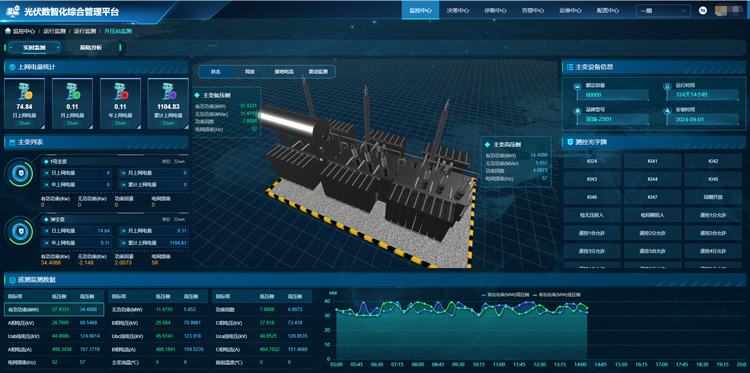

智慧光伏運維管理系統助力光伏運維降本增效

戴爾科技助力企業實現科學的降本增效

谷景電感替代國外品牌電感助力客戶降本增效

谷景電子電感新方案助力電梯行業降本增效

光伏電站智慧運維系統助力光伏電站降本增效

市場解讀 對話展商 磁元件峰會揭秘新能源降本增效秘籍

AR眼鏡:醫藥廠商降本增效新利器

直線電機模組:米思米如何以“磁”之力,引領降本增效新風尚?

隆基分布式光伏電站助力鑄造企業降本增效

無人機智能巡檢系統助力光伏運維降本增效

清遠mes管理系統助力企業降本增效

加速企業云上降本增效,提升性能首選云耀 X 實例

奇捷科技Function ECO解決方案助力企業降本增效

奇捷科技Function ECO解決方案助力企業降本增效

評論