很多同學問DVFS技術怎么實現的,這里小編就和大家掰扯掰扯SoC芯片的DVFS技術吧。

1. DVFS技術介紹

DVFS(Dynamic Voltage and Frequency Scaling)即動態電壓頻率調節技術,是一種高效的低功耗技術,它通過動態調整工作電壓和時鐘頻率,以達到降低功耗的目的。

在CMOS電路中,功耗主要由動態功耗和靜態功耗兩部分組成,而DVFS技術主要通過調整這兩部分來實現功耗的降低。

2. 動態功耗與靜態功耗

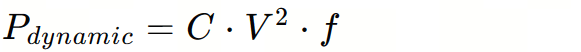

在CMOS電路中,動態功耗由以下公式給出:

其中,C 代表負載電容的容值,V 是工作電壓,f 為工作頻率。從公式可以看出,動態功耗與電壓的平方和頻率成正比。因此,通過降低電壓和頻率可以有效減少動態功耗。

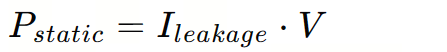

靜態功耗主要由漏電流引起,可以用以下公式表示:

其中,I 是漏電流,V 是工作電壓。由于靜態功耗與電壓成正比,降低電壓也能顯著減少靜態功耗。

3. DVFS的實現方式

1)電壓

為了實現DVFS,芯片的電源模塊需要能夠提供多級輸出電壓,通常是通過多個不同輸出電壓的LDO(Low Dropout Regulator)和選擇開關來實現。DVFS控制邏輯會輸出控制向量以選擇所需的電壓,電源管理模塊會自動完成電壓源的切換。

2)時鐘

時鐘頻率的控制則是通過集成在芯片內部的CGU(Clock Generator Unit)來實現,它可以為系統提供特定頻率的時鐘信號,對時鐘源進行分頻或升頻。

DVFS技術的實現主要依賴于對工作電壓和頻率的動態調整。具體來說,可以通過以下兩種方式實現:

DVS (Dynamic Voltage Scaling): 通過固定電壓-頻率對應點來調節電壓,適用于對性能要求較為穩定的應用場景。

AVS (Adaptive Voltage Scaling): 能夠在一定范圍內自由調節電壓數值,適用于對性能要求更為靈活的應用場景。

4. DVFS的挑戰與策略

在實際應用中,DVFS技術面臨著一些挑戰,主要包括:

時序收斂: 由于電壓和頻率的變化,需要在多個工作模式和條件下進行時序收斂,增加了設計的復雜度。

工作負載預測: 為了有效降低功耗,需要準確預測未來的工作負載,選擇合適的供電電壓和時鐘頻率。

針對這些挑戰,可以采取以下策略:

負載模型: 在一個時間窗口內統計模塊工作的時間長度,并設定不同閾值,以觸發DVFS轉換。就是工作負載的粗略模型可以通過在一個時間窗口內統計模塊工作的時間長度來建立,并設定不同的閾值。高閾值對應高電壓高頻率,低閾值對應低電壓低頻率。每當統計值穿過閾值邊界時,就會觸發DVFS的轉換。

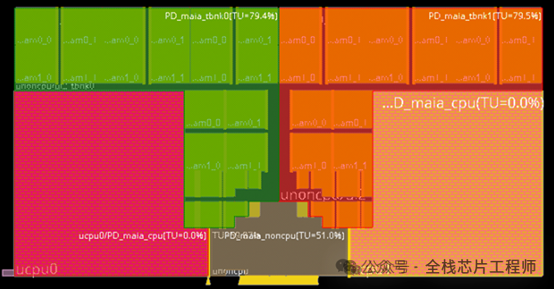

在實際的系統中,每個CPU或DSP可能有自己的獨立DVFS調節系統,因此可以根據本模塊的特點制定出更精確的負載模型,以取得更優的功耗表現。

調節順序: 安全的調節機制是,提升功率時先提升電壓再提升頻率,降低功率時先降低頻率再降低電壓。

在當前的芯片實現工藝下,更高的頻率通常需要更高的供電電壓。這是因為更高的頻率意味著動態功率消耗的增加,而更高的供電電壓可以提供更大的電源功率以滿足需求。因此,再次強調,安全的調節機制是:

當需要提升功率時,應先提升供電電壓,然后提升時鐘頻率。

當需要降低功率時,應先降低時鐘頻率,再降低供電電壓。

調節算法可以是軟件實現,也可以是硬件實現,具體取決于資源消耗情況和DVFS響應時間的要求。

5. 總結

DVFS技術是數字后端設計中重要的低功耗技術之一。通過動態調整工作電壓和頻率,可以有效降低芯片的功耗,延長設備的使用壽命,并減少能源消耗。然而,DVFS技術的實施需要克服時序收斂的復雜性和工作負載預測的準確性等挑戰。通過合理的策略和精確的控制,DVFS技術能夠在保證性能的同時,實現功耗的優化。

審核編輯:黃飛

-

芯片

+關注

關注

456文章

51155瀏覽量

426302 -

soc

+關注

關注

38文章

4199瀏覽量

218814 -

CMOS電路

+關注

關注

0文章

49瀏覽量

11579 -

DVFS

+關注

關注

1文章

18瀏覽量

12021

原文標題:SoC芯片的DVFS技術詳解

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺析SoC芯片的DVFS技術

淺析SoC芯片的DVFS技術

評論