一、寄生效應

定義:

在非理想狀態下設計中不希望存在的,有物質本身特性,或物質與物質間相互作用,在特定條件下所產生的新特性。

這些特性在版圖中形成虛擬的器件,有部分或全部真實器件的功能和特點。

在電路圖中不存在,但在layout中卻相當真實存在,會影響芯片性能

寄生效應器件體現:

寄生電容,寄生電阻,寄生mos管,寄生二極管,寄生三極管,寄生電感

作用:

大部分不希望有;無法準確代入電路仿真中,造成設計上誤差。

同時會對芯片的安全性產生危害,漏電,latchup等

二、寄生電容及版圖抗干擾設計

定義:

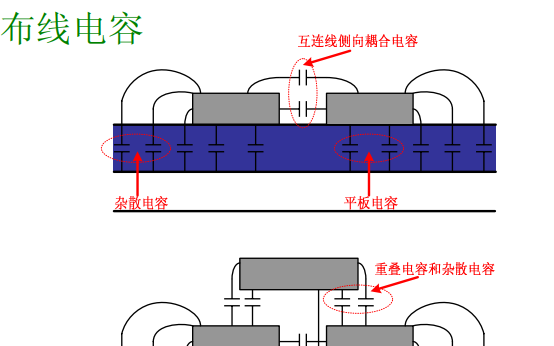

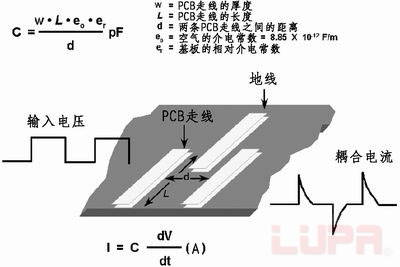

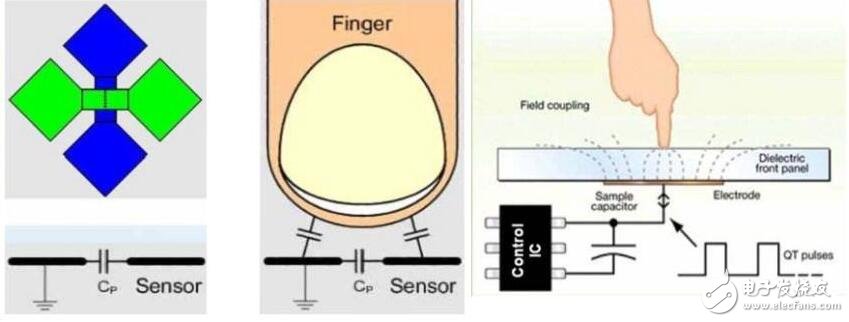

任何兩個導體間只要存在介質(任何兩個非絕緣體層次之間)都會產生寄生電容

工作原理:

電容器工作原理是電荷在電場中會受力而移動,當導體之間有了介質,則阻礙了電荷移動。

而使得電荷積累在導體上,造成電荷的積累儲存。

當A信號產生波動時,通過電容c會帶動信號b一起波動,為耦合。

同樣電容c的電荷積累會減緩信號a的突然變化,如果b信號接的是一個恒定的牢固的電位時,就會對a信號濾波。

ps:

經常采用電源和地線并排或重疊走線的好處就是電源地線之間的寄生電容有一定濾波作用。

這也是在電源和重要信號上掛到地的電容的原因。(濾波和穩壓)

種類:

1.metal相關的:metal-metal,metal-poly(影響背柵電壓,進而影響Ⅴth) ,metal和源漏十襯底(也有應力作用)

2.poly相關的:poly一poly,poly和源、漏(pmos可能截止,nmos可能漏電),poly和襯底

3.和襯底、阱相關的:源、漏和襯底,阱和阱(忽略)

寄生電容值大小的決定因素:

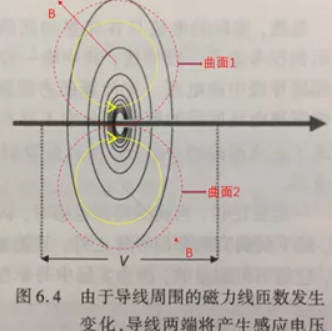

C=εs/4πKd

電容上下極之間距離對電容值的影響:

電容的上下極板間距越大,電容值越小

2.絕緣體電解質常數對電容值的影響:

由工藝決定,版圖無法改變,不用考慮

3.上下極板覆蓋面積對電容值影響:

覆蓋面積越大,電容越大;周長越長,電容值越大

4.電容連接方式對電容值影響:

串聯的總電容值比串聯電路中最小的那個電容的容值小(高速,PR項目里減小寄生電容的重要方法)。

并聯的電容容值為電容之和

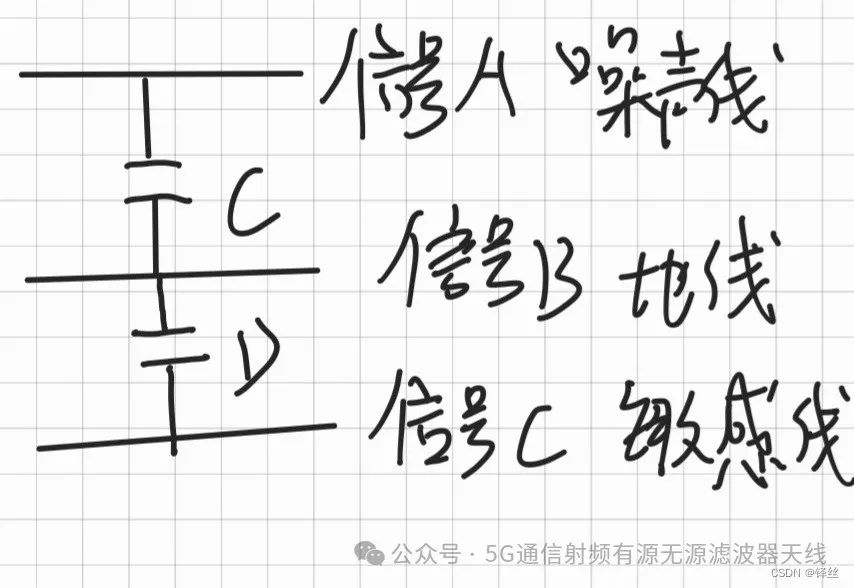

1.metal相關的寄生電容的版圖抗干擾處理:

⑴ metal一metal寄生電容抗干擾設計

①在噪聲metal和敏感metal兩邊用接地的metal進行隔離(這種方法叫shielding,gnd采用干凈的gnd,盡量不與其他模板共用,可用信號本身模塊的gnd)

在噪聲信號兩邊用接地metal隔離,可以有效防止噪聲信號通過寄生電容將噪聲傳遞出去

上圖噪聲線a的波動很難拉動b地線,就算拉動了b,也是頻率和幅度都大幅度消減的噪聲。在通過寄生電容D耦合到信號C上噪聲就更小了

②拉開噪聲metal和敏感metal的間距

如果兩個metal有很長一段平行走線,長長的橫截面平行就會有一個比較大的寄生電容。

就算中間有用接gnd的metal進行隔離,噪聲也一定程度的耦合到敏感線上,

所以最好的處理方式是在有屏蔽線的基礎上拉開間距,最好不要有平行走線

如果一定要平行總線,可選擇把噪聲線選擇用較高層次的線,采用不同層次走法來拉開間距

③全方位屏蔽法

對于高要求的信號屏蔽,可用上下左右四個方向進行gnd線隔離

④對于高速,RF信號,減少寄生電容的影響只有一種,采用高層metal,拉開間距。

對這些信號而言,不要任何寄生電容

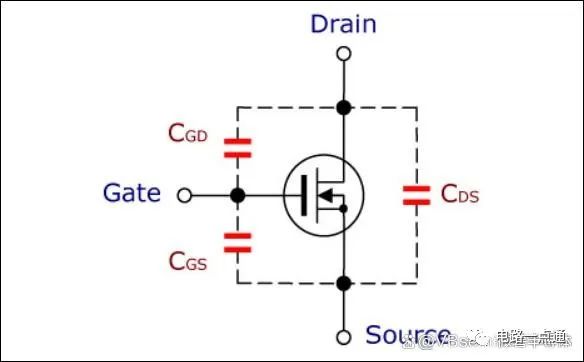

⑵ metal和poly Metal和源漏十襯底

Metal如果在管子溝道上走過,就會通過寄生電容影響gate電壓,同時和襯底的寄生電容對溝道反型產生影響,影響閾值電壓,進而影響D端的信號輸出。

同時metal壓在管子上也會引入不均勻的應力,降低管子的匹配性

2.襯底相關的寄生電容的版圖抗干擾處理

寄生電容可以把電路1的噪聲耦合到襯底,再通過襯底耦合到電路2中。

這種耦合到襯底的噪聲沒辦法完全避免,只能減少影響

減少襯底噪聲干擾的方法:

①用敏感模塊遠離噪聲模塊, 用間距去削弱噪聲

②把噪聲模塊(敏感模塊)用雙保護環為死,不讓噪聲傳出(入)模塊

③用深N井,NBL工藝物理隔開Psub,不讓噪聲輕易傳到襯底上

★NMELL保護環吸收電子(強),復合空穴(弱)。

Psub保護環吸收空穴(強),復合電子(弱)。

三、寄生電阻及版圖抗干擾設計

定義:

任何導體都存在寄生電阻,金屬,柵,襯底,擴散區,都存在寄生電阻

影響:

一般我們的信號傳導兩種信號,電壓(一般連接到gate)或電流(一般連接到源、漏)

傳電壓: 寄生電阻對電壓的影響不大。

∵I=V/R,當寄生電阻大的時候,電流就會小。

電流小,將gate電荷移走的時間就長(t=Q/I),那么gate上的電位由原來的電壓V改變到新電壓V的時間就長,影響管子的開啟速度。

這也就是橫向放置電流鏡為什么不能太長的原因之一;

也是當導線太長會影響電路翻轉,驅動不了管子的原因之一。

2. 當傳導電流時,會在傳導路徑上產生很大的壓降,V=IR,就會影響接下來電路的性能

寄生電阻值大小的決定因素:(通用于正常電容)

電阻值=R=ρ*L/s(w*d)=L/w(方塊數)*R(即ρ/d)(方塊阻值)

1.決定電阻值大小的一個因素是電阻率p(工藝決定,忽略)

2.橫截面越大,方塊電阻值越小;Metal的厚度越厚,方塊電阻越小,所以Top metal的寄生電阻越小

3.方塊數越多,寄生電阻越大。方塊數=線長度L/線的寬度w

4.串聯電阻,電阻值越大;并聯電阻比最小的電阻值還小。

5.接觸孔,通孔電阻;孔的個數越多,電阻越小。

6.任何兩個物質接觸的地方都有接觸電阻(無法計算)

各種電阻值和VIA和metal,poly等的過電流能力:

方塊阻值,孔電阻和過電流能力數據都在design rule或Electrical specifcations文檔里找(電學特性文檔)

降低寄生電阻的版圖處理技巧:

1.加厚,加寬metal:

同層次metal可以通過多根metal并聯的方式加寬metal來降低寄生電阻

不同層次metal相互疊加走線相當于加厚metal

2.特殊的版圖畫法技巧:

①電源地線樹形走線,由一個粗壯的總線,分支出多個較細的總線,一級一級分布就像樹分支一樣

②模塊內電源、地線可以分布成網格狀,多條通路的并聯可以極大降低模塊內部的電源、地的寄生電阻,加大過電流能力。

③將總線用多點,選擇中間位置連接到cell內部,形成網格。

四、寄生mos管及版圖抗干抗設計

形成原理:

如果一個metal穿過兩個nwell之間兩個n+/p+間,metal和襯底的寄生電容會讓襯底反型,形成寄生mos管。

會造成漏電,Latchup等嚴重后果。

★★★在低壓器件中很難形成寄生MOS管。

因為信號的電壓不夠高,無法有足夠的壓差形成反型。

五、二極管及三極管寄生效應

寄生二極管的形成:

任何相互接觸的p和n之間都是存在pn結的,PN結是寄生的二極管

寄生三極管的形成:

任何相互兩個銜接的pn結都是寄生三極管,三極管分pnp和npn(BJT)

審核編輯:劉清

-

三極管

+關注

關注

142文章

3611瀏覽量

121871 -

電容器

+關注

關注

64文章

6217瀏覽量

99534 -

寄生電容

+關注

關注

1文章

292瀏覽量

19225 -

信號輸出

+關注

關注

0文章

43瀏覽量

8482 -

GND

+關注

關注

2文章

539瀏覽量

38696

原文標題:PCB版圖學習一一誰都避不開的寄生效應

文章出處:【微信號:RFfilter,微信公眾號:5G通信射頻有源無源濾波器天線】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB寄生電容的影響 PCB寄生電容計算 PCB寄生電容怎么消除

【高速PCB布線指南(2)】寄生效應

IC工藝和版圖設計的電容版圖設計的詳細中文資料概述

什么是寄生電感_PCB寄生電容和電感計算

什么是寄生電容_寄生電容的危害

MOSFET的寄生電容及其溫度特性

什么是寄生效應?寄生電容及版圖抗干擾設計

什么是寄生效應?寄生電容及版圖抗干擾設計

評論