VLSI設計驗證及其方法的重要性

在 VLSI(超大規模集成)的動態世界中,對創新產品的需求比以往任何時候都更高。從概念到功能齊全的產品的過程涉及許多挑戰和不確定性,其中設計驗證通過確認設計滿足其預期要求和規格,在確保復雜電子系統的功能和可靠性方面發揮著關鍵作用。據 Research and Markets 稱,到 2023 年,全球 VLSI 市場預計價值 6622 億美元。據市場分析師預測,到 2028 年,其價值將達到 9717.1 億美元,復合年增長率 (CAGR) 為 8%。

在本文中,我們將探討設計驗證的概念、其重要性、涉及的過程、使用的語言和方法,以及超大規模集成電路設計發展中這一關鍵階段的未來前景。

什么是設計驗證及其重要性?

設計驗證是一個系統化的過程,用于驗證和確認設計滿足其指定的要求并遵守設計指南。這是產品開發周期中至關重要的一步,旨在及早發現并糾正設計問題,以避免在開發后期階段進行成本高昂且耗時的返工。設計驗證可確保最終產品,無論是集成電路 (IC)、片上系統 (SoC) 還是任何電子系統,都能正確可靠地運行。 SoC 和 ASIC 驗證在實現可靠和高性能集成電路方面發揮著關鍵作用。

VLSI設計驗證涉及兩種類型的驗證:

功能驗證

靜態時序分析

這些驗證步驟至關重要,需要在設計的各個階段進行時執行,以確保最終產品滿足預期要求并保持高質量。

功能驗證:

它是 VLSI 設計的關鍵階段,旨在確保在各種操作條件下使用的芯片的正確功能。它涉及測試設計以驗證其行為是否符合預期規格和功能要求。這個驗證階段至關重要,因為超大規模集成電路設計變得越來越復雜,在開發過程中必然會出現人為錯誤或設計缺陷。 VLSI設計中的功能驗證過程如下。

識別和準備:在此階段,確定設計要求并準備驗證計劃。該計劃概述了后續驗證步驟的目的、目標和策略。

規劃:驗證計劃準備好后,規劃階段涉及資源分配、設置測試環境以及創建測試用例和測試平臺。

開發:開發階段的重點是使用適當的語言和方法對測試平臺和測試用例進行編碼。此階段還包括構建和集成模擬和仿真環境,以促進徹底的測試。

執行:在執行階段,測試用例在設計上運行以驗證其功能和性能。這通常涉及廣泛的模擬和仿真器以涵蓋所有可能的場景。

報告:最后,驗證過程以生成詳細報告結束,包括錯誤報告、覆蓋率統計數據和總體驗證狀態。這些報告有助于確定需要改進的領域,并為未來的設計迭代提供有價值的見解。

靜態時序分析(STA):

靜態時序分析是 VLSI 設計中的另一個關鍵步驟,重點是驗證設計的時序要求。在 VLSI 設計中,時序至關重要,因為它決定信號如何在芯片中傳播并影響集成電路的整體性能和功能。該過程用于確定設計中最壞情況和最佳情況的信號傳播延遲。它分析從源(輸入)到目的地(輸出)的時序路徑,并確保信號在所需的時鐘周期內到達預期目的地,而不違反任何時序約束。在 STA 期間,設計被劃分為時間路徑,以便可以執行時序分析。每個時間路徑由以下因素組成。

起始點:時序路由的起始點是數據由時鐘邊沿啟動或需要在特定時間準備就緒的位置。每個起始點必須有一個寄存器時鐘引腳或輸入端口。

組合邏輯網絡:它包含沒有內部存儲器的部分。組合邏輯可以使用 AND、OR、XOR 和反相器元件,但不能使用觸發器、鎖存器、寄存器或 RAM。

端點:這是當時鐘邊沿捕獲數據或必須在特定時間提供數據時時序路徑結束的位置。每個端點必須有一個輸出端口或一個用于寄存器數據輸入的引腳。

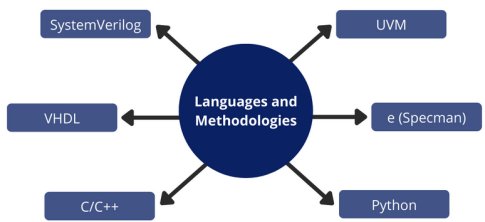

設計驗證中使用的語言和方法

設計驗證采用各種語言和方法來有效測試和驗證 VLSI 設計。

SystemVerilog (SV) 驗證:SV 提供了一組廣泛的驗證功能,包括面向對象編程、約束隨機測試和功能覆蓋。

通用驗證方法 (UVM):UVM 是一種基于 SystemVerilog 構建的標準化方法,可實現可擴展和可重用的驗證環境,從而提高設計驗證的效率和靈活性。

VHDL(VHSIC硬件描述語言):VHDL廣泛用于超大規模集成電路行業的設計輸入和驗證,為硬件建模、仿真和綜合提供強有力的支持。

e(Specman):e是Yoav Hollander為其Specman軟件開發的驗證語言,提供強大的驗證功能,例如約束驅動的隨機測試和事務級建模。后來更名為 Verisity,并被 Cadence Design Systems 收購。

C/C++ 和 Python:這些編程語言通常用于構建驗證框架、測試平臺和基于腳本的驗證流程。

VLSI設計驗證和方法

設計驗證的優點

有效的設計驗證為超大規模集成電路行業提供了眾多優勢。

它縮短了 VLSI 產品的上市時間

該過程確保符合設計規范

它增強了設計對不確定性的適應能力

驗證可最大限度地降低與設計失敗相關的風險

設計驗證的未來

設計驗證的未來看起來充滿希望。人工智能和機器學習輔助驗證的新方法正在出現,以有效解決驗證挑戰。采用先進的驗證工具和方法將對提高驗證過程的效率、有效性和覆蓋范圍發揮重要作用。此外,隨著SoC、ASIC和低功耗設計的發展,對專業VLSI驗證的需求將持續上升。

設計驗證是產品開發過程中不可或缺的一部分,可確保可靠性、功能和性能。設計驗證采用各種語言、方法和技術來解決復雜設計和新興技術帶來的挑戰。隨著技術格局的發展,設計驗證將繼續在提供創新且可靠的產品以滿足不斷變化的世界的需求方面發揮至關重要的作用。

審核編輯 黃宇

-

芯片

+關注

關注

456文章

51140瀏覽量

426149 -

VLSI

+關注

關注

0文章

73瀏覽量

42952

發布評論請先 登錄

相關推薦

晶圓制造recipe(工藝配方)的定義、重要性、種類及構建和驗證方式

選擇正版SolidWorks的重要性及如何避免盜版風險

凱迪正大分享電纜交流電壓檢測的試驗方法及其重要性

IO模塊的作用及其在工業生產中的重要性

武漢凱迪正大享電纜耐壓性檢測:內容、標準與重要性

PLC的I/O模塊的作用及其重要性

AC/DC電源模塊的原理、特點以及其在實際應用中的重要性

VLSI設計驗證及其方法的重要性

VLSI設計驗證及其方法的重要性

評論