使用D觸發(fā)器的移位寄存器

D觸發(fā)器的移位寄存器是一種重要的數(shù)字系統(tǒng)和計算機中應(yīng)用很廣泛的基本邏輯部件,它不只可以寄存數(shù)碼,而且在移位脈沖的作用下,可以根據(jù)需要使寄存器中的數(shù)碼向左或向右移動。具體來說,移位寄存器是由多個D觸發(fā)器構(gòu)成的,每個觸發(fā)器可以存儲一位數(shù)據(jù),因此對于n位移位寄存器,就需要n個觸發(fā)器。

根據(jù)具體的設(shè)計需求,移位寄存器可以實現(xiàn)不同的功能。例如,當(dāng)要求上升沿觸發(fā),具有異步復(fù)位功能時,可以在Logisim中構(gòu)建由4個D觸發(fā)器構(gòu)成的右移移位寄存器。此外,如果需要實現(xiàn)數(shù)據(jù)的并行輸入或串行輸入和串行輸出或并行輸出,也可以在設(shè)計時進(jìn)行相應(yīng)的調(diào)整。

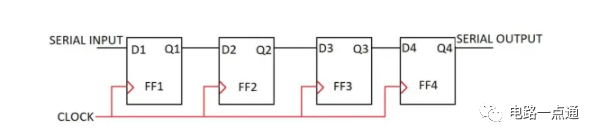

使用 D 觸發(fā)器的串行輸入串行輸出移位寄存器

在這種類型的寄存器中,輸入是一次一位串行,輸出也是串行一位。

帶D觸發(fā)器的串行輸入串行輸出移位寄存器設(shè)計

每個觸發(fā)器一次只能存儲一位,因此對于 4 位移位寄存器,需要四個觸發(fā)器。如上所示,串行數(shù)據(jù)通過第一個觸發(fā)器的 D 應(yīng)用到所有剩余的觸發(fā)器。當(dāng)一系列數(shù)據(jù)輸入寄存器時,每一位都隨著時鐘脈沖的每個正沿提供給下一個觸發(fā)器,并且隨著每個時鐘脈沖,串行數(shù)據(jù)從一個觸發(fā)器移動到下一個觸發(fā)器。

8位寄存器D觸發(fā)器

8位寄存器D觸發(fā)器是一種重要的數(shù)字系統(tǒng)和計算機中應(yīng)用廣泛的基本邏輯部件,它由8個D觸發(fā)器構(gòu)成,每個觸發(fā)器可以存儲一位數(shù)據(jù)。在具體的設(shè)計中,D7—D0為寄存器的輸入,q7—q0為寄存器的輸出,cp則是寄存器的時鐘脈沖。

根據(jù)具體的設(shè)計需求,這種8位的寄存器D觸發(fā)器可以實現(xiàn)不同的功能。例如,可以通過調(diào)用寫好的D觸發(fā)器來構(gòu)建一個寄存器,并通過一個頂層模塊將整體穿起來,實現(xiàn)所需的功能。此外,如果需要實現(xiàn)數(shù)據(jù)的并行輸入或串行輸入和串行輸出或并行輸出,也可以在設(shè)計時進(jìn)行相應(yīng)的調(diào)整。

8位寄存器可以設(shè)計一個8D觸發(fā)器。

用D觸發(fā)器設(shè)計的8位通用移位寄存器示意圖

使用D觸發(fā)器的3位同步計數(shù)器

三位同步計數(shù)器是一種數(shù)字電路,它利用D觸發(fā)器和適當(dāng)?shù)倪壿嬮T電路來實現(xiàn)同步加法計數(shù)的功能。這種計數(shù)器的工作原理是通過三個D觸發(fā)器進(jìn)行級聯(lián)連接,每個D觸發(fā)器代表一個二進(jìn)制位。當(dāng)時鐘信號到來時,首先將輸入的值加1,將其結(jié)果通過邏輯門傳遞給相鄰的D觸發(fā)器,同時也將時鐘信號傳遞給下一個級聯(lián)的D觸發(fā)器,以確保計數(shù)器的同步性。

在設(shè)計上,可以將這三個D觸發(fā)器的輸出端連接到一個3位數(shù)碼管顯示計數(shù)結(jié)果。此外,如果需要實現(xiàn)數(shù)據(jù)的并行輸入或串行輸入和串行輸出或并行輸出,也可以在設(shè)計時進(jìn)行相應(yīng)的調(diào)整。

用 D 觸發(fā)器設(shè)計的 3 位二進(jìn)制計數(shù)器示意圖

-

延時電路

+關(guān)注

關(guān)注

8文章

85瀏覽量

47110 -

計數(shù)器

+關(guān)注

關(guān)注

32文章

2261瀏覽量

94878 -

移位寄存器

+關(guān)注

關(guān)注

3文章

259瀏覽量

22316 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

47982 -

時鐘信號

+關(guān)注

關(guān)注

4文章

452瀏覽量

28641

發(fā)布評論請先 登錄

相關(guān)推薦

如何用JK觸發(fā)器構(gòu)成D觸發(fā)器 電路圖

D觸發(fā)器組成T和J-K觸發(fā)器電路圖

J-K觸發(fā)器組成D觸發(fā)器電路圖

rs觸發(fā)器電路圖與rs觸發(fā)器內(nèi)部電路圖

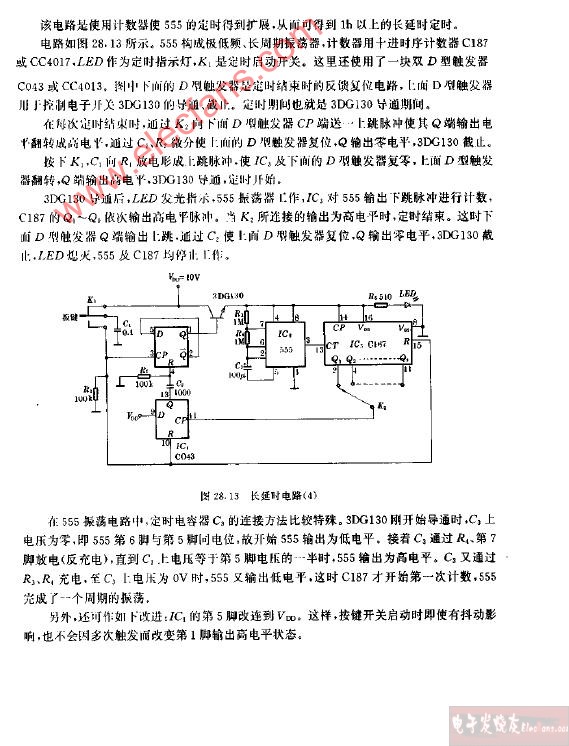

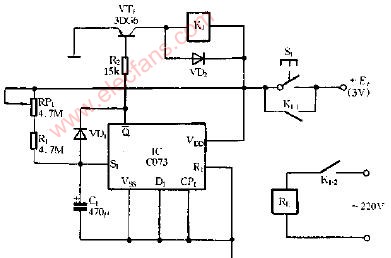

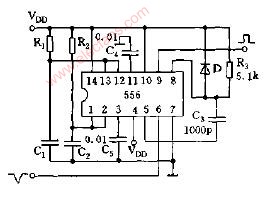

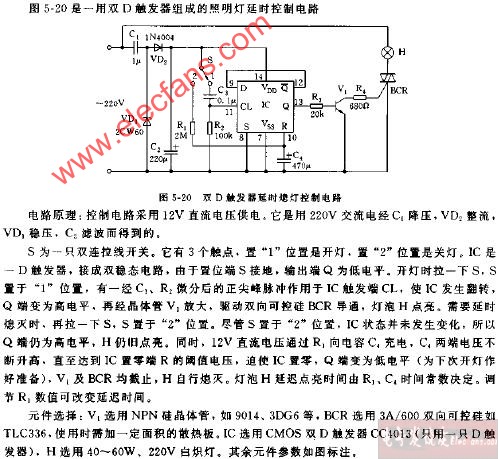

D型觸發(fā)器(延時電路)應(yīng)用電路圖解析

D型觸發(fā)器(延時電路)應(yīng)用電路圖解析

評論