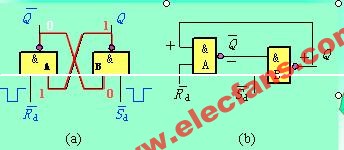

基本的RS(Reset-Set)觸發(fā)器是在數(shù)字電路和計算機(jī)體系結(jié)構(gòu)中使用的一種重要時序電路元件。它由兩個互補的輸入信號,即Reset(復(fù)位)和Set(設(shè)置)構(gòu)成,可以存儲一個比特的二進(jìn)制狀態(tài)。當(dāng)滿足特定條件時,它能夠在兩個穩(wěn)定狀態(tài)之間切換,使得存儲的數(shù)據(jù)可以被更新和控制。在設(shè)計和使用RS觸發(fā)器時,需要遵守一些約束條件。本文將詳細(xì)介紹這些約束條件。

首先要了解的是,RS觸發(fā)器有兩個輸出:一個是Q,表示當(dāng)前存儲的狀態(tài);另一個是Q',表示Q的補碼(即Q取反)。RS觸發(fā)器的狀態(tài)轉(zhuǎn)換是通過輸入信號的變化觸發(fā)的。下面是基本RS觸發(fā)器的真值表:

Reset | Set | Q | Q'

0 | 0 | 0 | 1

0 | 1 | 1 | 0

1 | 0 | 0 | 1

1 | 1 | 0 | 1

從上表可以看出,當(dāng)Reset信號為0且Set信號為0時,輸出Q和Q'保持不變,即記憶狀態(tài)維持不變;當(dāng)Reset信號為0且Set信號為1時,輸出Q變?yōu)?,Q'變?yōu)?,切換至一狀態(tài);當(dāng)Reset信號為1且Set信號為0時,輸出Q和Q'均變?yōu)?,切換至零狀態(tài);當(dāng)Reset信號和Set信號都為1時,輸出Q和Q'均變?yōu)?,無法確定的狀態(tài)。

從上述真值表可以得出RS觸發(fā)器的約束條件如下:

- 輸入信號的禁止?fàn)顟B(tài)約束:當(dāng)Reset信號和Set信號同時為1時,RS觸發(fā)器的行為是未定義的,因此在設(shè)計中應(yīng)避免出現(xiàn)這種情況,確保輸入信號不會同時為1。

- 輸入信號的保持狀態(tài)約束:當(dāng)Reset和Set信號均為0時,RS觸發(fā)器應(yīng)保持原狀態(tài),即輸出Q和Q'應(yīng)保持不變。這意味著,在使用RS觸發(fā)器時,要確保Reset和Set信號不會同時為0。

- 穩(wěn)態(tài)約束:在RS觸發(fā)器的穩(wěn)定狀態(tài)(即輸入信號不變化的情況下),輸出始終保持不變。穩(wěn)態(tài)約束要求在設(shè)計中確保輸入信號在穩(wěn)定狀態(tài)時不會改變。

- 數(shù)據(jù)不同步約束:在RS觸發(fā)器中,當(dāng)Reset信號從1變?yōu)?時,輸出Q的變化要相對反應(yīng)有延時。同樣地,當(dāng)Set信號從1變?yōu)?時,輸出Q'的變化也有延時。這是因為觸發(fā)器的響應(yīng)時間會導(dǎo)致輸出的變化稍有延遲。在設(shè)計中,要將這一延遲考慮在內(nèi),以確保輸入信號的變化得以正確反映在輸出信號上。

- 輸入信號的冪等性約束:在RS觸發(fā)器中,如果Reset信號為1,無論Set信號為何,輸出始終為0。同樣地,如果Set信號為1,無論Reset信號為何,輸出始終為1。這是觸發(fā)器的特性,可以通過邏輯門電路實現(xiàn)。

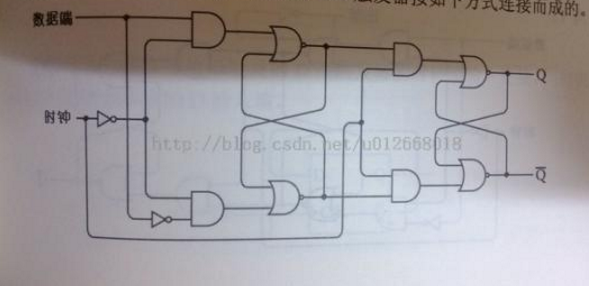

以上是基本RS觸發(fā)器的約束條件。在實際的數(shù)字電路和計算機(jī)體系結(jié)構(gòu)設(shè)計中,RS觸發(fā)器經(jīng)常被使用,而且還有其他類型的觸發(fā)器,如D觸發(fā)器和JK觸發(fā)器,它們有各自的特性和約束條件。

-

存儲

+關(guān)注

關(guān)注

13文章

4317瀏覽量

85869 -

計算機(jī)

+關(guān)注

關(guān)注

19文章

7500瀏覽量

88018 -

RS觸發(fā)器

+關(guān)注

關(guān)注

3文章

101瀏覽量

17947 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1606瀏覽量

80639

發(fā)布評論請先 登錄

相關(guān)推薦

基本RS觸發(fā)器

什么是RS觸發(fā)器,RS觸發(fā)器的工作原理是什么?

帶約束條件的函數(shù)化簡

邊沿觸發(fā)器怎么看

rs觸發(fā)器電路圖與rs觸發(fā)器內(nèi)部電路圖

RS觸發(fā)器的邏輯功能是什么 rs觸發(fā)器的約束條件是什么

RS觸發(fā)器的約束條件

RS觸發(fā)器輸入端約束條件

rs觸發(fā)器工作步驟和約束條件

什么是觸發(fā)器 觸發(fā)器的三種觸發(fā)方式怎么判斷

基本rs觸發(fā)器的約束條件

基本rs觸發(fā)器的約束條件

評論