RS觸發器的邏輯功能是什么

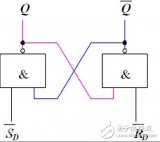

RS觸發器是一種常見的數字邏輯門電路元件,它由兩個相互反饋的邏輯門組成。RS觸發器的邏輯功能可以描述為存儲器元件或雙穩態開關。

RS觸發器有兩個輸入端(R和S)和兩個輸出端(Q和Q‘)。這里的R和S代表“Reset”(復位)和“Set”(置位),它們控制輸出狀態。

以下是RS觸發器的邏輯功能:

1. 當R=S=0時,觸發器保持狀態,不發生變化。輸出Q保持上一個存儲的值。這種狀態稱為“保持”或“無效”狀態。

2. 當R=0、S=1時,觸發器的輸出Q被置為邏輯“0”(低電平)。這稱為“復位”狀態。

3. 當R=1、S=0時,觸發器的輸出Q被置為邏輯“1”(高電平)。這稱為“置位”狀態。

4. 當R=S=1時,觸發器將進入禁止狀態。在禁止狀態下,輸入的改變不產生輸出變化,即狀態保持不變。這種狀態是被禁止的,因為在理想情況下,R和S不應同時為1。

RS觸發器可以實現存儲、復位和置位功能,具有雙穩態特性。它可以用于數字電路中的時序邏輯和存儲器設計。需要注意的是,由于輸入的不確定性和禁止狀態的問題,使用RS觸發器可能引起不穩定的結果,因此通常在實際應用中會使用更可靠的觸發器類型,如D觸發器或JK觸發器。

基本RS觸發器的四種狀態

基本RS觸發器具有四種可能的狀態,這取決于其兩個輸入端(R和S)的邏輯電平,以及初始狀態。以下是基本RS觸發器的四種狀態:

1. 保持狀態(Hold State):當R=0且S=0時,觸發器保持其當前狀態。這種狀態下,輸出保持不變,無論之前的輸入狀態是什么,觸發器的狀態保持不變。

2. 復位狀態(Reset State):當R=0且S=1時,觸發器進入復位狀態。在此狀態下,輸出Q被強制為邏輯低電平(0),而輸出Q’被強制為邏輯高電平(1)。

3. 置位狀態(Set State):當R=1且S=0時,觸發器進入置位狀態。在此狀態下,輸出Q被強制為邏輯高電平(1),而輸出Q‘被強制為邏輯低電平(0)。

4. 禁止狀態(Forbidden State):當R=1且S=1時,觸發器處于禁止狀態。在此狀態下,輸入的變化不會導致輸出的變化。這種狀態應該盡量避免,因為它會導致不可預測的結果。

需要注意的是,禁止狀態是不穩定的,并且R和S輸入的變化可能導致從禁止狀態到復位狀態或置位狀態的不受控制的切換。因此,為了保證穩定和可控的行為,通常會使用帶有附加邏輯電路的改進型觸發器,如帶有時鐘輸入的D觸發器或JK觸發器。

rs觸發器的約束條件是什么

RS觸發器在設計和使用時存在一些約束條件,以確保其正確的功能和避免潛在的問題。以下是RS觸發器的一些常見約束條件:

1. 非禁止狀態:輸入R和S不應同時為邏輯高電平(1),即R和S不能同時為1。這是為了避免觸發器進入禁止狀態,因為禁止狀態下觸發器的行為是不可預測的。

2. 觸發器建立和保持時間:對于RS觸發器的輸入信號,應滿足觸發器的建立時間(Setup Time)和保持時間(Hold Time)要求。即在輸入信號的變化之前和之后,輸入信號需要保持在足夠的時間窗口內,以使觸發器能夠穩定地識別和響應輸入。

3. 輸入噪聲和抖動:輸入信號的噪聲和抖動也是需要考慮的因素。由于RS觸發器是基于電平變化的觸發器,輸入端的不穩定性可能導致輸出的不穩定性和誤觸發。

4. 重置和置位的優先級:在特定情況下,當R和S同時變為1時,觸發器會由于競態條件而產生問題。為了避免競態條件,可以設定重置和置位的優先級,即確定在同時滿足R和S條件時,應該重置還是置位。

5. 時序和時鐘邊沿:在一些應用中,RS觸發器需要與時鐘信號一起使用,這涉及到時序和時鐘邊沿的配合和同步。必須確保輸入信號的變化和觸發器的狀態變化在正確的時鐘邊沿上同步。

這些約束條件可以確保RS觸發器在工作中的可靠性和穩定性。在實際使用中,設計者必須滿足這些約束條件,并且根據具體應用場景進行測試和驗證,以確保觸發器的正確操作。

編輯:黃飛

-

存儲器

+關注

關注

38文章

7514瀏覽量

163997 -

RS觸發器

+關注

關注

3文章

101瀏覽量

17989 -

觸發器

+關注

關注

14文章

2000瀏覽量

61221 -

邏輯功能

+關注

關注

0文章

14瀏覽量

3116

發布評論請先 登錄

相關推薦

基本rs觸發器的約束條件

RS觸發器工作原理_RS觸發器邏輯功能_RS觸發器和SR觸發器的區別

RS觸發器的邏輯功能是什么 rs觸發器的約束條件是什么

RS觸發器的邏輯功能是什么 rs觸發器的約束條件是什么

評論