?CPU 按產(chǎn)品市場可分為 x86 系列和非 x86 系列。x86 系列 CPU 生產(chǎn)廠商只有 Intel、AMD、VIA 三家公司,x86 系列 CPU 在操作系統(tǒng)一級相互兼容,產(chǎn)品覆蓋了 90%以上的桌面計算機(jī)市場。非 x86 系列 CPU 生產(chǎn)廠商有 IBM、Sun、HP、ARM、MIPS、日立、三星、現(xiàn)代、中國科學(xué)院計算研究所等企業(yè)和單位。非 x86 系列 CPU 主要用于大型服務(wù)器和嵌入式系統(tǒng),這些產(chǎn)品大多互不兼容,在桌面計算機(jī)市場中占有份額極小。

Intel 與 AMD 公司的 CPU 雖然在性能和軟件兼容性方面不相上下,但配套的硬件平臺并不能相互完全兼容。例如,它們需要不同的主板進(jìn)行產(chǎn)品配套。CPU制造工藝的逐步提升和硬件糾錯是工藝步進(jìn)提升的原因。通常來說,新步進(jìn)的CPU超頻能力更強(qiáng),發(fā)熱也會略低。如果兩顆 CPU 型號相同,但工藝步進(jìn)不同,從 CPU 超頻角度看,CPU 升級步進(jìn)工藝的同時,一般也會提高 CPU 的超頻能力。

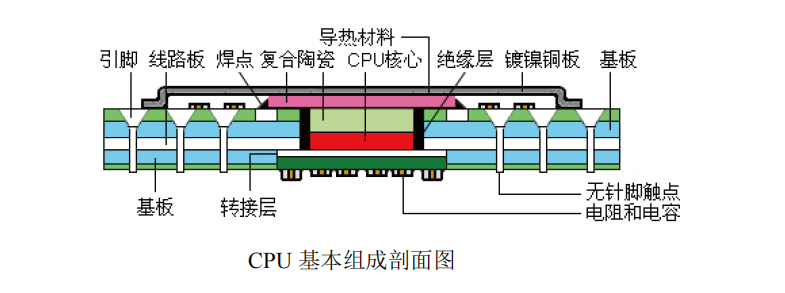

大部分 CPU 采用 LGA 或 FC-PGA 封裝形式。FC-PGA 封裝是將 CPU 核心封裝在基板上,這樣可以縮短連線,并有利于散熱。LGA 采用無針腳觸點封裝形式。CPU 由半導(dǎo)體硅芯片、基板、針腳或無針腳觸點、導(dǎo)熱材料、金屬外殼等部件組成。

(1)外殼(IHS)。CPU 金屬外殼采用鍍鎳銅板,它的作用是保護(hù) CPU 核心不受外力的損壞。外殼表面非常平整光滑,這有利于與 CPU 散熱片的良好接觸。

(2)導(dǎo)熱材料(TIM)。在金屬外殼內(nèi)部與復(fù)合陶瓷之間,填充了一層導(dǎo)熱材料,導(dǎo)熱材料一般采用導(dǎo)熱膏,它具有良好的絕緣性和極佳的導(dǎo)熱性能,它的功能是將 CPU 內(nèi)核發(fā)出的熱量傳導(dǎo)到金屬外殼上。

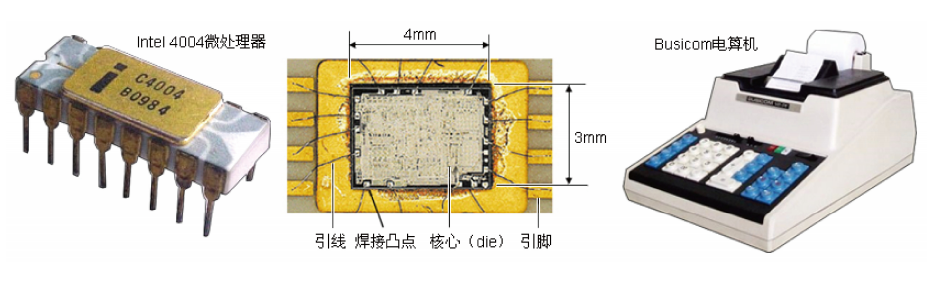

(3)CPU 核心(die)。CPU 核心是一個薄薄的硅晶片,尺寸一般為 12mm×12mm×1mm左右。目前 CPU 核心中有多個內(nèi)核(2/4/6/8 個),8 內(nèi)核的 Intel Xeon CPU 集成的晶體管數(shù)達(dá)到了 24 億個。

(4)轉(zhuǎn)接層。CPU 核心與基板之間有一個轉(zhuǎn)接層,它的作用有三個:一是將非常細(xì)小的 CPU 內(nèi)核信號線轉(zhuǎn)接到 CPU 針腳上;二是保護(hù)脆弱的 CPU 核心不受損傷;三是將 CPU核心固定在基板上。轉(zhuǎn)接層采用復(fù)合材料制造,有良好的絕緣性能和導(dǎo)熱性能。在轉(zhuǎn)接層上,采用光刻電路與 CPU 內(nèi)核的電路直接相連。在轉(zhuǎn)接層下面,采用焊點與基板上的線路相連。

(5)基板。金屬封裝殼周圍是 CPU 基板,基板的功能一是連接轉(zhuǎn)接層與 CPU 針腳,另外一個功能是設(shè)計一些電路,防止 CPU 內(nèi)核的高頻信號對主板產(chǎn)生干擾。

(6)電阻和電容。基板底部中間有的電容和電阻,主要用于消除 CPU 對外部電路的干擾,以及與主板電路進(jìn)行阻抗匹配。每個系列的 CPU 產(chǎn)品,這些電容和電阻的排列方式都有所不同。

(7)針腳。基板下面的鍍金無針腳觸點,是 CPU 與外部電路連接的通道。

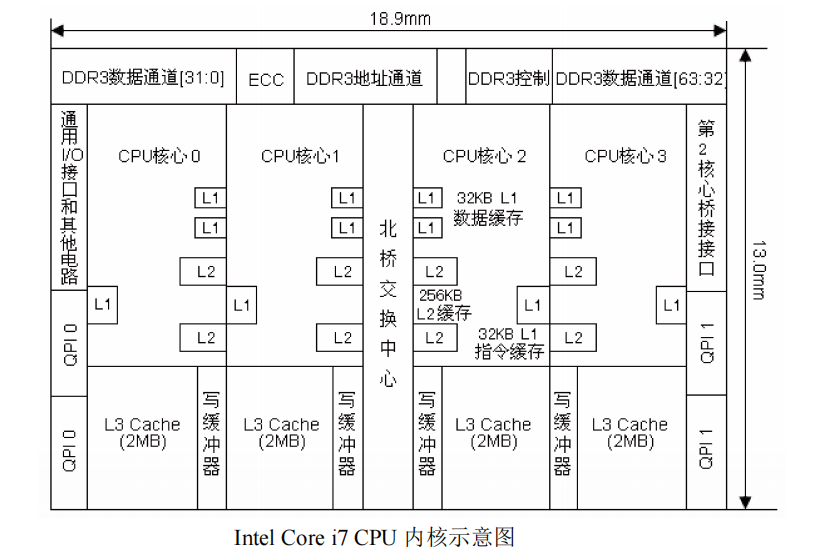

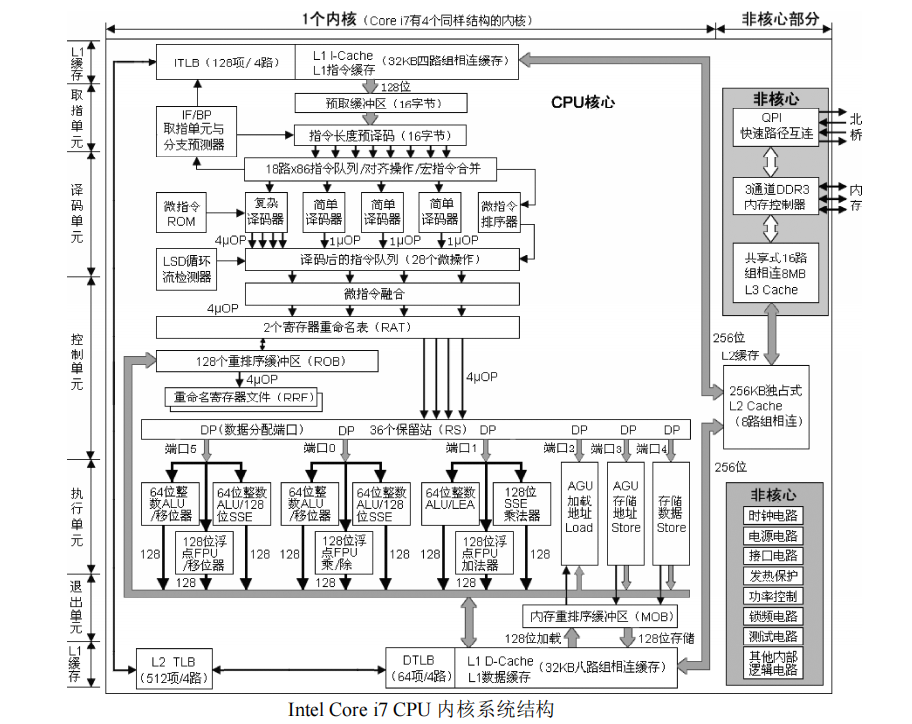

Core i7 CPU 內(nèi)核分為核心(Core)與非核心(UnCore)兩大部分。核心部分包括 CPU執(zhí)行流水線和 L1、L2 級高速緩存。非核心部分為 L3 級高速緩存、集成內(nèi)存控制器(IMC)、快速路徑互連總線(QPI),以及功耗與時鐘控制單元等。

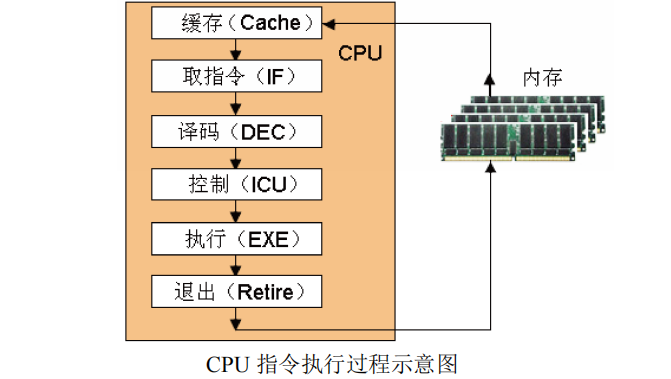

CPU 工作過程大致如下:指令和數(shù)據(jù)在執(zhí)行前,首先要加載到內(nèi)存或 CPU 內(nèi)核的高速緩存(L1/L2/L3 Cache)中,這個過程稱為緩存。CPU 根據(jù)指令指針(PC)寄存器指示的地址,從高速緩存或內(nèi)存中獲取指令;然后對分支指令進(jìn)行預(yù)測工作,這個過程稱為取指令(IF)。

CPU取到指令后,需要判斷這條指令是什么類型的指令,需要執(zhí)行什么操作,并負(fù)責(zé)把取出的指令譯碼為微操作(μOP)指令,這個過程稱為譯碼(DEC)。指令譯碼后可以得到操作碼和操作數(shù)地址,然后根據(jù)地址取操作數(shù)。然后需要對多條微操作指令分配計算所需要的資源(如寄存器、加法器等),這個過程稱為指令控制(ICU)或指令分派。

當(dāng)操作數(shù)被取出來以后,計算單元(如 ALU)根據(jù)操作碼的指示,就可以對操作數(shù)進(jìn)行正確的計算了,指令的計算過程稱為執(zhí)行(EXE)。執(zhí)行結(jié)束后,計算結(jié)果被寫回到 CPU內(nèi)部的寄存器堆中,有時需要將計算結(jié)果寫回到緩存和內(nèi)存中,這個過程稱為退出(Retire)或?qū)懟亍5酱藶橹梗粭l指令的整個執(zhí)行過程就完成了。

Core i7 CPU 包括幾十個系統(tǒng)單元。從體系結(jié)構(gòu)層次看,CPU 的內(nèi)部結(jié)構(gòu)主要有緩存單元(Cache)、取指單元(IF)、譯碼單元(DEC)、控制單元(ICU)、執(zhí)行單元(EXE)、退出單元(RU)等。

Core i7CPU 每個單核有 5 個 64 位整數(shù)算術(shù)邏輯運(yùn)算單元(ALU),3個 128 位的浮點處理單元(FPU)。CPU 中每個核心在最好的情況下,理論上每個時鐘周期可以進(jìn)行以下操作:取指令或數(shù)據(jù) 128 位/周期;譯碼 4 條 x86 指令(1 個復(fù)雜指令,3 個簡單指令)/周期;發(fā)送 7 條微指令/周期;重排序和重命名 4 條微指令/周期;發(fā)送 6 條微指令到執(zhí)行單元/周期;執(zhí)行 5×64 位=320 位整數(shù)運(yùn)算/周期;或執(zhí)行 3×128 位=384 位浮點運(yùn)算/周期;完成并退出 4 條微指令(128 位)/周期。CPU 在 3.2GHz 頻率下的峰值浮點性能為 51GFLOPS(雙精度)或者 102GFLOPS(單精度)。

CPU 訪問存儲系統(tǒng)時,在存儲系統(tǒng)中找到所需數(shù)據(jù)的概率稱為命中率,命中率計算方法如下所示,命中率越接近于 1 越好。

CPU 訪問存儲系統(tǒng)時,通常先訪問 Cache,由于 CPU 所需要的信息不會百分之百地在Cache 中,這就存在一個命中率的問題。從理論上說,只要 Cache 的大小與內(nèi)存的大小保持適當(dāng)比例,Cache 的命中率是相當(dāng)高的。對于沒有命中的指令或數(shù)據(jù),CPU 只好再次訪問內(nèi)存,這時 CPU 將會浪費(fèi)更多的時間。

為了保證 CPU 訪問 Cache 時有較高的命中率,Cache 中的內(nèi)容一般按一定的算法進(jìn)行替換。較常用的算法有“最近最少使用算法”(LRU),它是將最近一段時間內(nèi)最少被訪問過的 Cache 數(shù)據(jù)行淘汰出局。目前 CPU 高速緩存的命中率可達(dá)到 95%以上。

審核編輯:湯梓紅

-

處理器

+關(guān)注

關(guān)注

68文章

19404瀏覽量

230783 -

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3620瀏覽量

129649 -

cpu

+關(guān)注

關(guān)注

68文章

10901瀏覽量

212675 -

計算機(jī)

+關(guān)注

關(guān)注

19文章

7534瀏覽量

88450 -

操作系統(tǒng)

+關(guān)注

關(guān)注

37文章

6889瀏覽量

123598

原文標(biāo)題:CPU基本組成及關(guān)鍵技術(shù)介紹

文章出處:【微信號:架構(gòu)師技術(shù)聯(lián)盟,微信公眾號:架構(gòu)師技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

開關(guān)電源的基本組成及工作原理

計算機(jī)的基本組成及工作原理

計算機(jī)的基本組成和工作原理是什么

計算機(jī)的分類及基本組成

CPU的工作過程是怎樣的

計算機(jī)硬件的基本組成

STM32 PWM工作過程

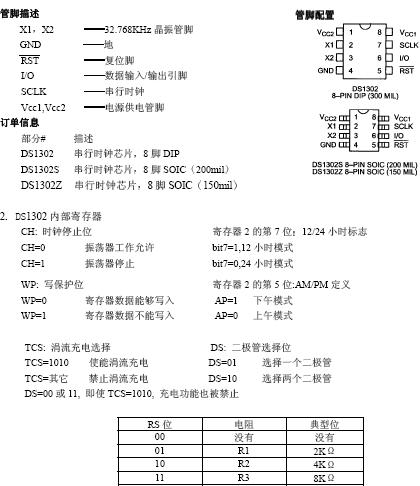

DS1302 的基本組成和工作原理

數(shù)控機(jī)床的工作過程

IPOA的工作過程是怎樣的?

CPU工作過程——MCU

CPU的基本組成和工作過程

CPU的基本組成和工作過程

評論