相信不少人都聽過verilog這個詞,今天我就想講一講我所理解的verilog是什么。

Verilog是一種硬件描述語言,它最基本的功能,就是把一份電路圖用代碼的形式表示出來,然后讓計算機理解一份代碼所對應(yīng)的電路。

硬件描述語言有很多,現(xiàn)在主流的基本就是verilog,或者它的升級版systemverilog。之前上學(xué)的時候還接觸過VHDL,但現(xiàn)在好像慢慢地沒什么人在用了。

Verilog代碼和C、Java這種計算機編程語言有本質(zhì)的不同,verilog里基本所有寫出來的東西都會對應(yīng)實際的電路。

聲明變量的時候如果指定是一個reg,那么這個變量就有寄存數(shù)值的功能,可以綜合出來一個實際的寄存器;如果指定是一段wire,那么他就只能傳遞數(shù)據(jù),只是表示一條線。

在verilog里寫一個判斷可能就對應(yīng)了一個mux,寫一個for可能就是把一段電路重復(fù)好幾遍(這在電路設(shè)計中是不太實用的,for語句也好像只在systemverilog中才支持)。

最能體現(xiàn)電路設(shè)計思想的就是always塊了,它可以指定某一個信號在某個值或某個跳變的時候執(zhí)行塊里的代碼。

總之,前端工程師寫verilog代碼的目的,就是要對應(yīng)出一個實際的電路出來,這個電路會完成我們期望的邏輯功能。

但是,人類寫出來的verilog代碼是高度抽象的,一般人甚至編碼者自己也很難把一段verilog代碼和實際的電路聯(lián)系起來。

編碼者在編寫的時候更多的是關(guān)心信號的邏輯功能有沒有錯誤,我們會看每一個關(guān)鍵信號的波形,確保輸入輸出一切正常。

至于哪里用了一個三輸入與門或者兩個二輸入與門我們不會去關(guān)心。一般就把這些人類寫出來的很抽象的代碼叫做verilog RTL代碼,RTL是register transition level。

RTL代碼要翻譯給機器看懂,還要經(jīng)過synthesis(綜合)這一步。這一步是tool完成的,它表示就把RTL變成最基本的邏輯門連接的形式,還是以verilog的格式寫出來,一般我們就稱綜合后的verilog為網(wǎng)表文件,或者叫netlist。

綜合的時候已經(jīng)要開始考慮芯片PPA的性能了,要知道,一段邏輯相同的電路,可能有很多種實現(xiàn)方式。

比如說一個邏輯表達式可以寫成與非的形式,也能寫成或非形式,對應(yīng)的電路可能就是與非門或者或非門。

而對于同一種電路,選用的cell可能也不一樣,同樣是一顆buffer,要選驅(qū)動能力多大的、開啟電壓選多大的等等也有很多講究。

后端在拿到netlist就可以布局布線了,我們后端在做的時候netlist也不是會一成不變的,我們會在確保邏輯功能不變的前提下對netlist進行改動。

但是,改動之后必須要和改動前的netlist對比檢查,確保沒有改它的邏輯才行。

這一步有時候我們就會稱為formal檢查,formality就是一個可以用來做這種檢查的工具,synopsys家的。實際上,前端在綜合前后也會做類似的檢查。

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

120932 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1028瀏覽量

54969 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110258 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59911

發(fā)布評論請先 登錄

相關(guān)推薦

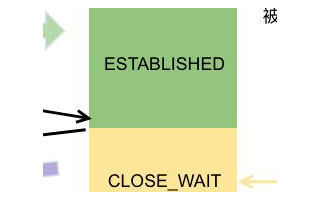

講一講的TCP三次握手和四次揮手

講一講芯片設(shè)計中的verilog是什么

講一講芯片設(shè)計中的verilog是什么

評論