01 關(guān)于ILA Cross Trigger

1)ILA Cross Triggering功能使得ILA核心之間、以及ILA核心與處理器(例如,AMD Zynq 7000 SoC)之間可以進(jìn)行Cross Trigger。這個(gè)功能在你需要在不同時(shí)鐘域的兩個(gè)ILA核心之間觸發(fā),或者在處理器和ILA核心之間執(zhí)行硬件/軟件跨觸發(fā)時(shí)非常有用。

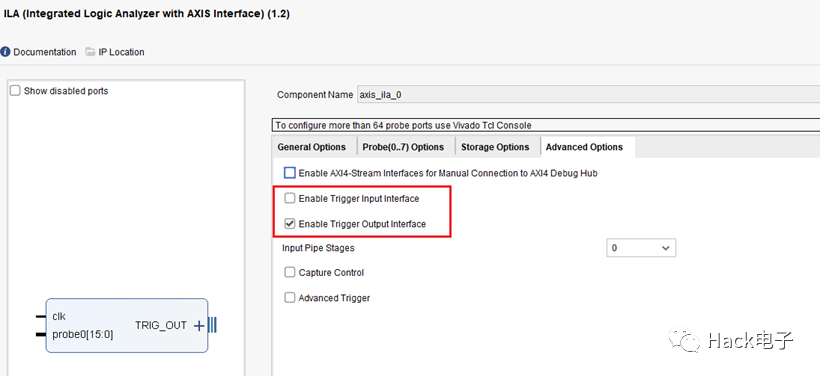

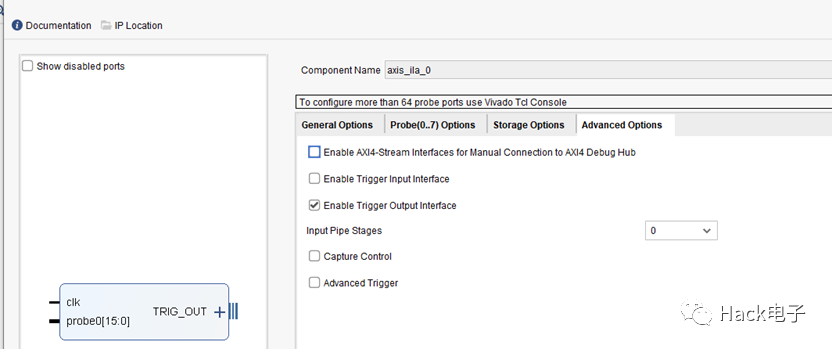

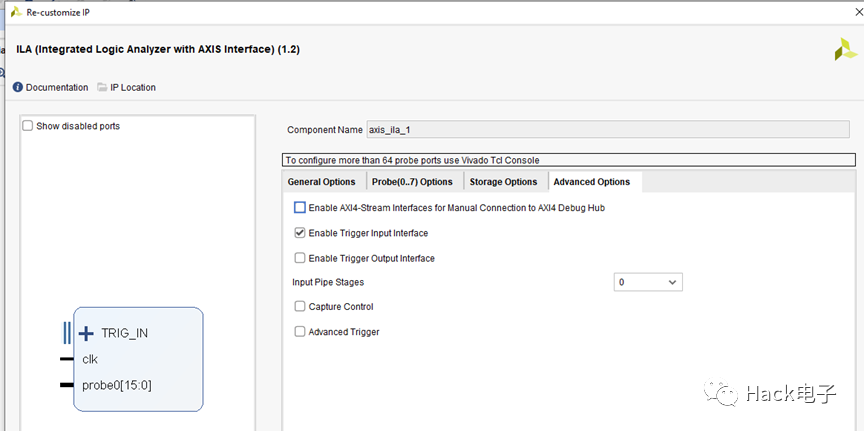

要使用Cross Trigger功能,在核心生成時(shí),你應(yīng)該配置ILA核心具有專用的觸發(fā)輸入端口(TRIG_IN和TRIG_IN_ACK)和專用的觸發(fā)輸出端口(TRIG_OUT和TRIG_OUT_ACK)。

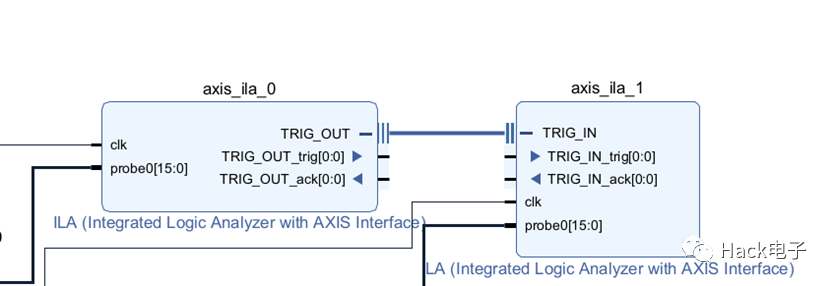

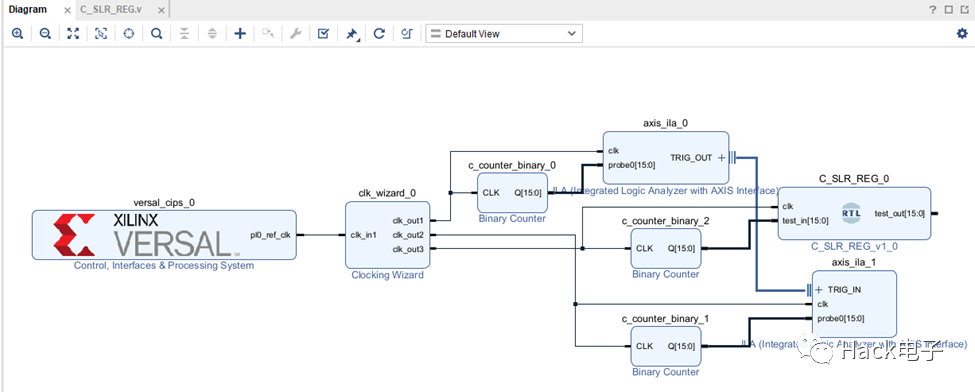

(一對(duì)ILA的TRIG_OUT和TRIG_IN 在Block Design中的互聯(lián)示意圖)

2)RIG_OUT_ACK 信號(hào)向 ILA 內(nèi)核(另一個(gè) ILA、用戶設(shè)計(jì)或處理器)指示 TRIG_OUT 已正確接收,并導(dǎo)致 ILA 在接收 TRIG_OUT_ACK 時(shí)降低 TRIG_OUT 信號(hào)。

換句話說,TRIG_OUT 保持高電平,直到 TRIG_OUT_ACK 可用。如果 TRIG_OUT_ACK 信號(hào)連接至低電平,則 TRIG_OUT 保持高電平,直到用戶重新啟動(dòng) ILA。只有 TRIG_OUT 變?yōu)榈碗娖健H绻?TRIG_OUT_ACK 連接到低電平,您可以重新準(zhǔn)備 ILA。

下圖展示了典型的交叉觸發(fā)設(shè)置,其中 ILA2 交叉觸發(fā)到 ILA1。ILA2 的 TRIG_OUT 信號(hào)連接到 ILA1 的 TRIG_IN 信號(hào)。ILA 1 的 TRIG_IN_ACK 信號(hào)連接到 ILA2 的 TRIG_OUT_ACK 信號(hào)。

3)典型的交叉觸發(fā)設(shè)置

02 測(cè)試工程基本情況介紹

本測(cè)試工程基與Vivado 2022.2

本測(cè)試工程基于Versal VCK190 Evaluation Platform (xcvc1902-vsva2197-2MP-e-S),這里同時(shí)介紹了以下兩種方式實(shí)現(xiàn)ILA Cross Trigger:

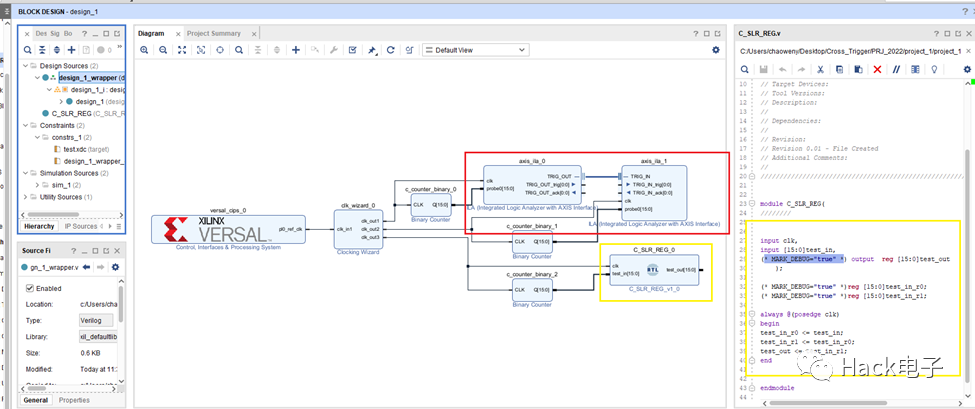

IPI的方式例化帶有Cross TRIG端口的ILA。(對(duì)應(yīng)axis_ila_0和axis_ila_1)

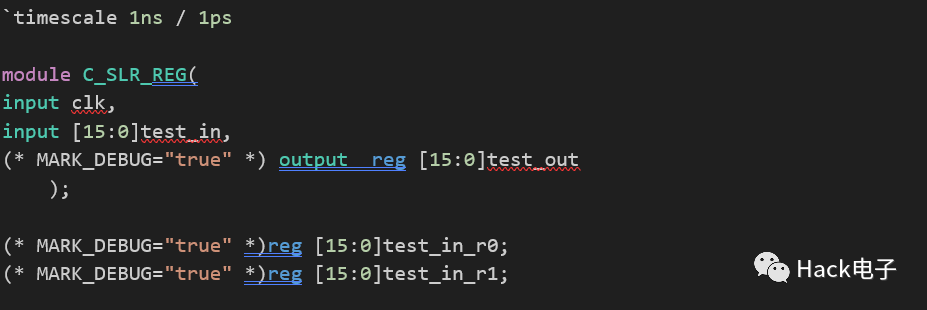

(* MARK_DEBUG="true" *)+ Tcl腳本的的方式(這種方式只支持Vivado 2022.1及更高版本)

紅色方框內(nèi)的axis_ila_0和axis_ila_1在配置IP的時(shí)候直接例化了對(duì)應(yīng)的Cross Trigger接口,黃色方框內(nèi)是對(duì)部分的RTL代碼設(shè)置了(* MARK_DEBUG="true" *)。

03 構(gòu)建步驟

測(cè)試的C_SLR_REG module的代碼如下:

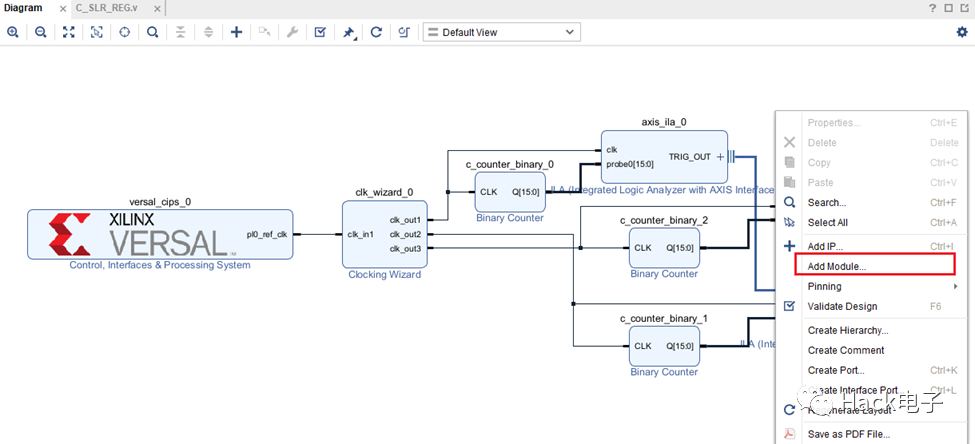

按照下圖構(gòu)建BD工程。

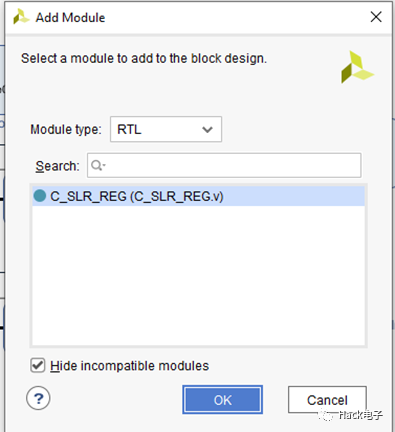

將C_SLR_REG module以RTL的方式加入到BD內(nèi), 操作方法見下圖。

連接好整個(gè)BD然后Create HDL Wrapper并將design_1_wrapper. v設(shè)置成top。

Run Synthesis

a. 綜合完成之后點(diǎn)擊Open Synthesized Design

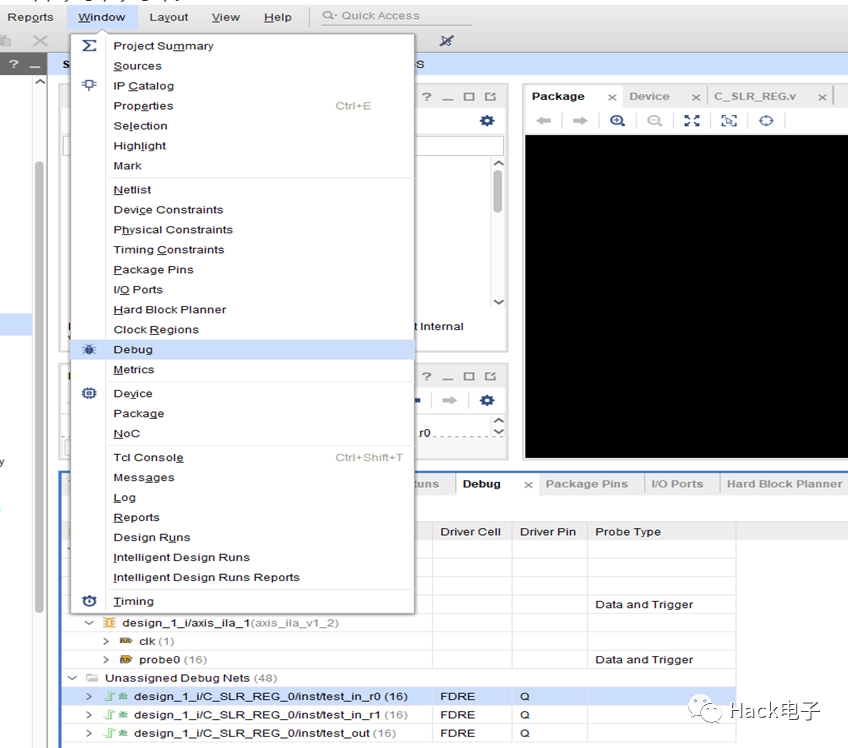

b. 使用如下方式打開Debug窗口

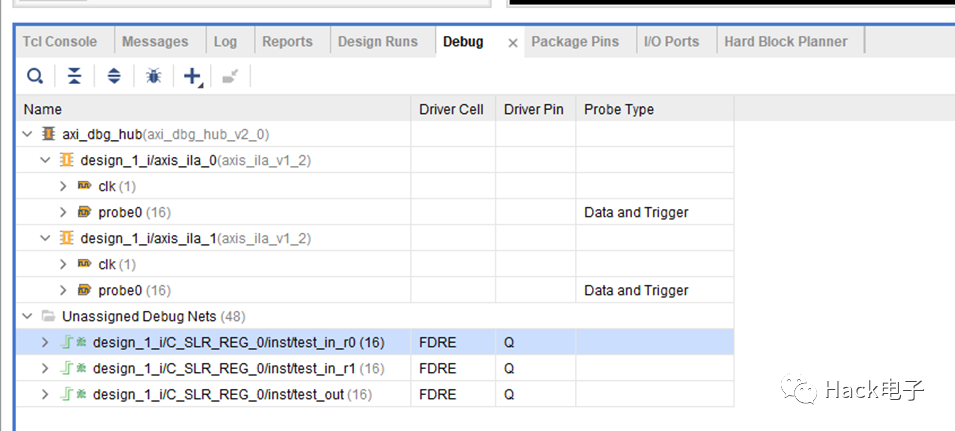

從Debug視圖可以看到已有兩個(gè)IPI例化的ILA(axis_ila_0和axis_ila_1),還有一些Unassigned Debug Nets(design_1_i/C_SLR_REG_0/inst/test_out,design_1_i/C_SLR_REG_0/inst/test_in_r0,design_1_i/C_SLR_REG_0/inst/test_in_r1),下面需要通過Tcl 腳本的方式創(chuàng)建新的debug core將Unassigned Debug Nets連接到新的debug core上。

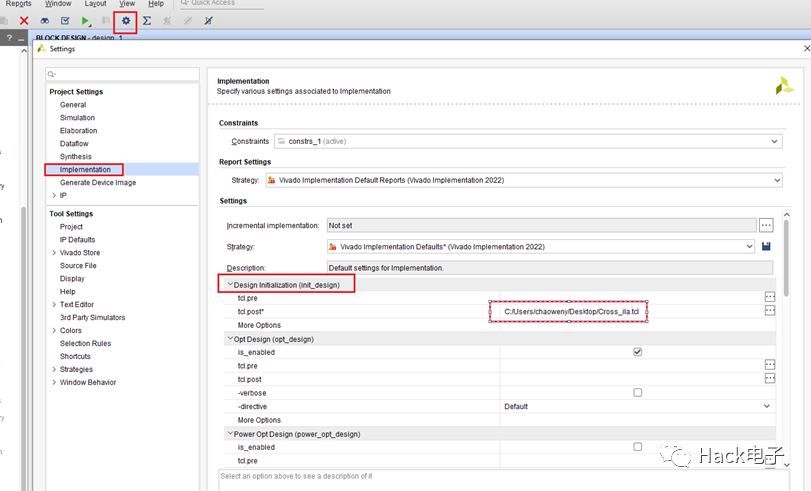

c. Tcl 腳本創(chuàng)建兩個(gè)新的debug core(u_ila_2和u_ila_3),(u_ila_3) trig_out -> (u_ila_2) trig_in.新建一個(gè)Tcl腳本(此處位Cross_ila.tcl)。然后在下圖位置調(diào)用Cross_ila.tcl腳本。

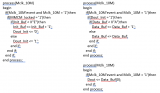

Cross_ila.tcl文件內(nèi)容如下:

###createu_ila_2 create_debug_coreu_ila_2ila set_propertyC_TRIGIN_ENtrue[get_debug_coresu_ila_2] set_propertyC_TRIGOUT_ENfalse[get_debug_coresu_ila_2] set_propertyC_NUM_OF_PROBES1[get_debug_coresu_ila_2] #createu_ila_2TRIG_IN_trigandTRIG_IN_ack create_debug_portu_ila_2TRIG_IN_trig create_debug_portu_ila_2TRIG_IN_ack #configu_ila_2/clk set_propertyport_width1[get_debug_portsu_ila_2/clk] connect_debug_portu_ila_2/clk[get_nets[listdesign_1_i/clk_wizard_0_clk_out3]] #configu_ila_2/probe0 set_propertyPROBE_TYPEDATA_AND_TRIGGER[get_debug_portsu_ila_2/probe0] set_propertyport_width16[get_debug_portsu_ila_2/probe0] connect_debug_portu_ila_2/probe0[get_nets[listdesign_1_i/C_SLR_REG_0/inst/test_out[*]]] ###createu_ila_3 create_debug_coreu_ila_3ila set_propertyC_TRIGIN_ENfalse[get_debug_coresu_ila_3] set_propertyC_TRIGOUT_ENtrue[get_debug_coresu_ila_3] set_propertyC_NUM_OF_PROBES2[get_debug_coresu_ila_3] #createu_ila_3TRIG_IN_trigandTRIG_IN_ack create_debug_portu_ila_3TRIG_OUT_trig create_debug_portu_ila_3TRIG_OUT_ack #configu_ila_3/clk set_propertyport_width1[get_debug_portsu_ila_3/clk] connect_debug_portu_ila_3/clk[get_nets[listdesign_1_i/clk_wizard_0_clk_out3]] ##create_debug_core的時(shí)候會(huì)自動(dòng)創(chuàng)建probe0和clk端口 #configu_ila_3/probe0 set_propertyPROBE_TYPEDATA_AND_TRIGGER[get_debug_portsu_ila_3/probe0] set_propertyport_width16[get_debug_portsu_ila_3/probe0] connect_debug_portu_ila_3/probe0[get_nets[listdesign_1_i/C_SLR_REG_0/inst/test_in_r0[*]]] #configu_ila_3/probe1 create_debug_portu_ila_3probe set_propertyPROBE_TYPEDATA_AND_TRIGGER[get_debug_portsu_ila_3/probe1] set_propertyport_width16[get_debug_portsu_ila_3/probe1] connect_debug_portu_ila_3/probe1[get_nets[listdesign_1_i/C_SLR_REG_0/inst/test_in_r1[*]]] ###connectu_ila_2/3 create_netila2_trig_to_ila3 create_netila2_ack_to_ila3 connect_net-netila2_trig_to_ila3-objects[get_pinsu_ila_3/TRIG_OUT_trig] connect_net-netila2_ack_to_ila3-objects[get_pinsu_ila_3/TRIG_OUT_ack] connect_net-netila2_trig_to_ila3-objects[get_pinsu_ila_2/TRIG_IN_trig] connect_net-netila2_ack_to_ila3-objects[get_pinsu_ila_2/TRIG_IN_ack] #set_false_path set_false_path-through[get_nets{ila2_trig_to_ila3}] set_false_path-through[get_nets{ila2_ack_to_ila3}] 5)RunImplementation. 6)GenerateDevieImage/Bit.

04 HW調(diào)試

Implementation完成之后,連接上板卡。

實(shí)際運(yùn)行結(jié)果

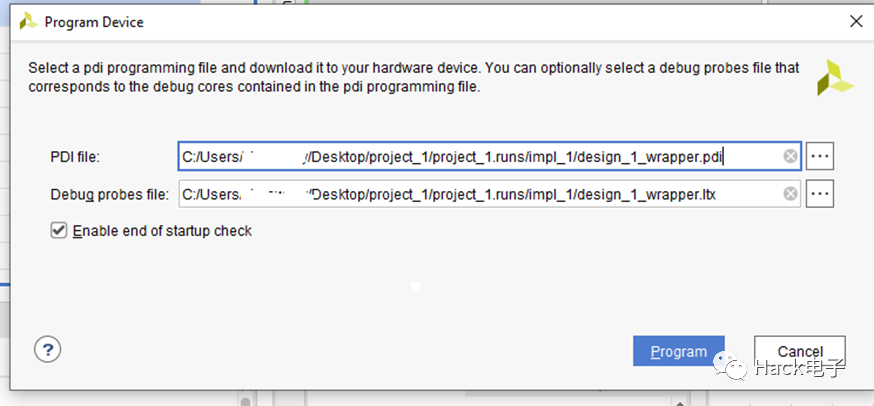

將PDI文件下載到器件中。

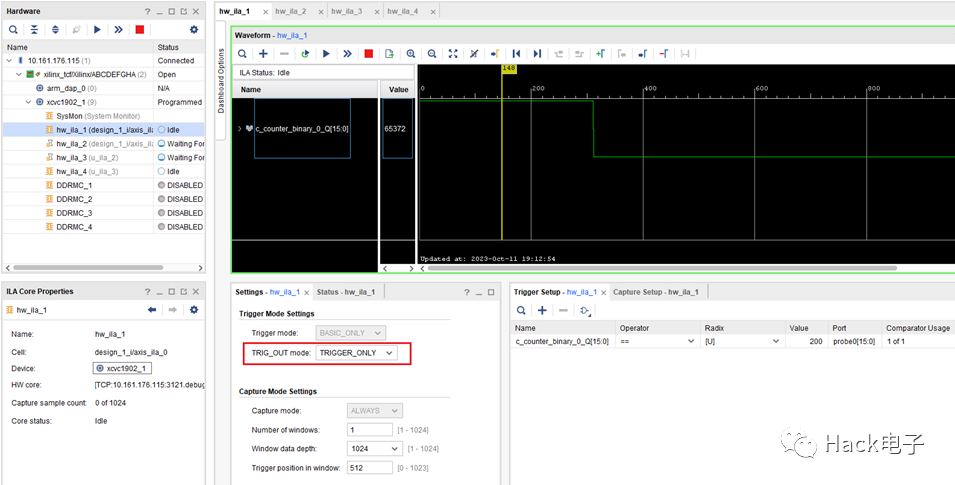

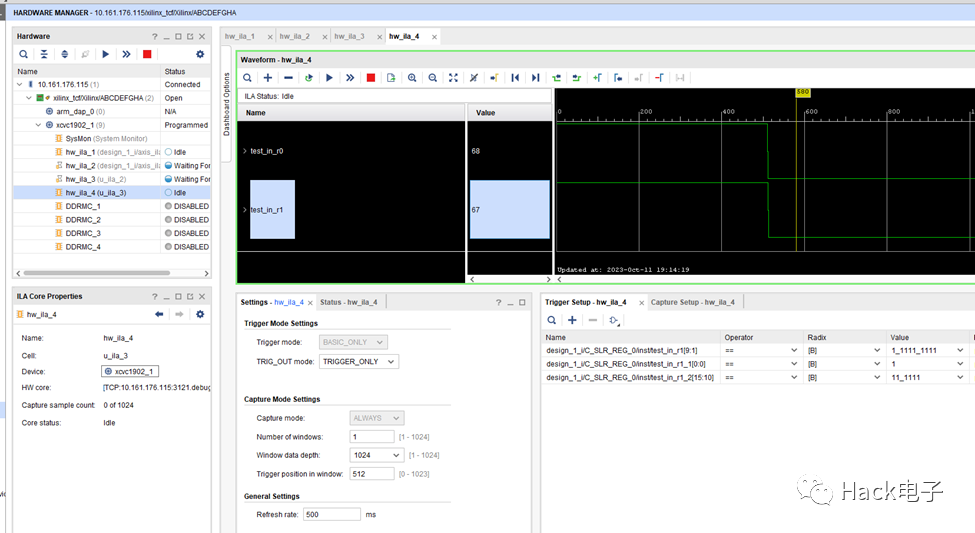

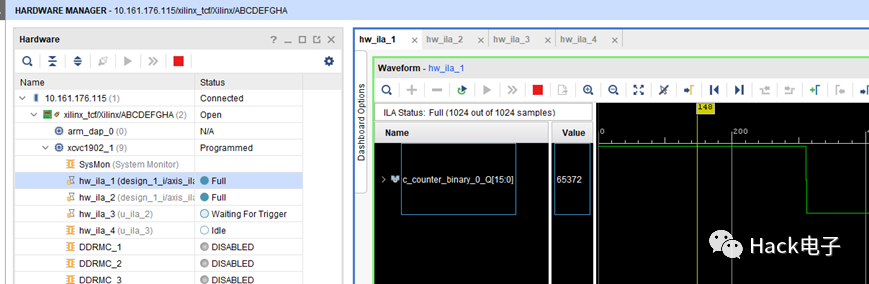

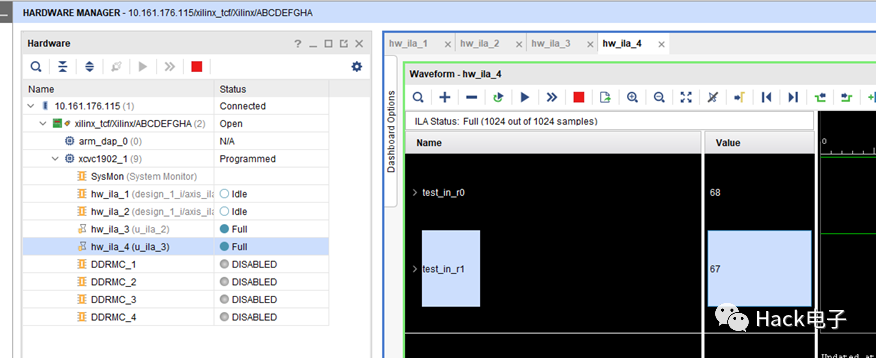

可以發(fā)現(xiàn)出現(xiàn)了四個(gè)hw_ila_1/2/3/4,與工程中的ila debug core對(duì)應(yīng)關(guān)系如下。

hw_ila_1:axis_ila_0 hw_ila_2:axis_ila_1 hw_ila_3:u_ila_2 hw_ila_4:u_ila_3

之前配置的兩組Cross Trigger:

axis_ila_0trig_out->axis_ila_1trig_in (u_ila_3)trig_out->(u_ila_2)trig_in 即: hw_ila_1trig_out->hw_ila_2trig_in hw_ila_4trig_out->hw_ila_3trig_in

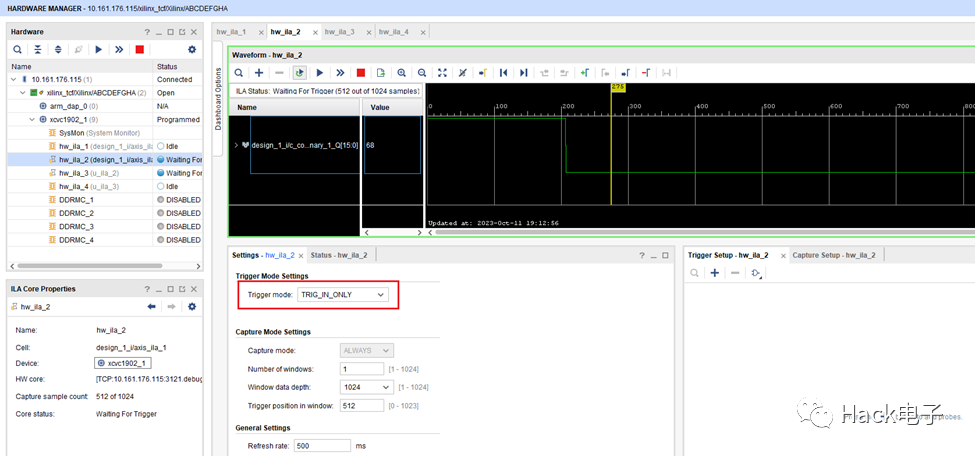

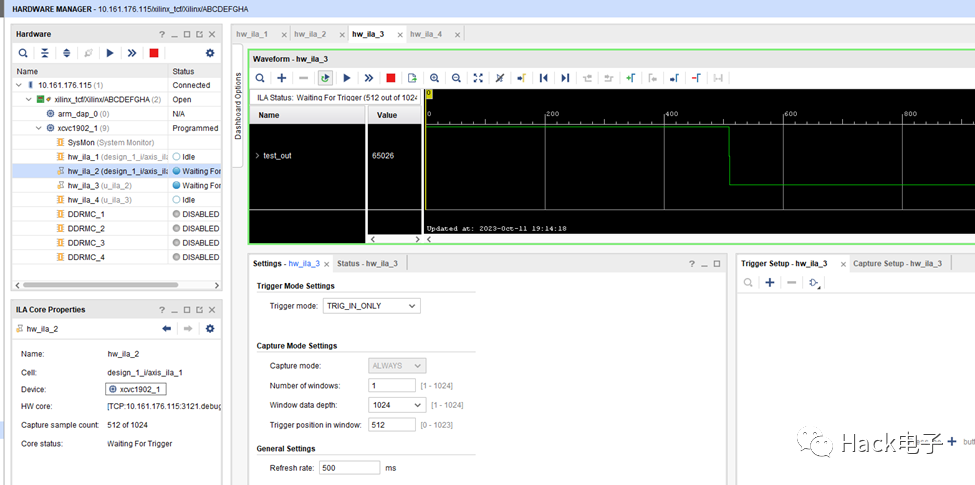

分別設(shè)置hw_ila_1/2/3/4的Trigger mode。

(hw_ila_1)

(hw_ila_2)

(hw_ila_3)

(hw_ila_4)

設(shè)置完成之后就可以實(shí)現(xiàn)ila之間的Cross Trigger.

審核編輯:湯梓紅

-

處理器

+關(guān)注

關(guān)注

68文章

19293瀏覽量

229935 -

amd

+關(guān)注

關(guān)注

25文章

5470瀏覽量

134198 -

信號(hào)

+關(guān)注

關(guān)注

11文章

2791瀏覽量

76795 -

ILA

+關(guān)注

關(guān)注

0文章

5瀏覽量

3604

原文標(biāo)題:如何實(shí)現(xiàn)ILA Cross Trigger

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何在下載Bitstream后自動(dòng)觸發(fā)ILA采集

vivado ILA 實(shí)現(xiàn)在線調(diào)試功能報(bào)錯(cuò),顯示沒有添加ILA,怎么解決?

vivado ILA在線調(diào)試求助

雙核C2000 Cross Trigger功能使用方法分享

實(shí)現(xiàn)ila時(shí)出錯(cuò)

蜂鳥E203 V2的FPGA實(shí)現(xiàn)之后,上板測(cè)試想用ila抓取內(nèi)部信號(hào)沒有波形是為什么?

Logic Cross-Reference

什么是D-ILA投影技術(shù)

Schmitt_Trigger_Oscillator電路設(shè)計(jì)

Vivado中關(guān)于ILA的詳解

Vivado之ILA詳解

ILA工作原理 ILA使用方法與注意

如何實(shí)現(xiàn)ILA Cross Trigger

如何實(shí)現(xiàn)ILA Cross Trigger

評(píng)論