1. 前言

在數(shù)字IP/IC,FPGA項目的上板驗證階段,對于一些難以確定原因的bug,比如:RTL仿真時,測試pattern覆蓋不夠全面,fpga跑起來后的實際信號時序可能跟RTL 仿真不一致,從而出現(xiàn)Bug。一種debug的方式就是用FPGA工具提供的ILA模塊(xilixn在ISE中叫:chipscope),來實時抓取FPGA內(nèi)部數(shù)字信號的波形,分析邏輯錯誤的原因,幫助debug。

ILA的正確、高效使用,能加速debug的進程。

2. ILA工作原理

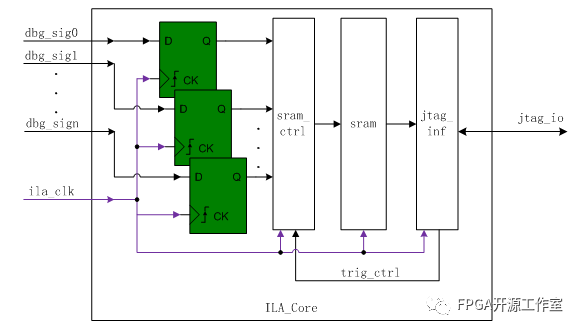

根據(jù)xilinx的datasheet功能描述,猜測ILA也是一個數(shù)字IP,大致結(jié)構(gòu)如下:

其中:

1) dbg_sig?:是待觀測的debug信號;

2) ila_clk:是設(shè)置的ILA工作時鐘(監(jiān)測、抓取);

3) jtag_inf:ILA數(shù)據(jù)與上層的交互口(tigger條件設(shè)置,抓取的數(shù)據(jù)上傳);

4) sram_ctrl:根據(jù)trig_ctrl,觸發(fā)抓取,并把抓取的數(shù)據(jù)按cila_clk的cycle實時寫入SRAM;

5) sram:抓取數(shù)據(jù)的存儲空間;

6) jtag_io:Jtag協(xié)議定義的標(biāo)準(zhǔn)IO;

根據(jù)這個大致結(jié)構(gòu),預(yù)計ILA工作原理如下:

1) PC端GUI應(yīng)用程序設(shè)置trigger條件;通過jtag_io配置進入ILA core;

2) ILA core開始工作,使用ila_clk監(jiān)測debug信號是否符合tigger條件;

3) 符合條件后,使用ila_clk抓取debug信號,并實時存入SRAM;

4) 抓取結(jié)束后,通過jtag_io把debug信號的值上傳到PC端;

5) PC端GUI應(yīng)用程序顯示波形;

根據(jù)這個工作原理,可以推導(dǎo)出ILA的一些使用特性:

1) ILA加入后,需要增加LUT/DFF的使用量;

2) ILA加入后,需要增加的使用量,跟debug信號的數(shù)量,抓取深度成正比;

這些特性,跟實際布局布線后的結(jié)果是匹配的。

3. ILA使用方法與注意

ILA的使用步驟如下:

A. 設(shè)計綜合;

B. 點擊:Set Up Debug開始添加ILA;

C. 添加debug信號:

D. 對每個debug信號選擇監(jiān)測、抓取時鐘:

E. 設(shè)置抓取特性:

F. 結(jié)束,保存ILA設(shè)置。ILA信息將存入工程的xdc約束文件:

到此,ILA插入結(jié)束,在place&route完成,產(chǎn)生configure bit后,下載進入FPAG即可使用ILA進行內(nèi)部觀測了。

4. ILA使用注意

在ILA的使用過程中,有如下3點需要注意:

A. 設(shè)置監(jiān)測、抓取時鐘時,最好用drive這個信號的clk。因為是數(shù)字電路,也存在跨時鐘域的問題。如果ila_clk和debug信號的clk不一致,這兒就是一個跨時鐘域的點。在P&R時,timing會報錯。你可以用set_false_path來mask掉這些timing violation,但是需要記住跨時鐘域的特性:如果debug一個4bit信號,實際信號只有4‘b0001--》 4’b0111的變化,可能抓取到:4‘b0001--》 4’b0101 -》 4‘b0111。

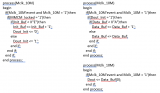

B. 因為綜合可能優(yōu)化掉一些信號(尤其是組合邏輯),或改變信號的名字,為了keep某些信號,可以在RTL code中,添加:“* mark_debug = “true” *”,使用如下:

C. 設(shè)置抓取特性時,“input pipe stage”建議設(shè)置到2~3。這樣雖然多用些DFF,可以確保ILA輸入時的timing更容易過。因為你的debug邏輯可能離ILA core非常的遠,增加pipe stage寄存器,可以把信號一級一級pipe到ILA core的輸入口。

5. 寫在最后

雖然ILA比邏輯分析儀好用多了,但是并不建議靠ILA來debug。因為:

1) ILA分析的波形長度有限;

2) ILA抓取的信號數(shù)量有限;

3) 添加大量信號時,麻煩;

4) 如果需要新加debug信號,需要重新做ILA,在Place&Route,這樣費時費力(一個稍大的工程,可能需要跑數(shù)小時);

所以,“此女”雖好但不可褻玩焉,否則走火入魔,舉步維艱。建立完備的測試pattern,cover全功能點,跑RTL simulation才是正道。

編輯:jq

-

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80756 -

GUI

+關(guān)注

關(guān)注

3文章

662瀏覽量

39827 -

ILA

+關(guān)注

關(guān)注

0文章

5瀏覽量

3616

原文標(biāo)題:數(shù)字IC/FPGA設(shè)計基礎(chǔ)_ILA原理與使用

文章出處:【微信號:bianpinquan,微信公眾號:變頻圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ADC12DJ3200設(shè)置斜坡測試模式,通過ILA查看數(shù)據(jù),從第九個數(shù)據(jù)開始出現(xiàn)錯誤,怎么解決?

毫伏表的使用方法和注意事項

光纖收發(fā)器的使用方法和注意事項

現(xiàn)場總線的使用方法與注意事項

BLDC電機的工作原理和使用方法

鉗形電流表的使用方法和注意事項

LCR電橋測試儀的工作原理與使用方法

電阻測試儀的使用方法和注意事項

點焊機的工作原理及使用方法

錫膏的使用方法及注意事項

如何在下載Bitstream后自動觸發(fā)ILA采集

ILA工作原理 ILA使用方法與注意

ILA工作原理 ILA使用方法與注意

評論