d觸發(fā)器有記憶功能嗎

D觸發(fā)器(D flip-flop)可以存儲一位二進制數據的狀態(tài),因此具有記憶功能。D觸發(fā)器通常用于數字電路中,用于實現寄存器、計數器等電路,可以通過時鐘信號進行同步操作,使它們可以存儲和操作二進制數據。值得注意的是,D觸發(fā)器只能存儲一位二進制數據,如果要存儲更多的數據,則需要使用多位寄存器。

D 觸發(fā)器

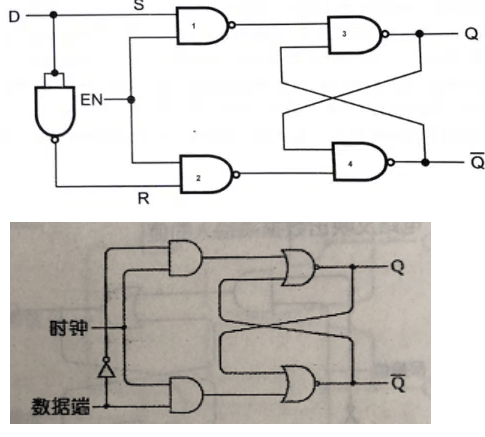

采用與和或非的D觸發(fā)器功能是一樣的,但都是或非元件減少對元件種類的要求。

SR latch:S輸入端水平對面的是Q非端,但鎖存的數據是出現在Q端;D flipflop的S端水平對面就是Q端,因為中間加了元件。

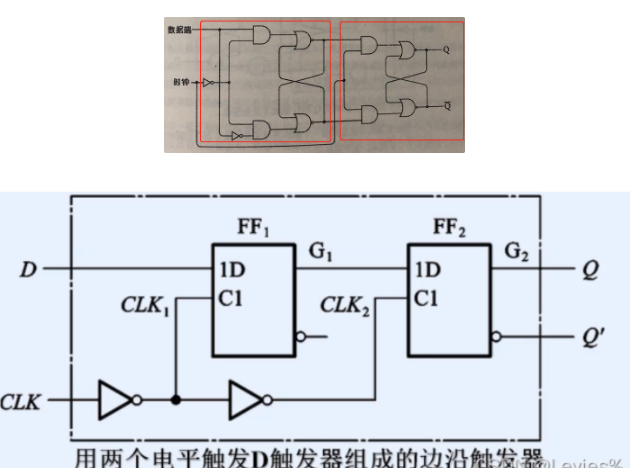

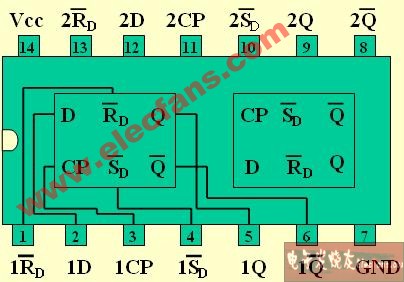

邊沿觸發(fā)的D觸發(fā)器需要兩個電平觸發(fā)的D觸發(fā)器組合而成,原理就是第一級的D觸發(fā)器隨著電平改變了輸出,但第二級需要等到高電平的到來才能改變,也就是時鐘的跳變。

D觸發(fā)器的基本原理

D觸發(fā)器是數字電路中最常用的觸發(fā)器類型之一,它用于存儲一位二進制數據的狀態(tài)。其基本原理如下:

D觸發(fā)器由兩個交叉耦合的反相器(也稱為非門)組成,常用的形式是由兩個NAND門構成。這兩個NAND門的輸出分別連接到對方的輸入端,形成一個正反饋回路。

D觸發(fā)器具有一個輸入端D(Data)和一個時鐘輸入端CLK(Clock)。當時鐘輸入為高電平(上升沿或下降沿)時,D觸發(fā)器會根據輸入端D的值來改變其輸出。

具體操作如下:

1. 當CLK為低電平時,D觸發(fā)器處于暫存狀態(tài),輸入信號D不會被傳遞到輸出。

2. 當CLK為高電平時,D觸發(fā)器被使能,此時輸入信號D的值會被傳遞到輸出。

3. 在CLK的邊沿(上升沿或下降沿)上,D觸發(fā)器會將輸入信號D的值保持到輸出端,即存儲起來。D觸發(fā)器的輸出保持在這個狀態(tài),直到下一次時鐘邊沿到來,并依據新的輸入值進行更新。

總結一下,D觸發(fā)器在時鐘邊沿發(fā)生時將輸入信號D的值傳遞到輸出,并在時鐘保持期間保持該值。這使得D觸發(fā)器能夠存儲輸入信號的狀態(tài),具備記憶功能。

D觸發(fā)器的輸出會受到時鐘的控制,只有在時鐘邊沿的瞬間才會發(fā)生變化。

審核編輯:黃飛

-

寄存器

+關注

關注

31文章

5392瀏覽量

121936 -

二進制

+關注

關注

2文章

802瀏覽量

41878 -

計數器

+關注

關注

32文章

2278瀏覽量

95450 -

D觸發(fā)器

+關注

關注

3文章

164瀏覽量

48177

發(fā)布評論請先 登錄

相關推薦

JK觸發(fā)器 D觸發(fā)器 RS觸發(fā)器 T觸發(fā)器 真值表

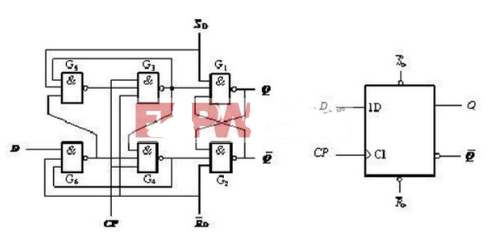

D觸發(fā)器組成T和J-K觸發(fā)器電路圖

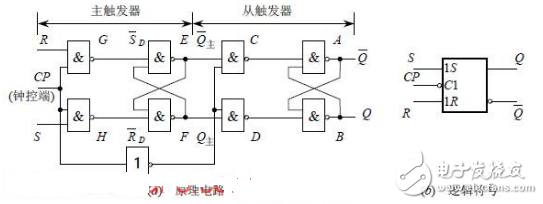

主從sr觸發(fā)器基本原理分析

D觸發(fā)器基本原理

d觸發(fā)器有記憶功能嗎 D觸發(fā)器的基本原理

d觸發(fā)器有記憶功能嗎 D觸發(fā)器的基本原理

評論