功率轉換器可以使用不同技術的寬帶隙半導體,人們常常會比較這些半導體的開關速度和邊緣速率。速度越快,支持的運行頻率就越高、損耗就越低,功率轉換器磁性元件就越小,聽上去很美好。而在真實世界中,更快的dV/dt和di/dt也會成為一個問題,使您難以滿足EMI規格要求——極小的軌道值或寄生電感以及電路電容會產生振鈴,而且如果必須添加多個昂貴的大濾波器來突破發射限制,寬帶隙技術就變得沒那么有吸引力了。振鈴還會導致電壓過沖,從而可能造成損壞,至少會降低電壓安全裕度,因而必須使用額定電壓更高或更昂貴的器件,而這通常伴隨更高的導電損耗。

邊緣放緩會增加耗散

在實踐中,必須控制邊緣速率以避免過沖應力,一個常見解決辦法是添加柵極電阻,而且通常會使用二極管柵極控制方法讓電阻在打開瞬態和關閉瞬態具有不同的電阻值。當然,這會降低電壓和電流邊緣速率以及內部電壓過沖,但是會增加關閉時的電壓/電流重疊,從而提高耗散的功率,而且毫不影響振鈴持續時間,該時間發生在關閉瞬態和柵極驅動穩定后。嘗試降低電感以盡量減小振鈴的努力也會因實際布局而失敗,因為實際布局需要實現安全分離并符合所選器件封裝類型。

緩沖電路是領跑技術

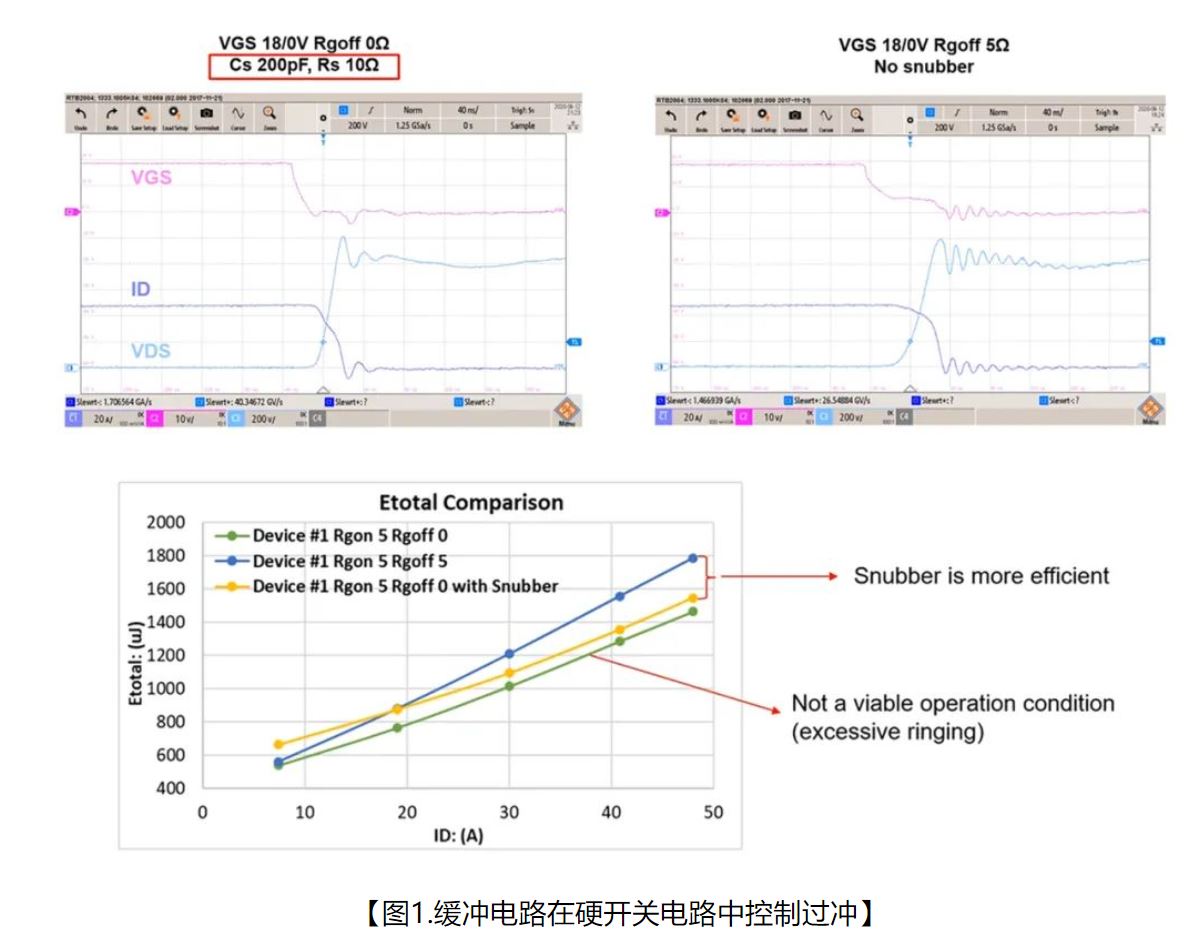

使用SiC FET時有更好的解決辦法,對于硬開關應用,這個辦法是跨器件使用小RC緩沖電路,而對于軟開關,則是在開關處使用電容器,并跨直流鏈路軌使用RC緩沖電路。即使緩沖電路RC值小,也可以有效抑制振鈴,同時限制過沖并保持低損耗。圖1顯示的是在硬開關電路中緩沖電路將過沖值控制到與使用5歐姆柵極電阻時相同,但是卻阻尼卻好得多。與僅使用柵極電阻相比,關閉能量Eoff會減半,但是打開能量Eon會增加10%,因此,為了進行公平比較,我們比較Etotal,結果表明整個緩沖電路方法更高效,同時能提高我們需要的阻尼。在真實電路中,如果ID是40A,開關頻率為100kHz,則使用緩沖電路并且沒有Rgoff的40毫歐SiC FET會耗散10.9W功率,低于僅使用5歐姆Rgoff時。在這兩種情況下,Rgon都設為5歐姆。對于軟開關應用,采用簡單電容器緩沖電路時損耗甚至會更低。

從波形中可以看出,柵極電阻解決辦法還會增加從柵極驅動到漏極電壓上升之間的延遲,大約會從33ns延遲到104ns,而這會限制可以達到的最小占空比和高頻轉換器電路的運行范圍。

SiC FET用戶指南可加快緩沖電路值選擇

通過觀察振鈴波形可以輕松計算緩沖電路值,只需添加一個小的已知緩沖電路電容器C1,它的電容大約是SiC FET數據表輸出電容Coss的3倍,然后觀察頻率變化,再推斷出寄生電容C0,其中包含Coss、雜散電容和所有散熱貢獻。寄生電感L現在可以通過L-C諧振方程計算得出。可能的緩沖電路起始值為C1= 2 x C0,R=√(L/(C0+C1))。還可以在UnitedSiC網站上找到推薦值,請參見:《SiC FET用戶指南》。這里提供了各種產品在硬開關和軟開關的LLC和PSFB應用以及一系列頻率下的值,可以調節這些值,以實現可接受的效率、電壓應力和EMI的組合。

因此,您可以做好準備,讓您的功率轉換器電路加速至高頻,并獲得較小的濾波和功率級磁性元件帶來的體積、重量和成本優勢。所有這些都需要使用最佳SIC FET額定電壓來完成任務,并讓所含EMI達到可控級別。

審核編輯 黃宇

-

電阻

+關注

關注

87文章

5580瀏覽量

173675 -

轉換器

+關注

關注

27文章

8831瀏覽量

149458 -

RC

+關注

關注

0文章

232瀏覽量

49249 -

柵極

+關注

關注

1文章

181瀏覽量

21175 -

SiC

+關注

關注

30文章

3039瀏覽量

63787

發布評論請先 登錄

相關推薦

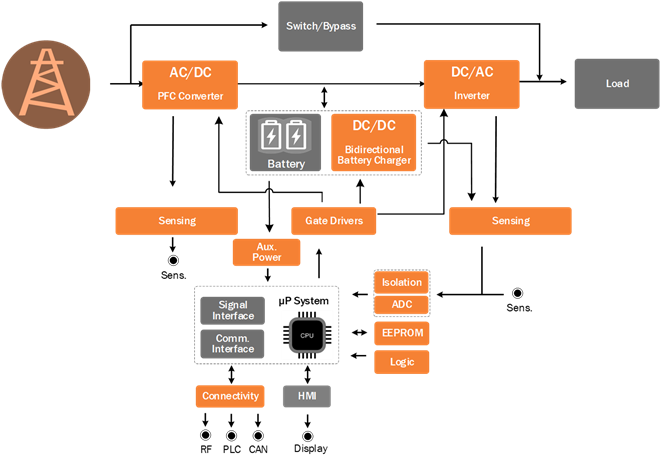

安森美豐富的SiC方案解決新一代UPS的設計挑戰

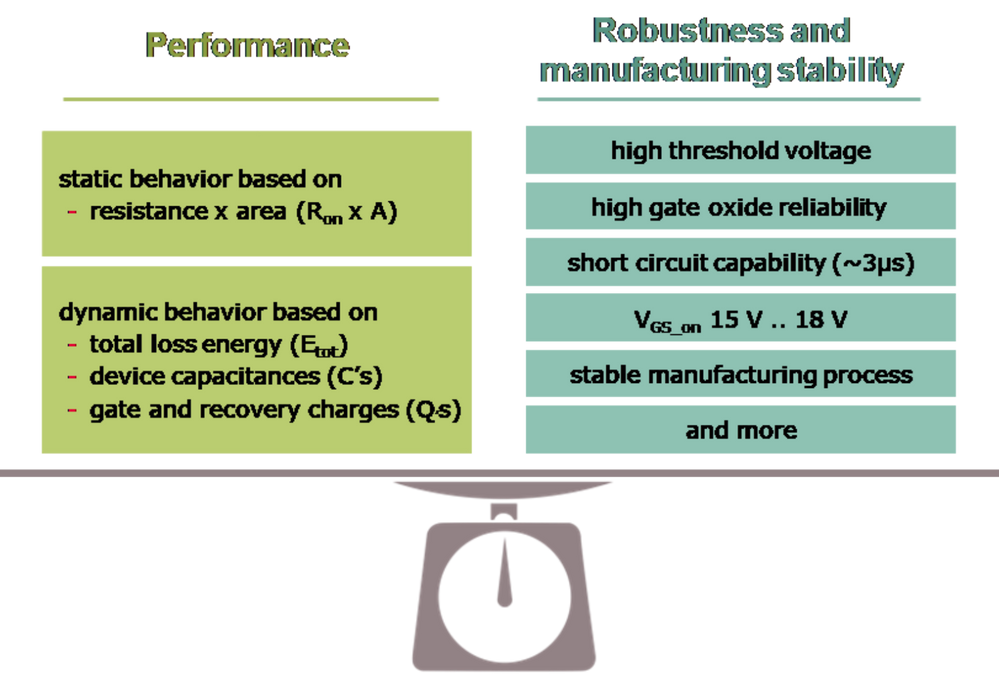

SiC MOSFET的設計挑戰——如何平衡性能與可靠性

為何使用 SiC MOSFET

使用SiC-SBD的優勢

SiC功率模塊的柵極驅動其1

SiC功率器件SiC-MOSFET的特點

SiC技術怎么應對汽車電子的挑戰

GaN和SiC區別

比亞迪SiC功率半導體的應用優勢和挑戰

SiC功率器件的新發展和挑戰!

使用SiC技術應對能源基礎設施的挑戰

安森美SiC cascode JFET并聯設計的挑戰

評論