本文由半導體產業縱橫(ID:ICVIEWS)編譯自semianalysis

晶體管的未來。

任何芯片的基本組成部分都是晶體管,最近晶體管迎來了 75 歲生日。今天我們將討論它的下一個 25 年。

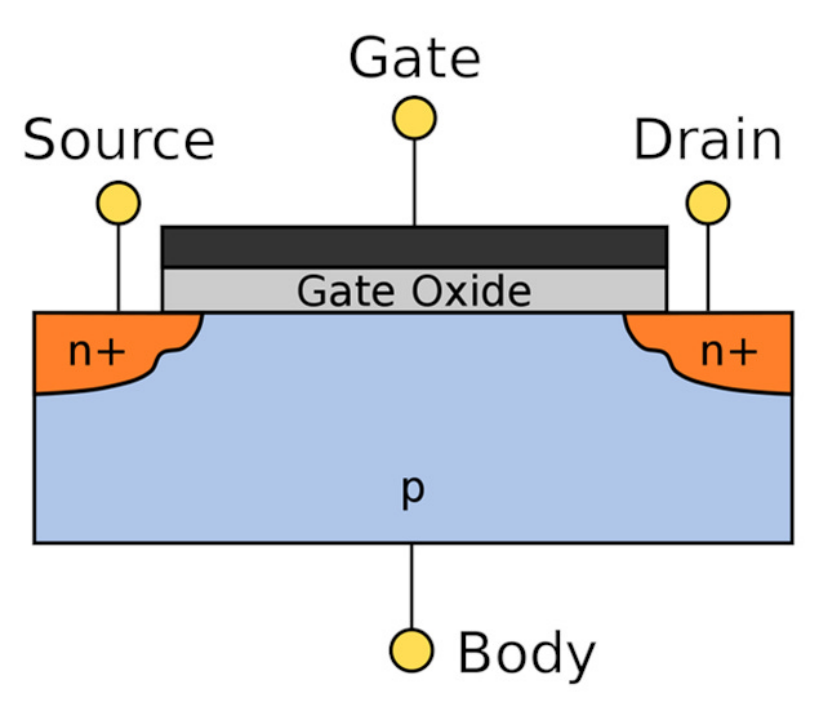

晶體管本質上是電流開關,施加到其“柵極”的電壓會導致電流在“源極”和“漏極”之間的通道中流動。每個晶體管都可以打開或關閉,對應于“1”或“0”。在摩爾定律擴展和 CMOS 工藝技術改進的推動下,現代計算芯片在數十億甚至萬億的規模上做到了這一點。

理想的晶體管可以執行以下操作:

1.開啟時傳導最大電流量。

2.關閉時不允許任何電流流動。

3.盡快切換。

晶體管的三個主要組成部分:“柵極”、“源極”和“漏極”

晶體管簡史

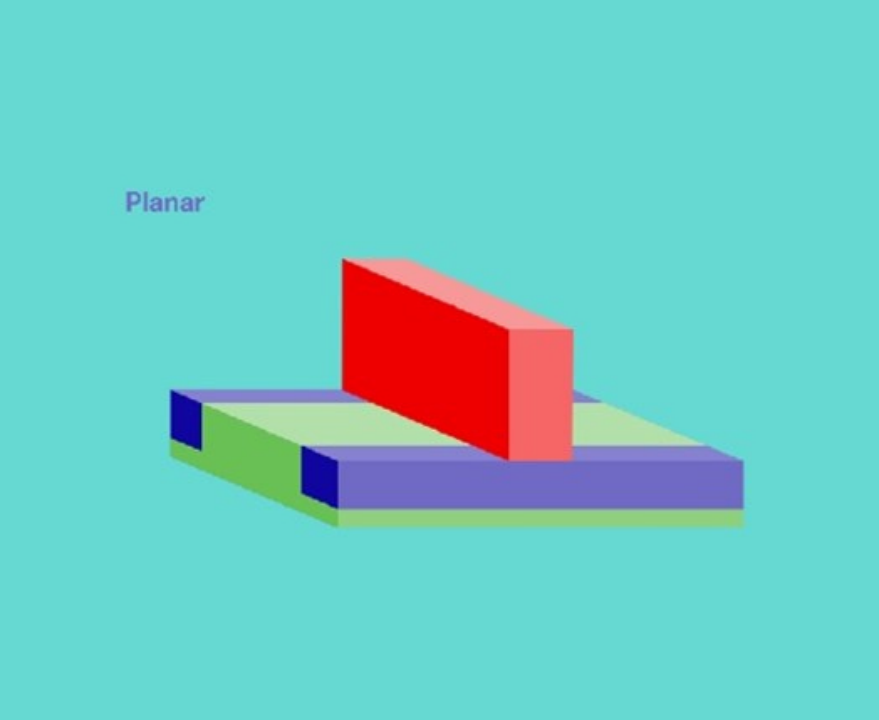

1947 年,約翰·巴丁 (John Bardeen)、威廉·肖克利 (William Shockley) 和沃爾特·布拉頓 (Walter Brattain) 在 AT T 的貝爾實驗室發明了第一批晶體管,稱為“平面”晶體管,因為晶體管的所有元件,包括柵極、源極和漏極都位于二維平面上。

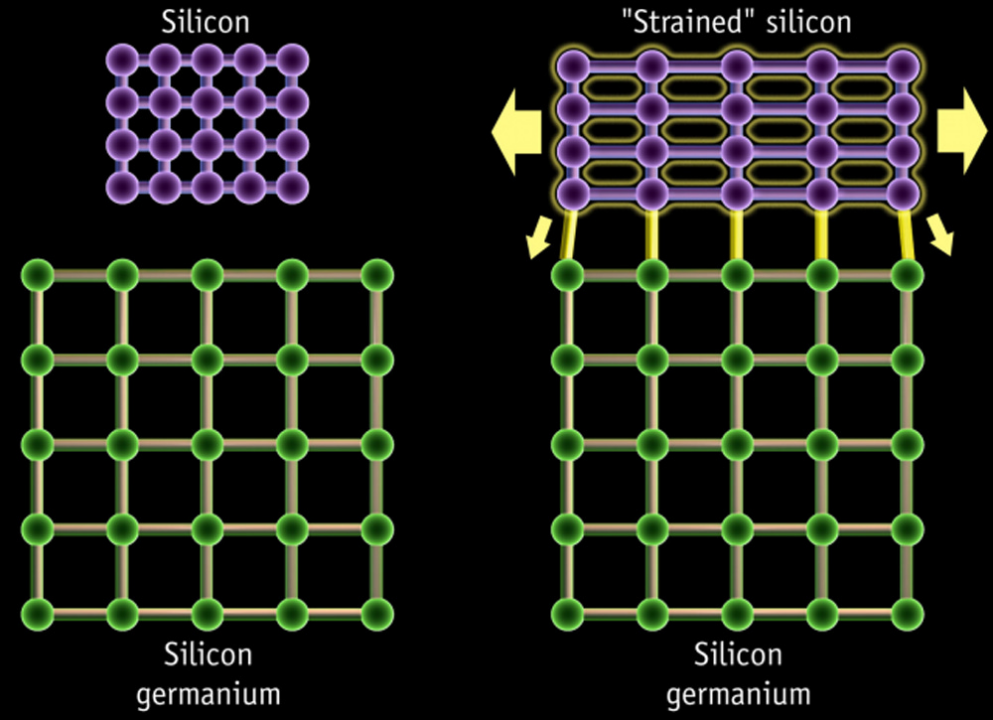

許多迭代以來,平面晶體管的開關速度可以通過縮短柵極長度來提高。“拉緊”硅通道也會提高開關速度。為了應變通道,將一層硅放置在一層硅鍺 (SiGe) 上。由于硅層中的原子與 SiGe 層對齊,這導致硅原子之間的連接拉伸,從而使溝道應變。在這種配置中,硅原子距離更遠,干擾電子運動的原子力減少。在應變通道中,電子遷移率(即電子在被電場牽引時的移動速度)提高了 70%,從而使晶體管開關速度提高了 35%。

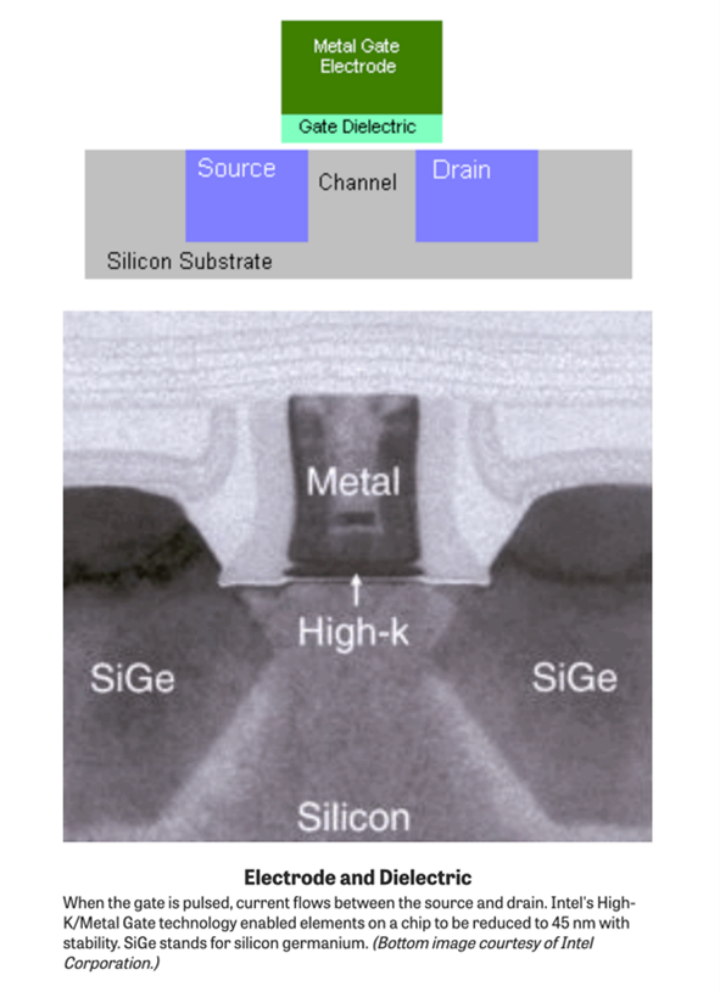

允許繼續縮放的進一步發展是“高 K/金屬”門的開發。在 45nm 節點,柵極電介質開始失去其絕緣(介電)質量并表現出過多的泄漏電流(即當晶體管處于關斷狀態時,大量電流會流過晶體管)。

柵極電介質是一個非常薄的絕緣層,通常由二氧化硅制成,位于晶體管的金屬柵電極和電流流過的通道之間。英特爾在其 45 納米工藝(2007 年)中取得重大突破,采用鉿基介電層和由替代金屬材料組成的柵電極。三年后,該行業的其他公司也紛紛效仿。由此產生的組合產生了“高介電常數”或“高 K”柵極。

隨著晶體管尺寸的不斷減小,源極和漏極之間的空間減小到柵極失去適當控制溝道中電流流動的能力的程度。正因為如此,平面晶體管表現出明顯的“短溝道”效應,尤其是在 28nm 節點以下,漏電流過大。

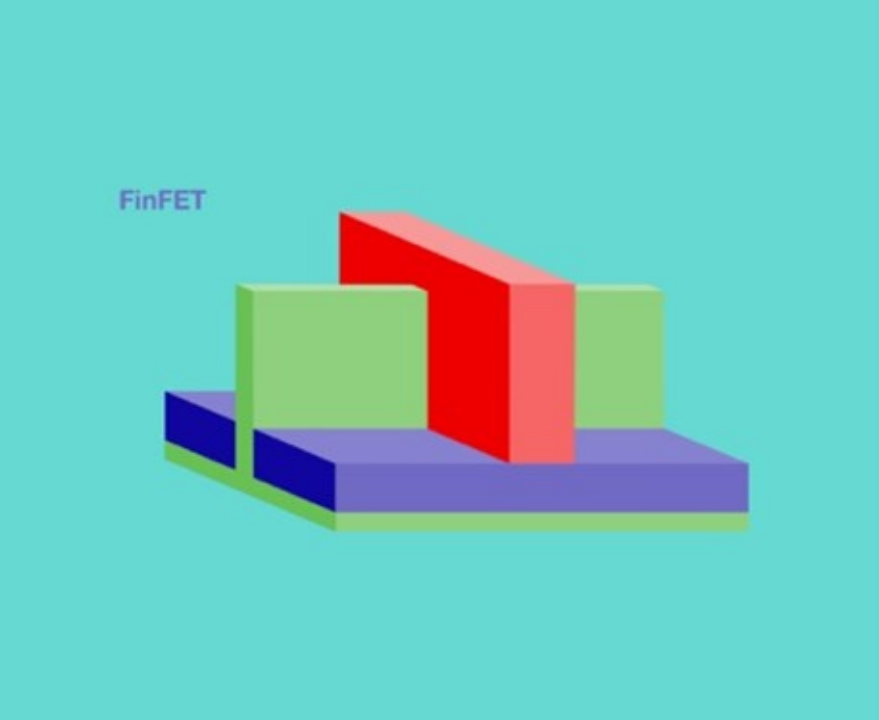

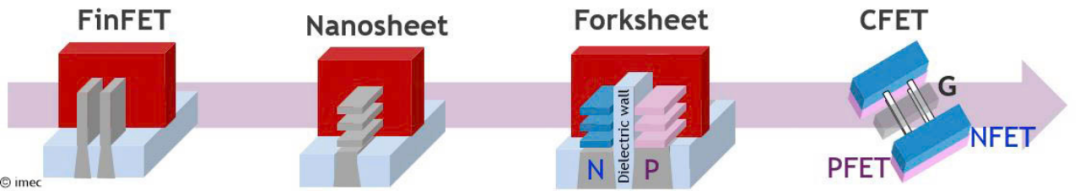

為了應對這一挑戰,業界轉向“3D”晶體管,即 FinFET。在 FinFET 中,柵極在硅鰭的三個側面環繞溝道,而不是像平面晶體管那樣僅在頂部環繞。這樣可以更好地控制流過晶體管的電流;FinFET 晶體管的開關時間明顯快于平面晶體管。在 2010 年代初期,英特爾開始生產 22 納米節點的 FinFET,而臺積電等代工廠在 3 年后開始生產 16 納米節點的 FinFET。

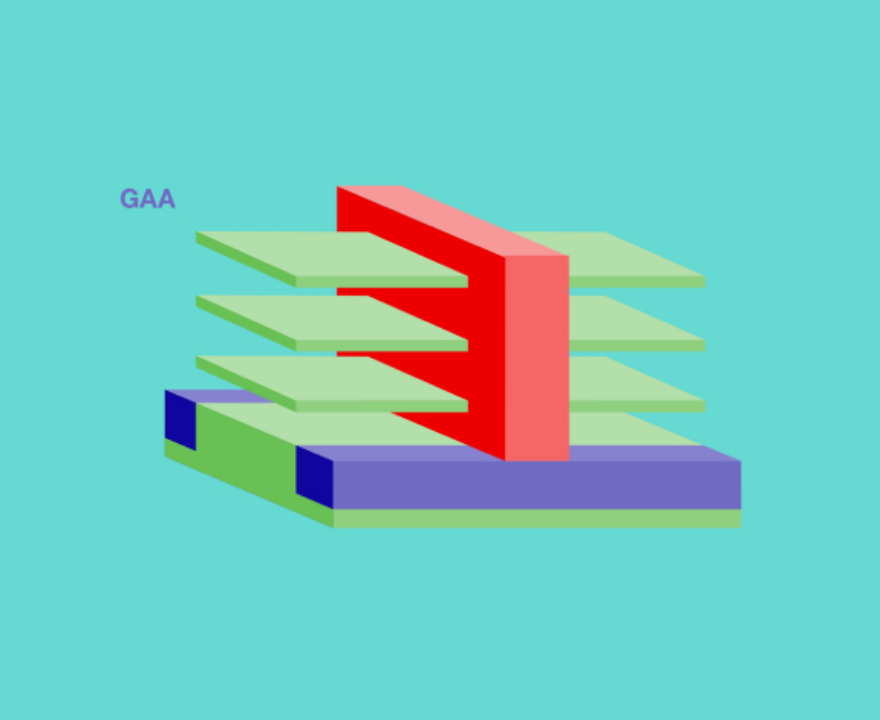

由于可以制造多薄/多高的鰭片以及可以并排放置多少鰭片的限制,晶體管的另一種發展目前正在行業中進行。這些下一代晶體管被稱為“Gate-All-Around”晶體管,或 GAAFET。GAAFET使用堆疊的水平“納米片”,因此柵極在所有 4 個側面都圍繞著通道。這進一步增加了晶體管的驅動電流和整體性能。每個納米片的寬度以及每個晶體管中的納米片數量都可以變化,從而允許定制設計。

2022 年,三星開始在其 3nm 工藝中使用 GAA。由于良率問題,三星 3nm GAP 的大批量芯片有望在 2024 年實現量產。英特爾的 20A 工藝節點路線圖上有 GAA,該工藝節點將于 2024 年制造就緒,產品將于 2025 年批量出貨。臺積電的 N2 有 GAA 2025 年或 2026 年的工藝節點。這些生產年份是目標,我們認為,這些參與者中至少有 2 個可能會進一步延遲。

除了最初的 GAA 工藝之外,還包括轉向 forksheet 或 3D 互補 FET (CFET),其中 n 和 p 通道移動得更近或垂直堆疊。

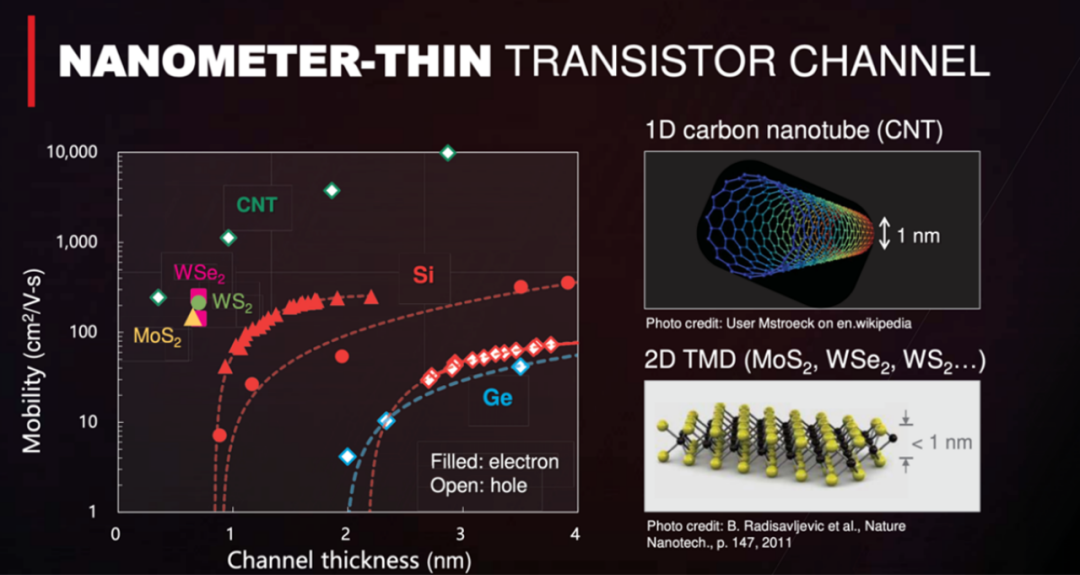

為了繼續超越 2nm 的路線圖,向 Gate-All-Around 的過渡也將需要用于納米片的新晶體管通道材料。這是因為硅和鍺等塊狀材料中的電子遷移率顯著下降 < 5nm。隨著我們深入到納米尺度,原子效應不再被忽視。也許應對這些挑戰的最佳材料系列是二維材料.。

二維材料

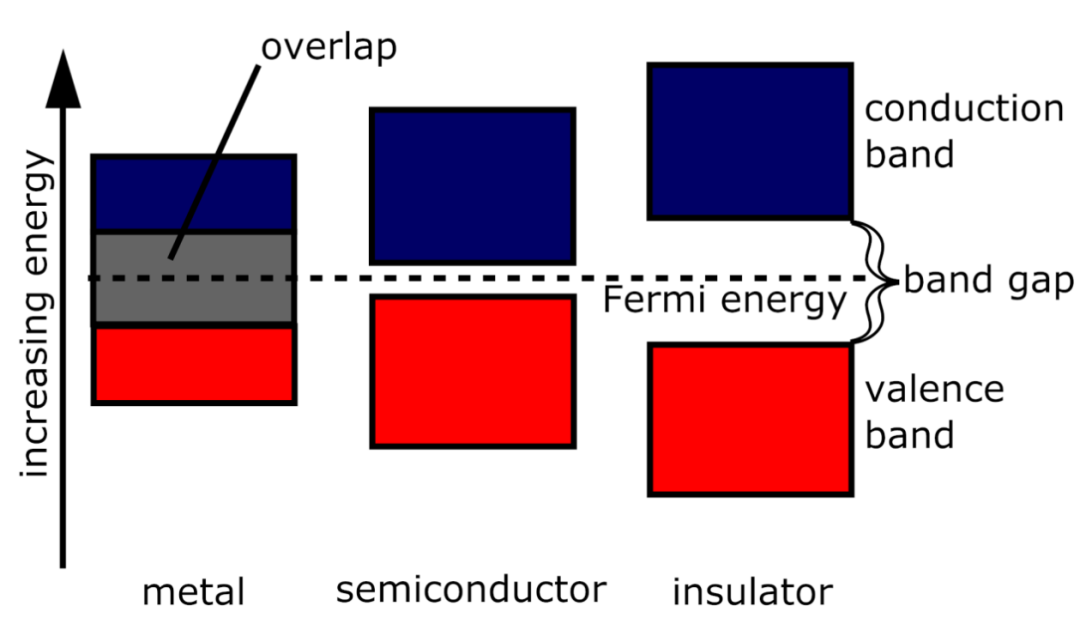

二維材料是由單層原子組成的結晶固體。最著名的二維材料是石墨烯,它是一種碳的同素異形體,由排列在六邊形晶格中的單層原子組成。但是,需要注意的是石墨烯沒有帶隙。

半導體由它們的帶隙定義:將卡在價帶中的電子激發到它可以導電的導帶所需的能量。帶隙需要足夠大,以便晶體管的開和關狀態之間有明顯的對比,這樣它就可以在不產生錯誤的情況下處理信息。盡管具有高電子遷移率,但沒有帶隙,石墨烯不能用作半導體材料。盡管石墨烯在摻雜時具有帶隙,但摻雜的石墨烯不允許足夠低的關斷電流或足夠高的導通電流。

MoS用于下一代納米片的最有前途的二維材料來自“過渡金屬二硫化物”或“TMD”子系列。來自該組的材料包括二硫化鉬 (MoS2),TMDs具有 < 5nm 通道厚度所需的帶隙 + 遷移率組合。?

雖然碳納米管(CNT,一種一維材料)也受到關注,但經過 30 多年的研發,它們的制造難度仍然很高。為了實現晶體管應用所需的性能指標,必須生長數百萬個單獨的管(即密度)并以相同的方式對齊。二維材料的用途要廣泛得多,指的是一整套材料,而且理論上比碳納米管更容易制造。

二維材料生長

二維材料通常通過化學氣相沉積 (CVD) 生長,盡管最近的努力還包括原子層沉積 (ALD)。根據襯底和參數的選擇,二維薄膜生長可以是單層或多層。

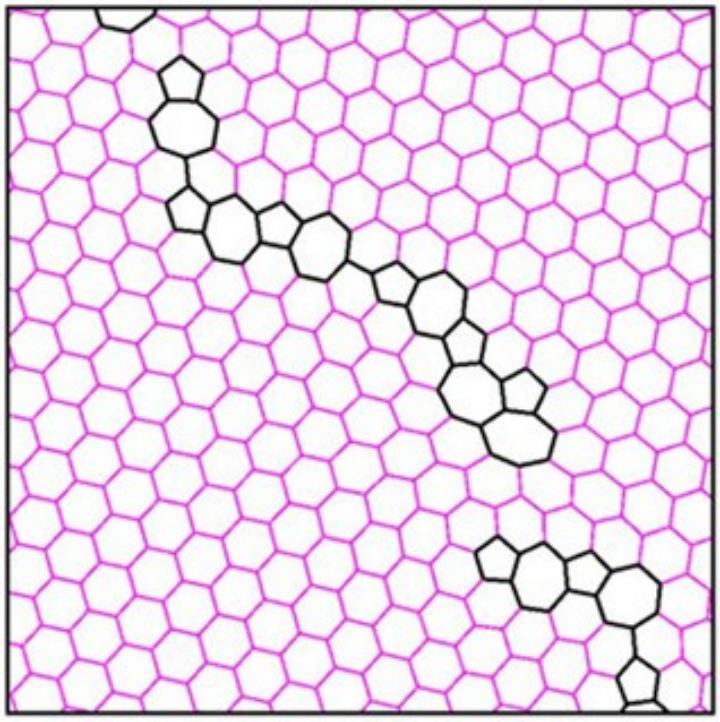

例如,單層石墨烯(最成熟的二維材料)如今主要通過 CVD 在銅箔或薄膜基板上生長。然而,目前的 CVD 生長技術產生的“多晶”石墨烯在晶格中具有多個晶界。生長也是可變的,這意味著晶圓與晶圓之間的一致性很難實現。

由于存在晶界和其他缺陷,CVD 石墨烯固有的電子遷移率通常仍遠低于10,000 cm-2/(V?s),與 2000 年原始剝離石墨烯薄片報道的200,000 cm2/(V?s), 相差的載流子密度為10 12 cm-2。

石墨烯 CVD 生長過程中出現的“晶界”示例。這種生長被稱為“多晶”

因此,今天的石墨烯電子市場可以忽略不計,一些參與者主要專注于傳感器(例如:霍爾效應)或 mems 設備(限制較少的光刻規則/更大的線寬,可以容忍更高的可變性等)。因為石墨烯具有生物相容性,可以通過場效應傳感進行功能化以檢測各種分子化合物,Cardea Bio 和 GrapheneDX 等公司特別致力于石墨烯生物傳感器。歐洲的 Graphenea 和 Applied Nanolayers 等其他公司正在建設專門的石墨烯晶圓廠。

要認真對待二維材料,必須開發更一致的晶圓到晶圓生長工藝,以實現長期“單晶”材料的目標。Aixtron 和 Oxford Instruments 目前是唯一一家銷售二維材料專用生長工具的 OEM。

二維材料轉移

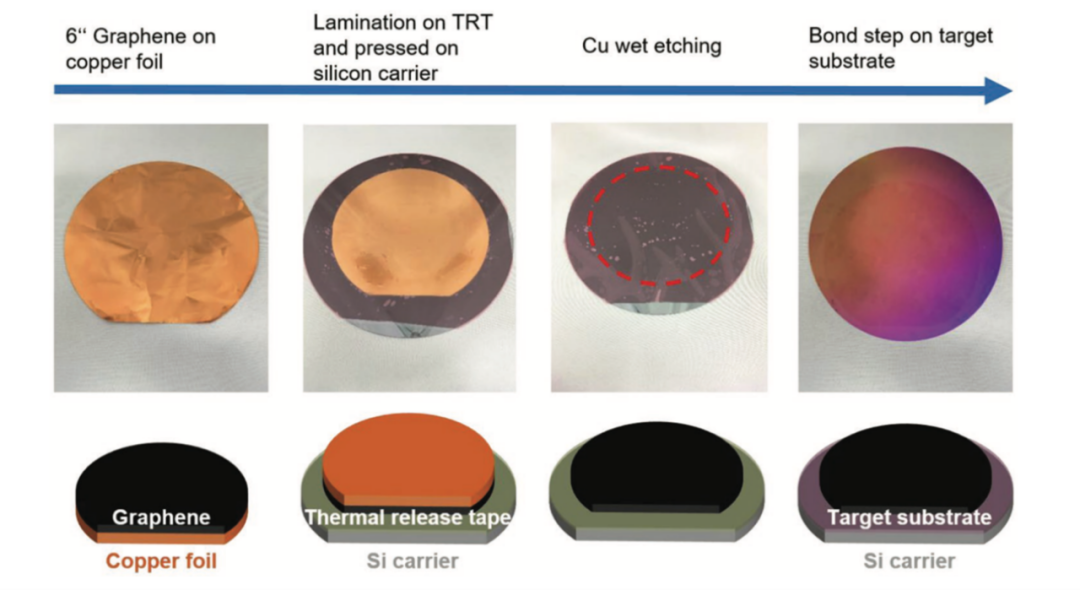

由于二維材料生長通常在較高溫度 (>600° C) 下在銅或藍寶石等優化襯底上進行,因此需要一個轉移步驟將二維材料轉移到最終的硅晶圓上。

目前將二維材料從其生長基板轉移到目標硅器件晶圓的方法不足以滿足 CMOS 市場(需要濕化學/蝕刻劑、金屬沉積、犧牲聚合物層、熱釋放膠帶 [TRT] 的某種組合,它會留下殘留物,以及/或激光剝離)。最傳統的 2D 轉移技術涉及濕法蝕刻銅基板,并使用聚合物聚甲基丙烯酸甲酯 (PMMA) 拾取二維材料并將其移動到目標基板。然而,PMMA殘留物在轉移后殘留在石墨烯表面并降低了石墨烯的電性能。

今天的二維材料轉移方法足以滿足傳感器或“顯示器等某些設備的要求,但在質量、產量和污染方面并沒有掃清 CMOS 的障礙。

目前用于石墨烯的示例轉移過程。

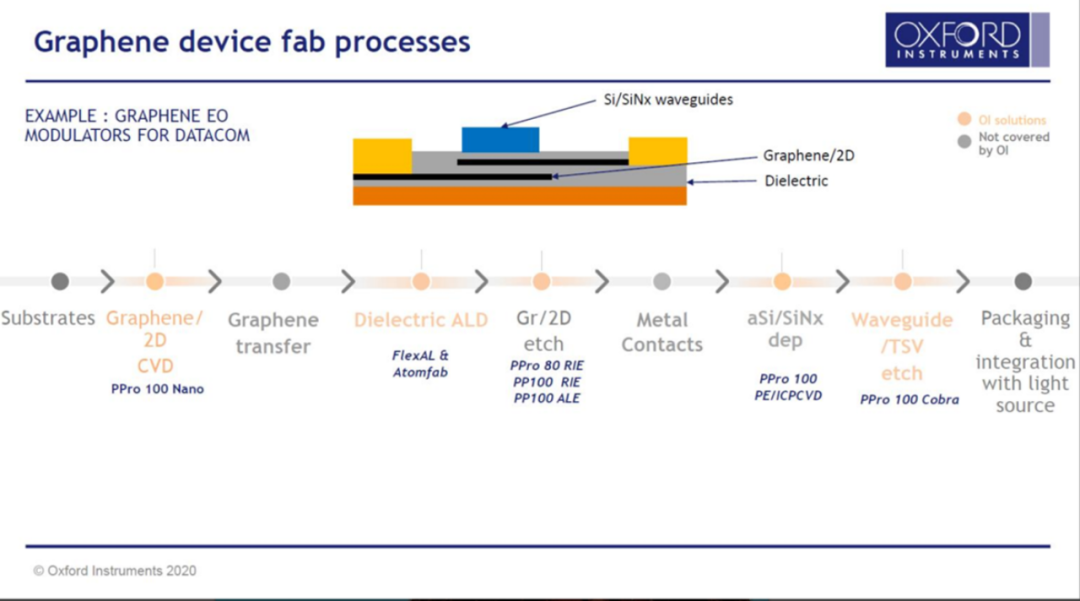

Oxford Instruments 的石墨烯器件工藝流程示例

直接增長與轉移

雖然二維材料在硅上的直接生長是首選,但迄今為止,很難實現低溫、高質量的生長解決方案。ALD 允許比傳統的金屬有機 CVD 或 MOCVD 更低的溫度,但吞吐量仍然很慢。

將優化基板上較慢、高質量的生長步驟與高通量、優化的轉移步驟分離可能更好。這將允許更好的過程優化和產量控制。這在前沿處理昂貴的2nm以下、高 NA EUV + GAA 晶圓時可能是最好的選擇(特別是如果每個晶體管需要多個納米片)。

去耦對晶圓廠也很友好,因為增長和轉移可以異步完成,以確保最大的晶圓廠生產線利用率(實現更高的 WPH 數量)。最后,轉移更通用,允許異質結構、堆疊和扭曲配置比直接生長更容易。從長遠來看,這有可能打開二維扭電子領域

IEDM二維材料亮點

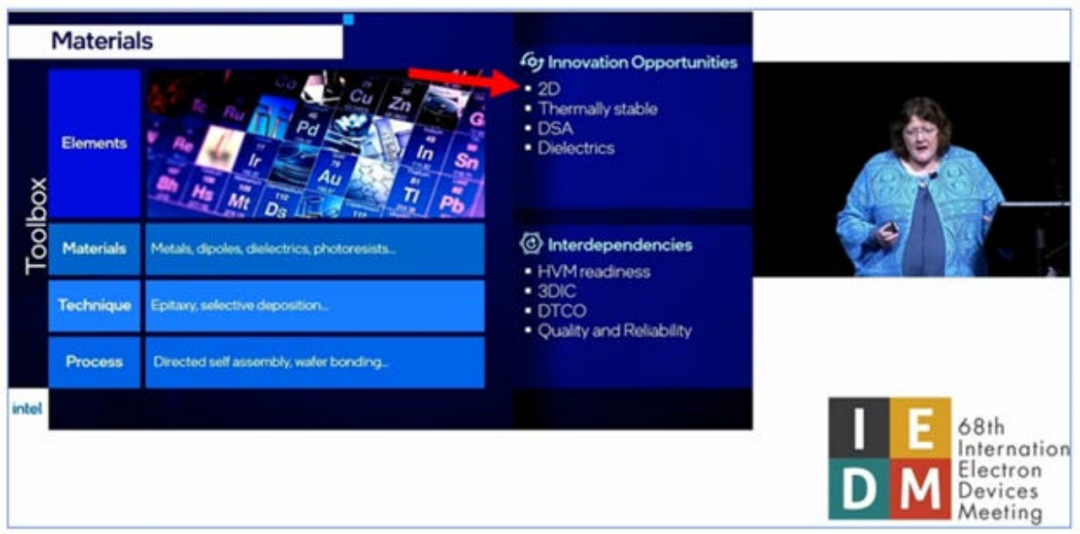

在舊金山舉行的第 68 屆年度 IEDM 會議為半導體和計算行業的未來提供了一個很好的視角。在出席的行業領導者的演講中英特爾紀念了晶體管問世 75 周年,它既回顧了過去,也展望了未來。

IEDM 上的主題演講,“慶祝晶體管誕生 75 周年!展望下一代創新機會

隨著摩爾定律的放緩,無論是后硅通道世界還是封裝技術,新技術都會推動性能提升。英特爾的演講提出了三個可能推動行業發展和擴大目標的領域:新型電介質、定向自組裝(用于納米圖案化)和二維材料。

尤其是二維材料,在會議上大放異彩。該行業在不久的將來有一個清晰的路線圖,FinFET 和 GAA 架構將擴展硅通道的統治地位。

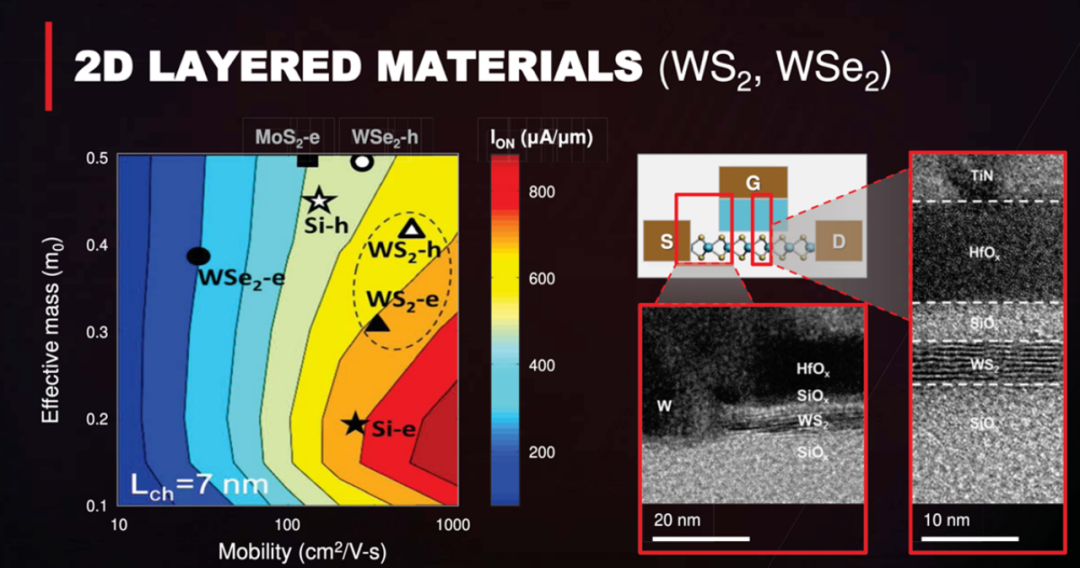

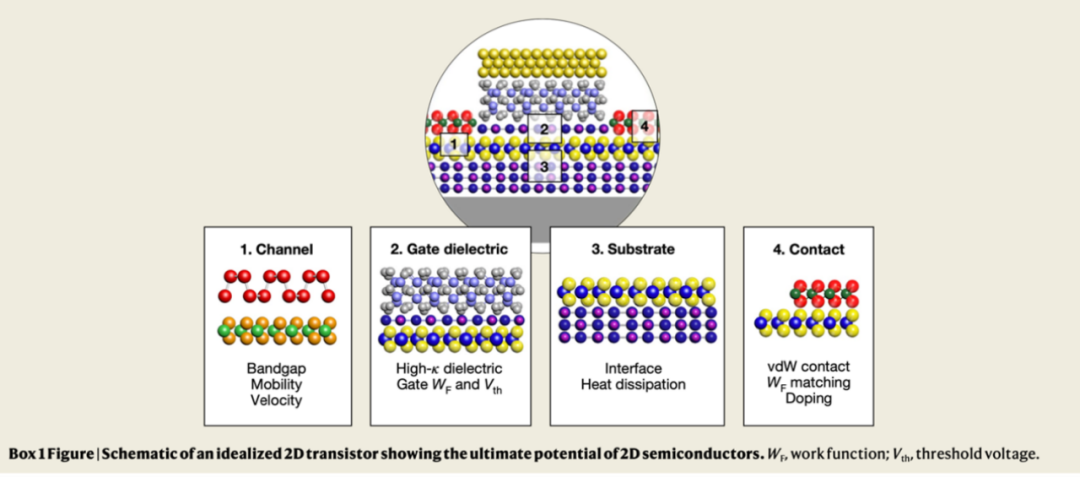

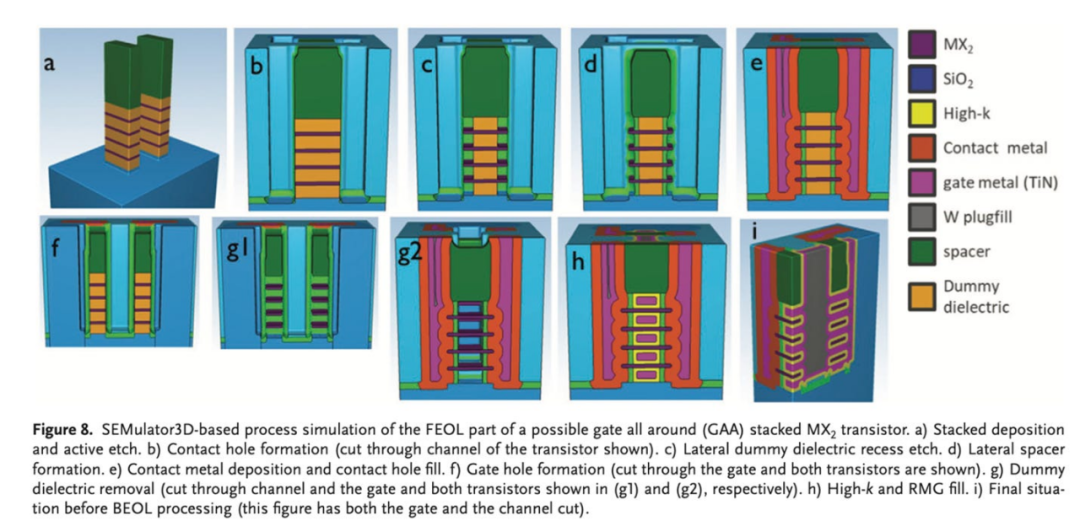

英特爾展示了 GAA 結構中的二維材料通道,具有低泄漏和近乎理想的開關,這是垂直堆疊晶體管的重要一步。IMEC 的路線圖引入了互補 FET (CFET) 作為類似的解決方案,其中堆疊了基于單層過渡金屬二硫化物 (TMD)(例如 WS2or MoS或 MoS2)的 n 和 p 通道。

在 IEDM 上,有一個專門針對 2D 通道技術的會議,由斯坦福大學的 Eric Pop 博士和 IBM 高級 CMOS 邏輯計劃的 Nicolas Loubet 共同主持。演示文稿側重于 2D 晶體管的各個方面,包括溝道、柵極電介質、所需的基板/材料,以及降低接觸電阻以提高器件性能。以下是對其中一些論文的技術評論:

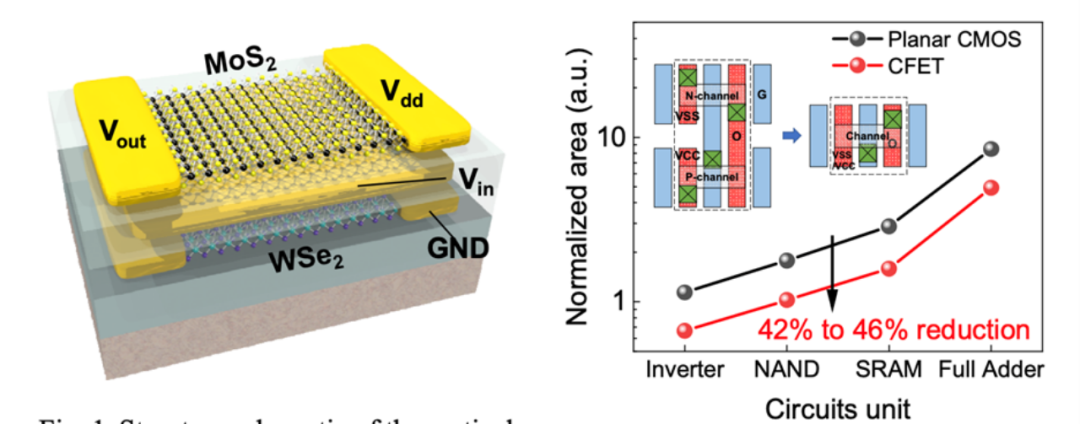

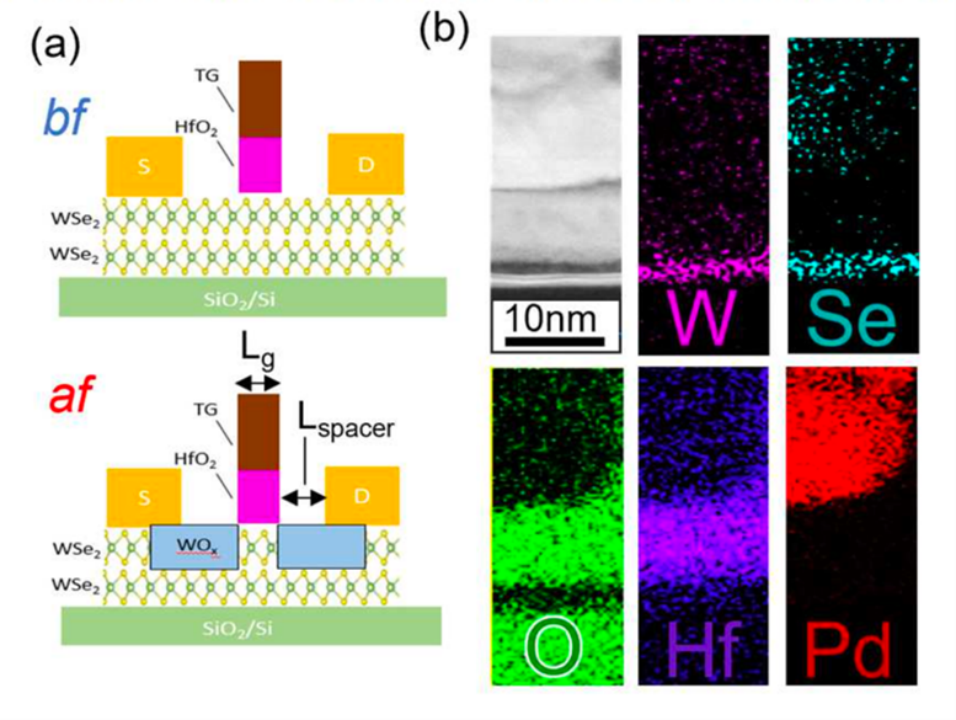

北京大學在中國的研究展示了頂部門控CVD生長的WSe2pFETs,其漏電流為594 UA/um,此外還有基于WSe2/MoS2的CFET。與傳統的平面集成電路相比,CFET結構的性能提高了8%,面積減少了44%。在可制造性方面,許多挑戰仍然存在。本文演示的CFET幾乎是以一種與FAB兼容的方式制造的,除了用于nFET中MoS2通道的濕傳遞技術之外。可伸縮的干轉移技術對于將這種技術轉移到生產中至關重要。

二維 CFET 結構和集成面積縮減。垂直堆疊可以在不損失性能的情況下產生更高密度的組件。在這種垂直疊加方法中的一個研究與開發挑戰主要是在放置源和漏觸點以及為互連選擇接觸材料方面。

臺積電在另一篇IEDM論文中,對SiN2上轉移MoSe2溝道器件的理想材料提供了深入的見解。選擇接觸材料的挑戰在于尋找理想的工作函數和較弱的費米能級釘扎效應的結合,臺積電選擇了利用一層薄銻(SB)和高功函數鉑(Pt)來實現這一目標。這種努力展現了最低的報告接觸電阻,0.75kΩ-um用于pFET,1.8kΩ-um在nFET中。在nFET中,這意味著接觸電阻比以前報告的值減少72%,這意味著向邏輯應用的2D通道前進了一大步。

接觸電阻只是器件總電阻的一個組成部分;間隔電阻是導致器件性能不佳的另一個主要因素,特別是在pFET中。臺積電在另一篇IEDM論文中,利用氧化多層WSe2與WSe2通道結合形成的WOx作為低電阻間隔摻雜劑。WO x作為高p摻雜劑,被發現可以降低肖特基勢壘高度,盡管加入摻雜劑(1 kΩ-um),但導致總電阻降低。

雖然基于 TMD 的設備很有前途,但 TMD 生長方法存在一個根本問題。基于轉移的方法會留下聚合物殘留物,而使用 MOCVD 在氧化物上直接生長會導致各種缺陷,最顯著的是有機污染物和硫空位。IEDM 精選了一些同時使用遷移和直接增長方法的論文。

英特爾推出了一款基于轉移二硫化鉬的2D FET,源漏接觸長度為25 nm,與當前的硅工藝節點相當。測試的器件顯示了上升亞閾值擺幅(SS at=75 mV/dec)低于34納米的源漏距離。然而,英特爾的工藝使用了使用ALD生長的犧牲介電層的層轉移工藝,這留下了大量的殘留物,并導致源極和漏極接觸處的MoS2分層。為了制造和未來的產量目標,轉移方法必須是無殘留和干燥的,或采用直接生長的方法。

會議還討論了直接增長的進展,觀察到更多使用 CVD 的晶圓廠兼容工藝。北京大學的一篇論文討論了具有低接觸電阻 (0.65 kΩ-μm) 的純歐姆的 WSe2pFET。該器件的通道長度為 120 nm,在 6 nm SiO2上生長時,性能數據創下紀錄(Ids= 425μA/μm,gm=80μS/μm,SSsat=200 mV/dec)。該工藝也與在 Si/HfLaO2介電薄膜上的生長兼容,但性能稍差(Ids=370μA/μm,gm=100μS/μm,SSsat=250 mV/dec)。然而,第一個設備制造過程中的高加工溫度 (890° C) 對可制造性構成了晶圓廠兼容性風險。不過,這項工作確實代表了 p 型二維 TMD 材料的巨大進步,這是二維材料中需要開發的一個領域。

二維材料還用于使用 hBN 作為封裝層的 MoS2晶體管的介電界面工程。這項工作導致了 CVD 生長的單層 MoS2器件報告的最低亞閾值擺動。封裝層似乎也提高了器件可靠性,在播種鋁和頂柵沉積后表現出較少的斷態退化,表明介電層最大限度地減少了進一步加工造成的損壞。這代表了基于二維材料的設備可靠性和使用壽命的進步。當使用鉭 (Ta) 晶種層作為 TaOx 摻雜層時,據報道大的 Ids = 861μA/μm 和低亞閾值擺幅 (72 mV/dec),而對于低功率應用,高 IDs = 598 μA/μm據報道,Vds=0.65 V,超過 IRDS 2028 HD 規格。

所討論的 2D 進步僅代表二維材料革新行業的潛力的一小部分。然而,要將 2D 轉化為晶圓廠級別的大批量制造,仍然存在重大挑戰。上述所有論文都利用濕轉移技術將二維材料從生長基板轉移到生產晶圓。如上所述,雖然有望說明設備潛力,但由于可能存在聚合物殘留和較低的吞吐量,這種方法無法擴展到大批量生產。

隨著每一次 IEDM 會議的召開,半導體行業的前進道路變得更加清晰:2D 是未來,而且在這些筆者看來,這是不可避免的。截至目前,前沿討論方向似乎更青睞 WS2和 WSe2,因為它們既可以制成 n 型,也可以制成 p 型。

二維材料顯然是該行業的未來,有很大的動力推動該領域向前發展。隨著二維材料進入半導體堆棧,還需要開發有效在線表征它們的工具。為此,即將在 SPIE 光刻和圖案化會議上舉行的會談討論了計量學的前景以及英特爾和 IMEC 會談:

二維過渡金屬二硫化物晶體管是未來的硅替代品還是炒作?

用于表征超薄二維材料層的 300 毫米在線計量

此外,領導歐盟石墨烯旗艦 2D 實驗試點項目的 IMEC 將在下個月的研討會上展示最新進展;參與者還包括英特爾和臺積電。

行業的下一步

任何新材料/工藝技術的第一步都是進入行業路線圖。過去的幾次 IEDM 和即將召開的 SPIE Advanced Lithography 會議清楚地表明,二維材料現在已經穩穩地出現在路線圖上。然而,下一步是從路線圖到具體行動。

說起來容易做起來難,但筆者認為,二維材料應該首先在較成熟的節點(主要是在 MEMS、模擬+MS、RF 和光子代工廠)的生產線后端實施。二維材料在 MEMS、5G/6G 射頻開關和光子收發器等設備中提供了引人注目的性能提升。與晶體管相比,這些設備中的一些不需要最高質量的起始材料。

例如,原型射頻開關設備(由 hBN 和 MoS2等二維材料制成)已在 UT 奧斯汀實驗室以及羅德與施瓦茨等合作伙伴進行了演示和表征。來自主要行業參與者的初始數據和反饋表明,二維開關的經典品質因數 (FoM),即“Ron x Coff 值”,達到甚至超過了對新興網絡頻段的預期。

在硅光子學中,目前調制器和光電探測器分別制造并組裝在芯片中;使用二維材料,收發器的所有組件,包括調制器、開關和光電探測器,都可以在同一2D層中整體制造。目前的調制器材料,如 LiNBO3,體積龐大,需要 2-5 V 的驅動電壓。石墨烯 Mach-Zedhner (MZ) 調制器可以用 <1 V 的電壓制造。諾基亞意大利、愛立信和位于亞琛的 Black Semiconductor 都在努力在這個方向。

二維材料還可以實現更快的光學切換。可重構光分插復用器 (ROADM) 中的切換目前不能低于數十毫秒。例如,放置在微環諧振器頂部的石墨烯可以實現皮秒級的開關。

一旦在后端解決了工藝、計量和良率問題,并且隨著二維材料生長和轉移質量的提高,該行業在生產線的前沿/前端集成二維材料的路徑就會更加清晰。在此期間,前沿社區需要解決接觸電阻、基板/電介質材料和架構(例如:納米片的數量)等問題,以達到必要的設備性能指標。

每當該行業必須解決一項主要的材料/工藝技術以保持摩爾定律的發展時,它就會交付。離子注入、高 K 門、EUV ……有很多例子,二維材料也不例外。然而,使二維材料成為現實所需的制造技術目前正處于“死亡谷”階段,因此需要整個行業(來自所有領域,尤其是 OEM、代工/無晶圓廠/IDM、和計量學)。

正如 Sri Samavedam(高級副總裁 CMOS 技術,IMEC)最近提到的那樣,“在這個行業中,從展示一個概念到引入制造通常需要大約 20 年的時間。可以安全地假設 2047(標志著晶體管誕生 100 周年)的晶體管或開關架構已經在實驗室規模上得到了證明。”

審核編輯 黃宇

-

芯片

+關注

關注

456文章

51154瀏覽量

426214 -

晶體管

+關注

關注

77文章

9744瀏覽量

138709

發布評論請先 登錄

相關推薦

絕緣柵雙極晶體管(IGBT)

晶體管的由來

SGNE045MK晶體管

什么是晶體管 晶體管的分類及主要參數

什么是達林頓晶體管?

8050晶體管介紹 8050晶體管的工作原理

基本晶體管開關電路,使用晶體管開關的關鍵要點

下一代晶體管露臉

一個CPU上有多少晶體管?

一個芯片集成多少晶體管

晶體管的三個極是什么_判斷晶體管的三個電極

晶體管的第一個76年:變小了,卻變大了?

晶體管的下一個25年

晶體管的下一個25年

評論