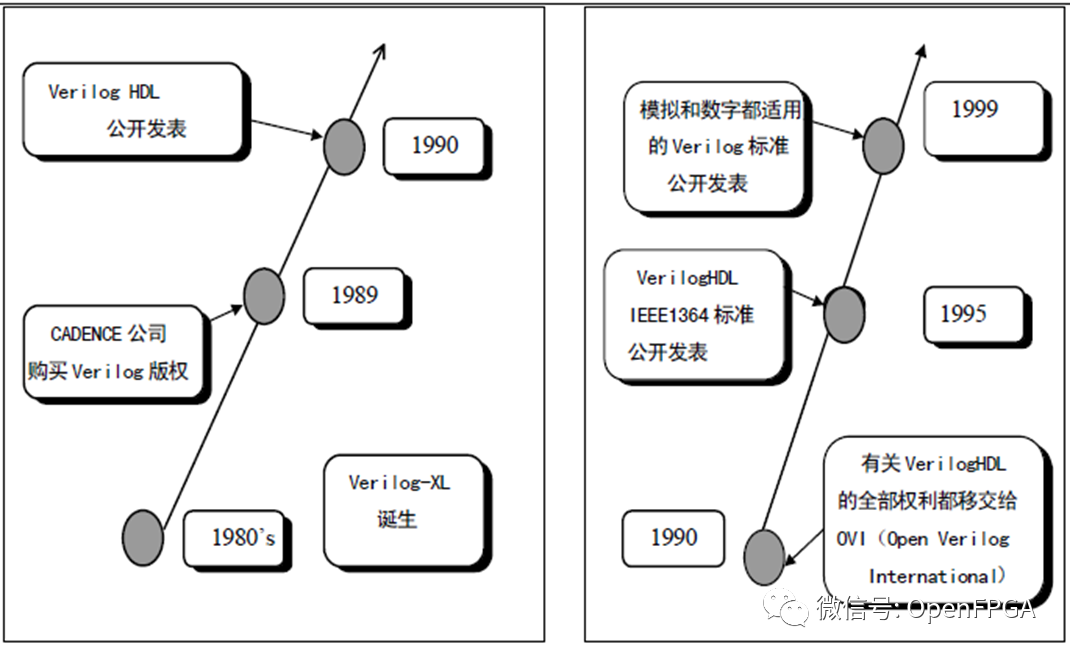

Verilog和System Verilog是同一硬件描述語(yǔ)言(HDL)的同義名稱(chēng)。SystemVerilog是IEEE官方語(yǔ)言標(biāo)準(zhǔn)的較新名稱(chēng),它取代了原來(lái)的Verilog名稱(chēng)。Verilog HDL語(yǔ)言最初是于1 9 8 3年由Gateway Design Automation 公司為其模擬器產(chǎn)品開(kāi)發(fā)的硬件建模語(yǔ)言。那時(shí)它只是一種專(zhuān)用語(yǔ)言。專(zhuān)有的Verilog HDL于1989年逐漸向公眾開(kāi)放,并于1995年由IEEE標(biāo)準(zhǔn)化為國(guó)際標(biāo)準(zhǔn),即IEEE Std 1364-1995TM(通常稱(chēng)為“Verilog-95”)。IEEE于2001年將Verilog標(biāo)準(zhǔn)更新為1364-2001 TM標(biāo)準(zhǔn),稱(chēng)為“Verilog-2001”。Verilog名稱(chēng)下的最后一個(gè)官方版本是IEEE Std 1364-2005TM。同年,IEEE發(fā)布了一系列對(duì)Verilog HDL的增強(qiáng)功能。

這些增強(qiáng)功能最初以不同的標(biāo)準(zhǔn)編號(hào)和名稱(chēng)記錄,即IEEE Std 1800-2005TM SystemVerilog標(biāo)準(zhǔn)。2009年,IEEE終止了IEEE-1364標(biāo)準(zhǔn),并將Verilog-2005合并到SystemVerilog標(biāo)準(zhǔn)中,標(biāo)準(zhǔn)編號(hào)為IEEE Std 1800-2009TM標(biāo)準(zhǔn)。2012年增加了其他設(shè)計(jì)和驗(yàn)證增強(qiáng)功能,如IEEE標(biāo)準(zhǔn)1800-2012TM標(biāo)準(zhǔn),稱(chēng)為SystemVerilog-2012。在撰寫(xiě)本書(shū)時(shí),IEEE已接近完成擬定的IEEE標(biāo)準(zhǔn)1800-2017TM或SystemVerilog-2017。本版本僅修正了2012版標(biāo)準(zhǔn)中的勘誤表,并增加了對(duì)語(yǔ)言語(yǔ)法和語(yǔ)義規(guī)則的澄清。

verilog的發(fā)展歷史及未來(lái)

原始Verilog

Verilog始于20世紀(jì)80年代初,是一家名為Gateway Design Automation的公司的專(zhuān)有硬件描述語(yǔ)言(HDL)。最初的Verilog HDL的主要作者是Phil Moorby。在20世紀(jì)80年代早期,數(shù)字仿真開(kāi)始流行。一些電子設(shè)計(jì)自動(dòng)化(EDA)公司提供了數(shù)字仿真器,但這些仿真器沒(méi)有標(biāo)準(zhǔn)的硬件描述語(yǔ)言。相反,每個(gè)仿真器公司都提供了一種專(zhuān)用于該仿真器的專(zhuān)有建模語(yǔ)言。網(wǎng)表(Gateway)設(shè)計(jì)自動(dòng)化也不例外。仿真器產(chǎn)品被命名為“Verilog XL”(Verification Logic,Accelerated的縮寫(xiě)),其附帶的建模語(yǔ)言被稱(chēng)為“Verilog”。

Verilog XL仿真器和Verilog HDL在20世紀(jì)80年代后半期成為數(shù)字設(shè)計(jì)的主要仿真器和語(yǔ)言。促成這種流行的一些因素包括:1)速度和容量,2)ASIC定時(shí)精度,3)集成設(shè)計(jì)和驗(yàn)證語(yǔ)言,4)數(shù)字合成。

1、Verilog XL仿真器比大多數(shù)(如果不是全部的話(huà))當(dāng)代競(jìng)爭(zhēng)對(duì)手的仿真器速度更快,設(shè)計(jì)容量更大,允許公司更有效地設(shè)計(jì)更大、更復(fù)雜的數(shù)字集成電路(IC)。

2、 在20世紀(jì)80年代后半期,許多電子設(shè)計(jì)公司正在從定制集成電路轉(zhuǎn)向?qū)S眉呻娐罚ˋSIC)。網(wǎng)表(Gateway)設(shè)計(jì)自動(dòng)化與主要ASIC供應(yīng)商密切合作,Verilog XL成為確保ASIC仿真計(jì)時(shí)準(zhǔn)確的黃金參考仿真器。ASIC供應(yīng)商的這種偏好使Verilog成為COM的首選語(yǔ)言,COM是設(shè)計(jì)ASIC的公司。

3、20世紀(jì)70年代和80年代早期的主要數(shù)字仿真器通常涉及使用兩種專(zhuān)有語(yǔ)言:門(mén)級(jí)建模語(yǔ)言來(lái)仿真數(shù)字邏輯,以及單獨(dú)的專(zhuān)有語(yǔ)言來(lái)仿真刺激和響應(yīng)檢查。網(wǎng)關(guān)設(shè)計(jì)自動(dòng)化背離了這一傳統(tǒng),將門(mén)級(jí)建模、抽象功能建模、刺激和響應(yīng)檢查集成到一種稱(chēng)為Verilog的語(yǔ)言中。

4、許多公司采用Verilog語(yǔ)言設(shè)計(jì)ASIC的第四個(gè)原因是能夠?qū)⒊橄蟮腣erilog模型合成為門(mén)級(jí)模型。20世紀(jì)80年代后半期,Synopsys,Inc.與Gateway Design Automation達(dá)成協(xié)議,在Synopsys Design Compiler(DC)數(shù)字合成工具中使用專(zhuān)有的Verilog語(yǔ)言。與當(dāng)時(shí)所有其他專(zhuān)有數(shù)字建模語(yǔ)言相比,仿真和合成Verilog語(yǔ)言的能力是一個(gè)巨大的優(yōu)勢(shì)。

開(kāi)放verilog和VHDL

Verilog語(yǔ)言的快速增長(zhǎng)和普及在20世紀(jì)90年代初突然放緩。電氣和電子工程師協(xié)會(huì)(IEEE,通常發(fā)音為“I-triple-E”)發(fā)布了VHDL語(yǔ)言,作為第一個(gè)行業(yè)標(biāo)準(zhǔn)、非專(zhuān)有硬件描述語(yǔ)言。與Verilog類(lèi)似,VHDL還提供了一種集成的數(shù)字建模和驗(yàn)證語(yǔ)言,并得到了ASIC供應(yīng)商的支持(首先是在VHDL設(shè)計(jì)流程中使用經(jīng)過(guò)認(rèn)證的Verilog ASIC庫(kù))。隨著VHDL仿真器和合成編譯器的出現(xiàn),許多設(shè)計(jì)公司開(kāi)始回避使用專(zhuān)有語(yǔ)言,包括Verilog。還有一些其他因素,比如美國(guó)國(guó)防部(DOD)授權(quán)使用VHDL作為DOD設(shè)計(jì)的文檔語(yǔ)言,也導(dǎo)致了從Verilog向VHDL的轉(zhuǎn)變(DOD不要求設(shè)計(jì)工作使用VHDL,只要求最終文檔使用VHDL)。

網(wǎng)關(guān)設(shè)計(jì)自動(dòng)化公司(Gateway Design Automation)通過(guò)將Verilog發(fā)布到公共領(lǐng)域,阻止了這種遠(yuǎn)離專(zhuān)有HDL的做法。第一步工作就是要求將Verilog語(yǔ)言文檔與Verilog XL仿真器產(chǎn)品文檔分開(kāi)。在這項(xiàng)工作進(jìn)行期間,Cadence Design Systems得到Gateway Design Automation的請(qǐng)求并完成了這項(xiàng)工作;1991年,Verilog正式成為公共領(lǐng)域語(yǔ)言,成立了一個(gè)名為Open Verilog International(OVI)的非營(yíng)利組織,目的是控制Verilog語(yǔ)言并促進(jìn)其使用。

Verilog向公共領(lǐng)域的發(fā)布有效地阻止了Verilog向VHDL的流動(dòng)。在接下來(lái)的二十年中,這兩種HDL共存,并且可以說(shuō),在全球電子設(shè)計(jì)行業(yè)中保持了某種程度上均勻的總體使用。然而,2005年SystemVerilog的出現(xiàn)打破了VHDL的平衡,而Verilog在其新名稱(chēng)SystemVerilogt下再次成為數(shù)字設(shè)計(jì)和驗(yàn)證中使用的更主要的HDL語(yǔ)言。

IEEE Verilog-95和Verilog-2001

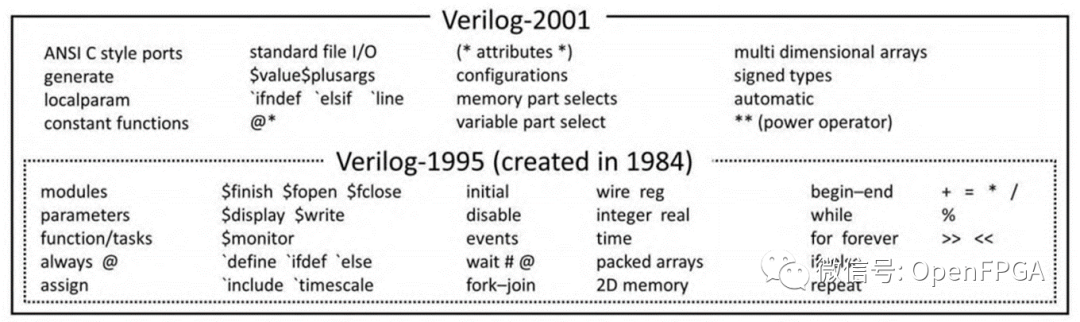

IEEE于1993年接管了Verilog語(yǔ)言,并在兩年后發(fā)布了正式的IEEE Verilog HDL標(biāo)準(zhǔn),即IEEE 1364-1995,昵稱(chēng)為“Verilog-95”。五年后,IEEE發(fā)布了1364-2001,綽號(hào)為“Verilog2001”,其中有許多用于建模和驗(yàn)證數(shù)字設(shè)計(jì)的增強(qiáng)功能。

圖1-1顯示了Verilog-95中的主要語(yǔ)言功能,以及Verilog-2001中添加的主要新功能。請(qǐng)注意,此圖并不是語(yǔ)言特性的全面列表。其目的是展示Verilog-2001添加到原始Verilog語(yǔ)言中的主要新功能。

圖1-1:Verilog-95和Verilog-2001語(yǔ)言特性

SV向Verilog擴(kuò)展-一個(gè)單獨(dú)的標(biāo)準(zhǔn)

到2001年,典型數(shù)字集成電路的規(guī)模和復(fù)雜性從20世紀(jì)80年代開(kāi)始發(fā)生了巨大的變化,當(dāng)時(shí)Verilog和VHDL語(yǔ)言都是第一次出現(xiàn)。即使在Verilog-2001中增加了新功能,有效地建模這些大型設(shè)計(jì)以及驗(yàn)證這些復(fù)雜設(shè)計(jì)所需的大量激勵(lì)和反復(fù)檢查代碼也變得越來(lái)越困難,為了解決Verilog-2001的語(yǔ)言局限性,Accellera開(kāi)始為Verilog語(yǔ)言定義大量新功能。”這些擴(kuò)展被概括為兩個(gè)主要類(lèi)別:

增強(qiáng)功能主要滿(mǎn)足更高效、更準(zhǔn)確地建模數(shù)字邏輯功能的需要。

為大型復(fù)雜設(shè)計(jì)編寫(xiě)高效廣泛驗(yàn)證代碼的功能增強(qiáng)。

定義下一代Verilog的最初工作是在IEEE之外完成的,由一個(gè)名為Accellera(現(xiàn)為Accellera Systems Initiative)的獨(dú)立非營(yíng)利組織完成。Accellera是一個(gè)think-tank組織,由開(kāi)發(fā)電子設(shè)計(jì)自動(dòng)化(EDA)軟件工具的公司和使用這些軟件工具的公司的代表組成。Accelera成立于20世紀(jì)90年代中期,由Verilog和VHDL用戶(hù)組合并而成。后來(lái),其他EDA小組也并入了Accelera,如SystemC Initiative。Accelera負(fù)責(zé)目前使用的許多EDA工程標(biāo)準(zhǔn)的初始開(kāi)發(fā)工作。許多Accelera標(biāo)準(zhǔn)最終“成為IEEE標(biāo)準(zhǔn)”。

2002年末,Accellera發(fā)布了這些主要擴(kuò)展的第一個(gè)版本,該版本將添加到IEEE Verilog-2001語(yǔ)言中。在Verilog-2001擴(kuò)展的開(kāi)發(fā)過(guò)程中,這些新的語(yǔ)言功能被稱(chēng)為“Verilog++”,但在最后一刻決定將這些擴(kuò)展發(fā)布為“SystemVeriIog 3.0”。選擇使用是為了表明,當(dāng)擴(kuò)展與Verilog結(jié)合時(shí),它將是Verilog語(yǔ)言的第三代(Verilog-95是第一代,Verilog-2001是第二代),B Accellera繼續(xù)定義對(duì)Verilog的更多擴(kuò)展,一年后,在2003年發(fā)布了SystemVerilog 3.1標(biāo)準(zhǔn)。

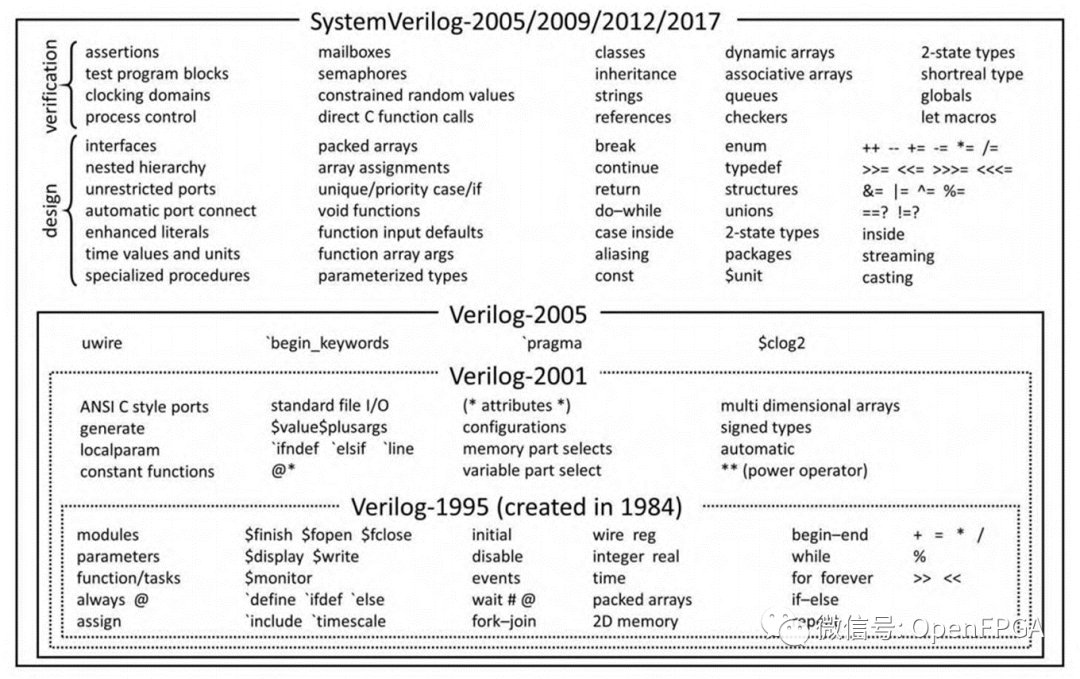

需要注意的是,Accellera SystemVerilog 3.1文檔不是一種完整的獨(dú)立語(yǔ)言,它是IEEE 1364-2001 Verilog語(yǔ)言的一組擴(kuò)展。Accellera最初的意圖是,IEEE隨后將這些擴(kuò)展添加到下一版本的IEEE 1364 Verilog標(biāo)準(zhǔn)中,目標(biāo)是1364-2005,昵稱(chēng)為Verilog-2005。然而,出于多種原因,IEEE Verilog標(biāo)準(zhǔn)委員會(huì)決定不立即將這些擴(kuò)展合并到實(shí)際的Verilog 1364標(biāo)準(zhǔn)中。相反,IEEE為這些擴(kuò)展指定了一個(gè)新的標(biāo)準(zhǔn)編號(hào),在2005年,IEEE發(fā)布了1364-2005 Verilog標(biāo)準(zhǔn),同時(shí)發(fā)布了1800-2005 SystemVerilog對(duì)Verilog標(biāo)準(zhǔn)的擴(kuò)展。

圖1-2顯示了SystemVerilog添加到Verilog-2001的主要功能。該圖還顯示,Verilog 1364-2005中包含了4項(xiàng)功能,而不是SystemVerilog 1800-2005標(biāo)準(zhǔn)。圖1-2沒(méi)有描述SystemVerilog的2005、、2009、 2012和2017版本之間的關(guān)系。SystemVerilog添加到傳統(tǒng)Verilog中的大多數(shù)新功能都是在SystemVerilog-2005版本中實(shí)現(xiàn)的。2009和2012版本中只添加了少量附加功能,2017版本中沒(méi)有添加任何新功能。

圖1-2:帶有SystemVerilog語(yǔ)言擴(kuò)展的Verilog-2005

SystemVerilog取代Verilog

在發(fā)布這兩個(gè)獨(dú)立的標(biāo)準(zhǔn)后,IEEE立即開(kāi)始將這兩個(gè)標(biāo)準(zhǔn)合并在一起,合并了這兩個(gè)大型文檔。除了合并這兩個(gè)標(biāo)準(zhǔn)外,IEEE還定義了許多附加SystemVeriIog功能(西蒙·戴維曼(Simon Davidmann)是數(shù)字仿真領(lǐng)域的早期先驅(qū)之一,他就Verilog和SystemVerilog的起源寫(xiě)了一本更詳細(xì)的歷史書(shū),可以在《System Verilogfor Design,Second Edition》一書(shū)的附錄中找到。)。合并后的Verilog和SystemVerilog標(biāo)準(zhǔn)作為IEEE 1800-2009 SystemVerilog標(biāo)準(zhǔn)發(fā)布。當(dāng)時(shí),IEEE終止了舊的Verilog-1364標(biāo)準(zhǔn)。“Verilog”的名稱(chēng)正式成為“SystemVerilog”。

硬件設(shè)計(jì)和驗(yàn)證這些設(shè)計(jì)的復(fù)雜性在不斷發(fā)展,IEEE也在不斷發(fā)展SystemVerilog標(biāo)準(zhǔn)以跟上步伐。2012年,IEEE發(fā)布了1800-2012 SystemVerilog標(biāo)準(zhǔn)。SystemVerilog-2017版本主要對(duì)SystemVerilog標(biāo)準(zhǔn)進(jìn)行了修正,并未在2012標(biāo)準(zhǔn)中添加任何新的語(yǔ)言功能。

IEEE在2005年決定發(fā)布兩個(gè)獨(dú)立的標(biāo)準(zhǔn)——一個(gè)包含傳統(tǒng)的Verilog語(yǔ)言(1364-2005),另一個(gè)只包含Verilog的擴(kuò)展,稱(chēng)為SystemVerilog(1800-2005)——這讓工程師們感到困惑。一個(gè)普遍存在的誤解是Verilog是一種硬件建模語(yǔ)言,SystemVerilog是一種驗(yàn)證語(yǔ)言。這種理解是不對(duì)的!最初的Verilog語(yǔ)言始終是一種集成的建模和驗(yàn)證語(yǔ)言。SystemVerilog以實(shí)質(zhì)性的方式擴(kuò)展了原始Verilog HDL的建模方面和驗(yàn)證方面。SystemVerilog既是一種數(shù)字建模語(yǔ)言,也是一種數(shù)字驗(yàn)證語(yǔ)言。

審核編輯:劉清

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26605 -

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83917 -

HDL語(yǔ)言

+關(guān)注

關(guān)注

0文章

47瀏覽量

8949

原文標(biāo)題:談?wù)刅erilog和SystemVerilog簡(jiǎn)史,F(xiàn)PGA設(shè)計(jì)是否需要學(xué)習(xí)SystemVerilog

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)是否需要學(xué)習(xí)SystemVerilog

FPGA設(shè)計(jì)是否需要學(xué)習(xí)SystemVerilog

評(píng)論