中斷

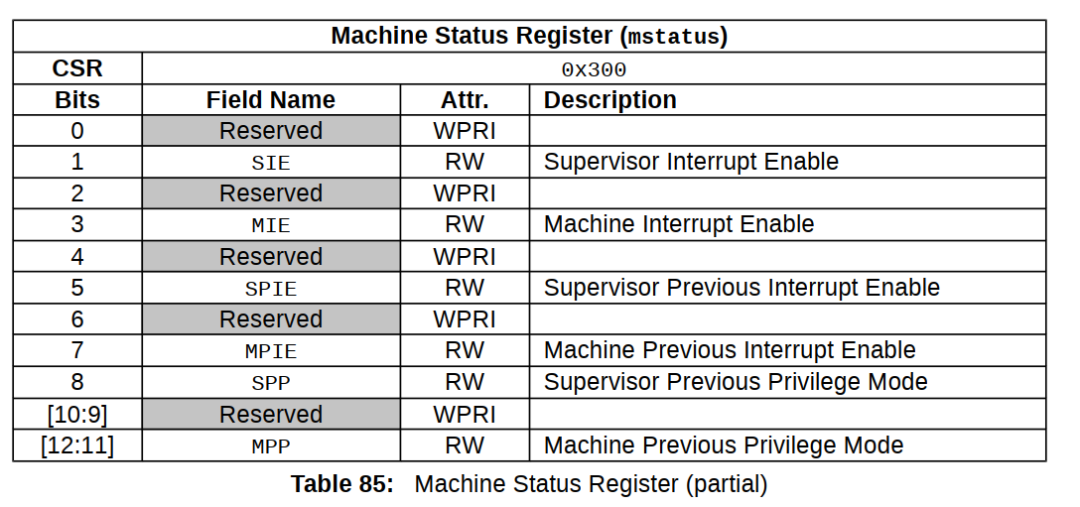

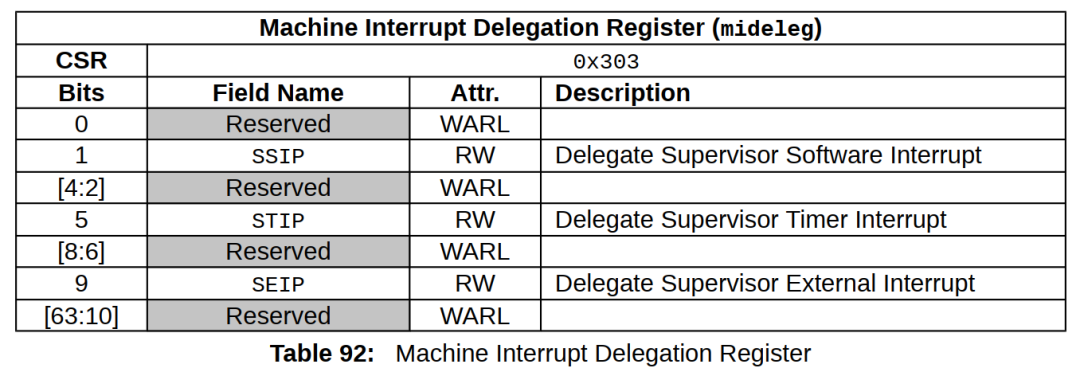

U54內核支持M模式和S模式中斷。默認情況下,所有中斷都在M模式下處理。對于支持S模式的 hart,可以有選擇地將中斷委托給S模式。

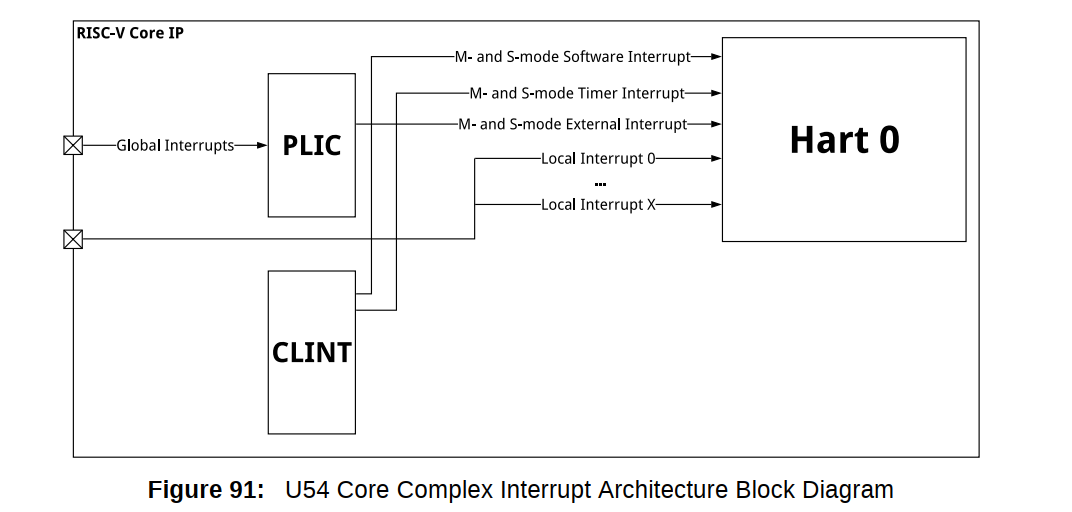

U54中斷架構如下:

U54內核還支持兩種類型的 RISC-V 中斷:本地和全局。

本地中斷:U54內核的本地中斷只有2種,軟件中斷和定時器中斷,這兩個中斷都由本地中斷器(CLINT)生成。本地中斷通過專用中斷異常代碼和固定優先級直接發送給單個hart。因此,本地中斷沒有仲裁,也不需要額外的內存訪問來確定中斷的原因。

全局中斷:通過平臺級中斷控制器 (PLIC) 路由,該控制器可以通過外部中斷將中斷定向到系統中的任何 hart。所有的外設都屬于全局中斷。

中斷優先級

全局中斷的各個優先級由 PLIC 確定。

U54內核的優先級如下,按優先級降序排列:

機器外部中斷

機器軟件中斷

機器定時器中斷

主管外部中斷

主管軟件中斷

主管定時器中斷

異常

如果一個 hart 在S模式下運行并嘗試訪問一個僅M模式的控制和狀態寄存器 (CSR),這會立即進入異常處理程序并確定下一步行動。mstatus寄存器中的異常代碼將保持值 0x2,表明發生了非法指令異常。根據系統的要求,監督模式應用程序可能會報告錯誤和/或完全終止程序。

沒有特定的啟用位來允許發生異常,因為默認情況下它們總是啟用的。然而,在引導流程的早期,軟件應該將 mtvec.BASE設置為一個定義的值,其中包含默認異常處理程序的基地址。所有異常都會捕獲 tomtvec.BASE。軟件必須讀取 mcause CSR以確定異常的來源,并采取適當的措施。

在中斷處理程序中發生的同步異常將立即導致程序執行中止中斷處理程序并進入異常處理程序。中斷處理程序中的異常通常是軟件錯誤的結果,通常應該避免,因為mepc 和 mcause CSR 將被原始中斷上下文中捕獲的值覆蓋。

RISC-V 定義的同步異常具有優先級順序,當單個指令同時發生多個異常時,可能需要考慮優先級順序。下表描述了同步異常優先級順序。

數據地址斷點(watchpoints)、指令地址斷點、環境斷點異常(EBREAK)都具有相同的異常碼(3),但優先級不同,如上表所示。

指令地址未對齊異常 (0x0) 的優先級低于其他指令地址異常,因為它們是目標未對齊的控制流指令的結果,而不是取指的結果。

-

內核

+關注

關注

3文章

1382瀏覽量

40375 -

RISC

+關注

關注

6文章

465瀏覽量

83813 -

架構

+關注

關注

1文章

519瀏覽量

25515 -

sifive

+關注

關注

0文章

36瀏覽量

9467

發布評論請先 登錄

相關推薦

三星將SiFive RISC-V內核用于SoC,汽車,5G應用

SiFive發布P870和X390,RISC-V架構內核性能暴漲

全球首款基于 RISC-V “HiFive Unleashed” 單板計算機(SBC)

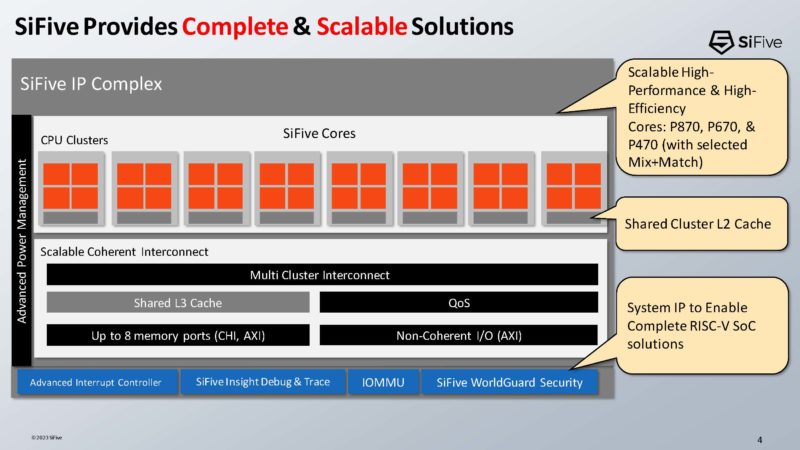

可擴展的高性能RISC-V 內核IP

帶有SiFive開發板和高性能CPU的RISC-V邁向主流

RISC-V是什么?有哪些優勢

SiFive及晶心科技共同推展RISC-V_擴大RISC-V市占率

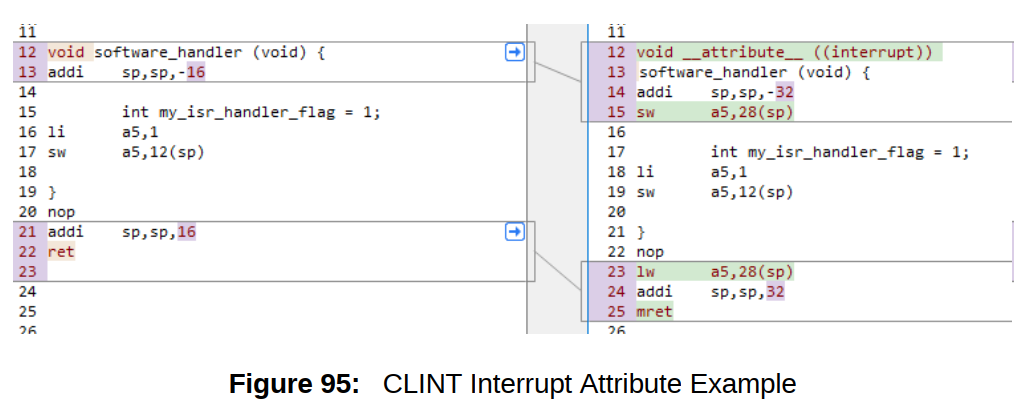

Sifive Learn Inventor基礎之GPIO 按鍵中斷 RISC-V

SiFive P870 RISC-V 處理器亮相 Hot Chips 2023

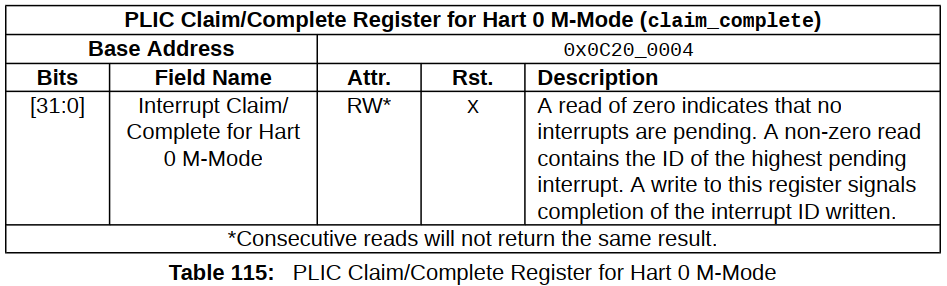

U54內核PLIC中斷處理例子

U54內核上CLINT的內存映射

U54內核中斷控制和狀態寄存器

RISC-V發展及FPGA廠商為什么選擇RISC-V

RISC-V SiFive U54內核的中斷介紹

RISC-V SiFive U54內核的中斷介紹

評論