在systemverilog協(xié)議中,logic定義四態(tài)值,即向量(vector)的每個(gè)位(bit)可以是邏輯0, 1, Z或X,與verilog協(xié)議中的reg很接近。但是logic有個(gè)很明顯的優(yōu)勢(shì),不允許多驅(qū)動(dòng)。

多驅(qū)動(dòng)對(duì)關(guān)鍵字logic而言是語(yǔ)法錯(cuò)誤,在VCS編譯階段就能夠發(fā)現(xiàn),能夠更早得發(fā)現(xiàn)錯(cuò)誤。

而在Verilog協(xié)議中,并沒(méi)有強(qiáng)調(diào)reg是不允許多驅(qū)的,因此VCS等編譯工具不會(huì)主動(dòng)報(bào)錯(cuò)。

需要在spyglass lint才能檢查出來(lái),或者通過(guò)VCS 仿真發(fā)現(xiàn)。

在芯片設(shè)計(jì)中,更早的暴露問(wèn)題一直是設(shè)計(jì)和驗(yàn)證人員追求的目標(biāo),因此在RTL編碼時(shí),如果正常設(shè)計(jì)是不允許多驅(qū)動(dòng)的場(chǎng)景中,建議使用logic替代reg。

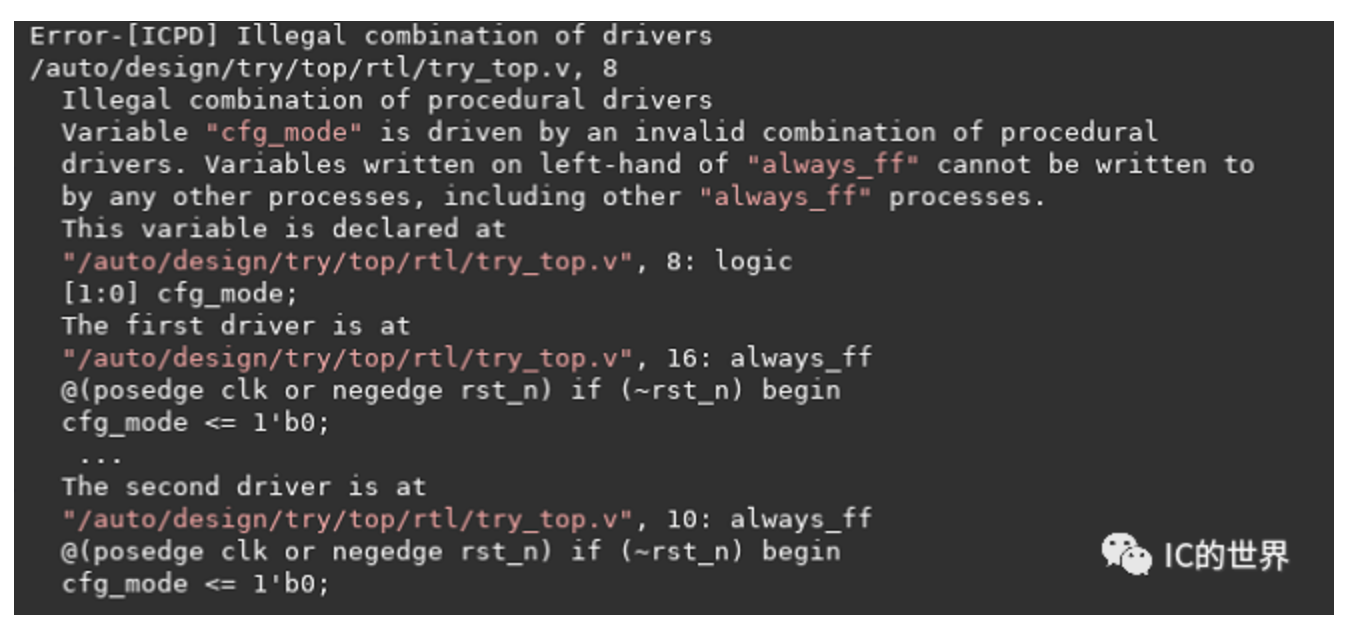

如下案例中:cfg_mode 被多驅(qū)動(dòng),在實(shí)際項(xiàng)目設(shè)計(jì)中,多驅(qū)動(dòng)的問(wèn)題往往更加隱蔽,更不容易發(fā)現(xiàn)。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

logic [1:0] cfg_mode ;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

VCS報(bào)錯(cuò):

如下案例中:cfg_mode 被多驅(qū)動(dòng),但是申明成reg類(lèi)型,因此VCS不會(huì)報(bào)ERROR。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

reg [1:0] cfg_mode ;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

53文章

8271瀏覽量

146840 -

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83883 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59911 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9630 -

Verilog語(yǔ)言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8288

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SystemVerilog學(xué)習(xí)一 —— 計(jì)數(shù)器

[啟芯公開(kāi)課] SystemVerilog for Verification

是否有更好的方法來(lái)存儲(chǔ)比reg [100,000:0] val更有效的大值

使用SystemVerilog來(lái)簡(jiǎn)化FPGA中接口的連接方式

噪聲頻譜密度(NSD)比信噪比(SNR)更有用?

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊(cè)

SystemVerilog 3.1a Language Re

SystemVerilog的正式驗(yàn)證和混合驗(yàn)證

數(shù)字硬件建模SystemVerilog之Interface方法概述

SystemVerilog在硬件設(shè)計(jì)部分有哪些優(yōu)勢(shì)

systemverilog:logic比reg更有優(yōu)勢(shì)

SystemVerilog相比于Verilog的優(yōu)勢(shì)

systemverilog:logic比reg更有優(yōu)勢(shì)?

systemverilog:logic比reg更有優(yōu)勢(shì)?

評(píng)論