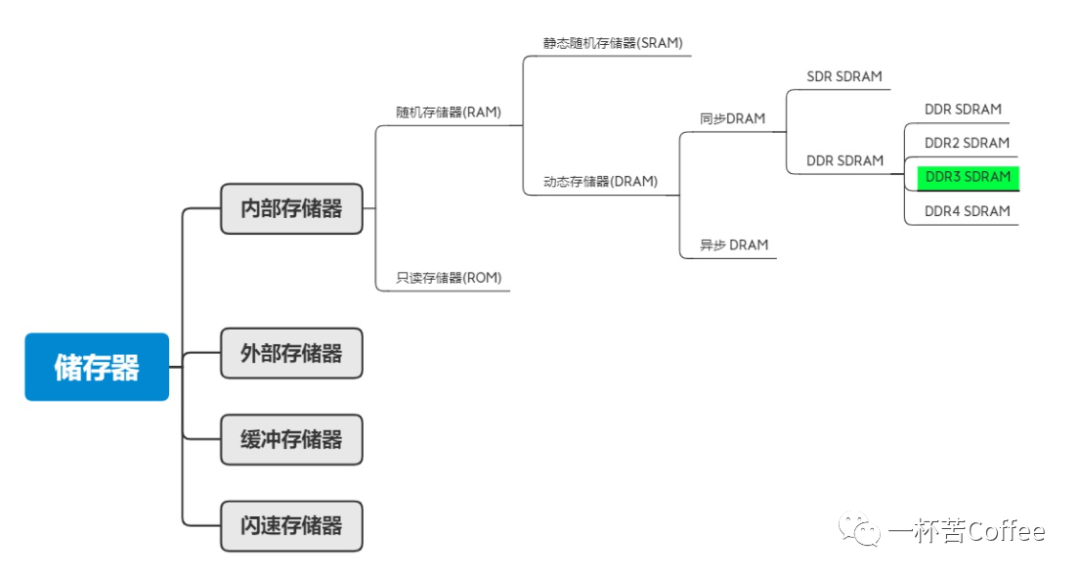

SDRAM簡介

SDRAM(synchronous dynamic random-access memory)即同步動態隨機存取內存。在介紹SDRAM前,我們先了解下DRAM(Dynamic random-access memory),DRAR中文譯為動態隨機存取內存,也叫動態隨機存取器,為什么叫動態隨機存取器,原因是它的實現原理跟靜態存儲器SRAM不一樣,DRAM是在芯片里集成很多個陣列的電容,DRAM存儲二進制數據0和1就是通過給這些陣充放電荷實現。一個簡單的單個DRAM存儲單元示例圖如下圖所示。

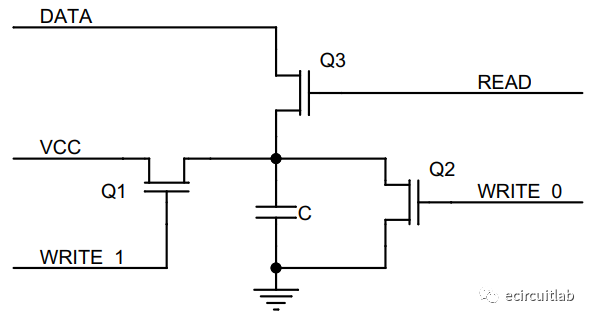

單個DRAM單元實現電容充放電原理

電容C用來存儲電荷,信號WRITE 1、WRITE 0控制開關晶體管Q1和Q2給電容充電和放電,實現二進制1和0存儲。信號READ控制開關晶體管打開把電容C接到數據線DATA上,芯片內部處理電路通過讀取DATA線上的電壓信號來判斷DRAM存儲單元存儲的數據為二進制1還是0。

從原理上去看DRAM實現數據存取很完美,但實際芯片按照上面的原理做好電路后,開關晶體管和電容本身都會有漏電流。漏電流會導致一個特別糟糕的情況,電容存儲的電荷會慢慢通過漏電流方式流失掉,當電荷流失到一定的量后,內部電路讀取電容的電壓去判斷數據時,就不能正確判斷為二進制1了,這種情況下數據是錯誤。

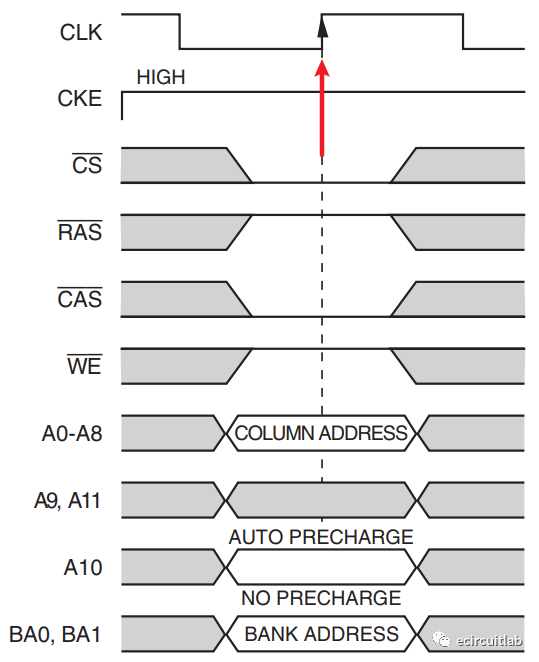

這樣的錯誤肯定是不允許發生的,解決辦法是通過定時刷新方式給電容充電,保證電容存儲的電荷量穩定在理想的狀態。因為這樣的過程是一個一直的動態過程,動態隨機存取器的名稱由此而來。而SDRAM是DRAM的一種操作方式,如下圖所示,SDRAM讀寫數據時,是通過在時鐘的上升沿同步獲取控制、數據信號,所以叫做同步動態隨機存取器。

SDRAM在時鐘CLK上升沿時同步獲取控制、數據信號

DRAM和SRAM優缺點:

- SRAM讀寫速度快,DRAM讀寫速度慢。

- SRAM耗電量低,DRAM耗電量大。

- SRAM制造成本高,容量低,DRAM制造成本低,容量大。

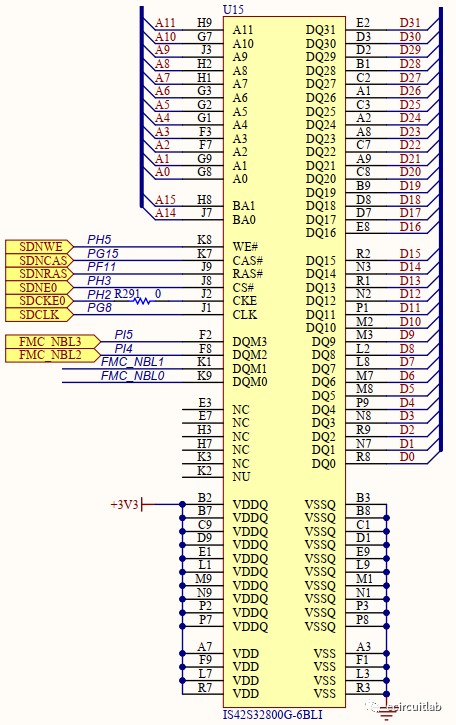

SDRAM接口信號

SDRAM主要信號如下(256Mb容量示例):

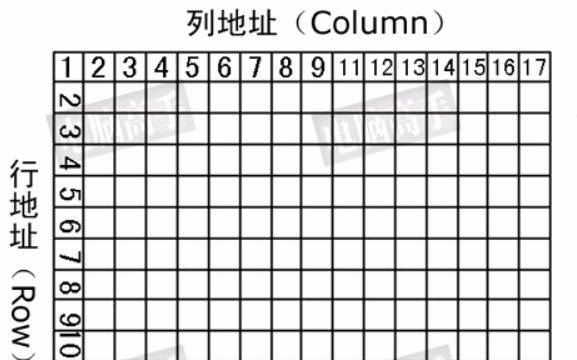

A0-A11: 地址信號。

BA0-BA1: Bank選擇信號。

DQM0-DQM3: 讀寫數據掩碼控制信號。

DQ0-DQ31: 數據信號。

CKE: 時鐘使能信號。

CLK: 時鐘信號。

CS: 片選信號。

CAS: 列地址選通控制信號。

RAS: 行地址選通控制信號。

WE: 寫使能信號。

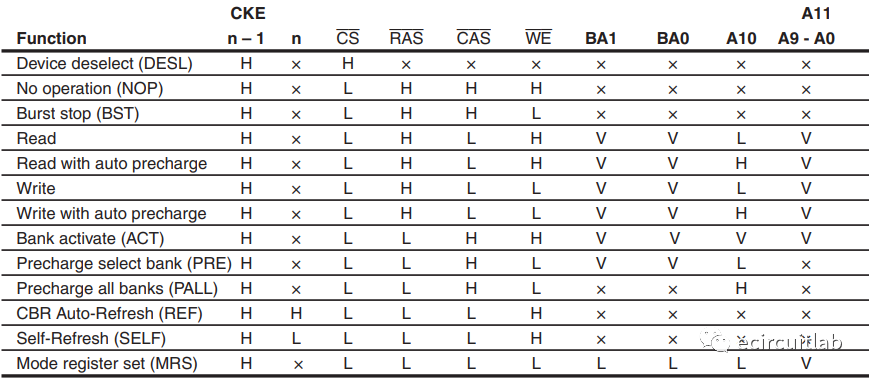

在上述羅列的信號中,A0-A11、BA0-BA1、CKE、CS、CAS、RAS、WE的不同組合,可以構成不同的Command如下圖所示。

DRAM Commad真值表

從上圖可以看到,DQ0-DQ31和DQM0-DQM3不參與組合成Command。這里說明下,DQMx是讀寫數據掩碼信號,用于控制數據讀寫使能對應Byte的。它們的控制關系是DQM0控制DQ0-DQ7,DQM1控制DQ8-DQ15,以此類推。知道數據信號DQ0-DQ31不參與組合成Command后,在硬件設計的Layout階段時,有時數據線不好走線,可以通過調換組內數據線來解決數據線Layout難度大問題。

注意這里說的組內調換是單個Byte內的信號,DQ0-DQ7為一組,DQ8-DQ15為一組,以此類推,不能跨組調換,跨組調換讀寫數據就錯誤了。

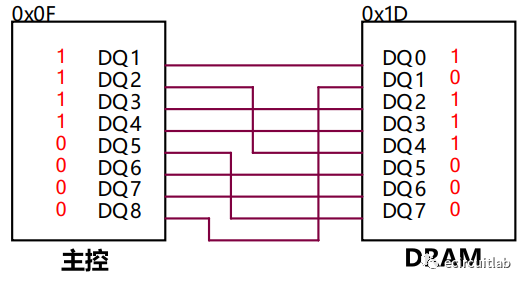

這里介紹的組內數據線調換不影響數據的正確性,可能會有很多人困惑,我做了個圖如下說明解釋。如下圖中,左側為主控信號,右側為DRAM。主控要寫數據0x0F到DRAM中,因為數據線在DRAM端被調換了,所以實際到DRAM內的數據變為0x1D。這樣看像是數據錯了,但我們再看主控從DRAM讀數據的情況,主控讀數據時,DRAM內的0x1D順著信號線原路返回,變成了0x0F,錯錯得正。

所以DRAM信號線組內調線序不影響數據讀寫錯誤,但不能跨組調,不能跨組調的原因是即使有錯錯得正的邏輯,但是如果DQM信號沒有使能對應的Byte,那就會導致數據缺失,所以必然出錯。

在DRAM端做數據組內調換,不影響主控讀寫數據的正確性

當然,組內數據可調的這個思路,放在DDR3、DDR4等都可以的,但還是要先看DRAM規格書,確定數據線不參與任何Command組合,如果參與了就不能調,比如有的廠家的LPDDR就用了數據線來做Command。

STM32上的SDRAM電路設計

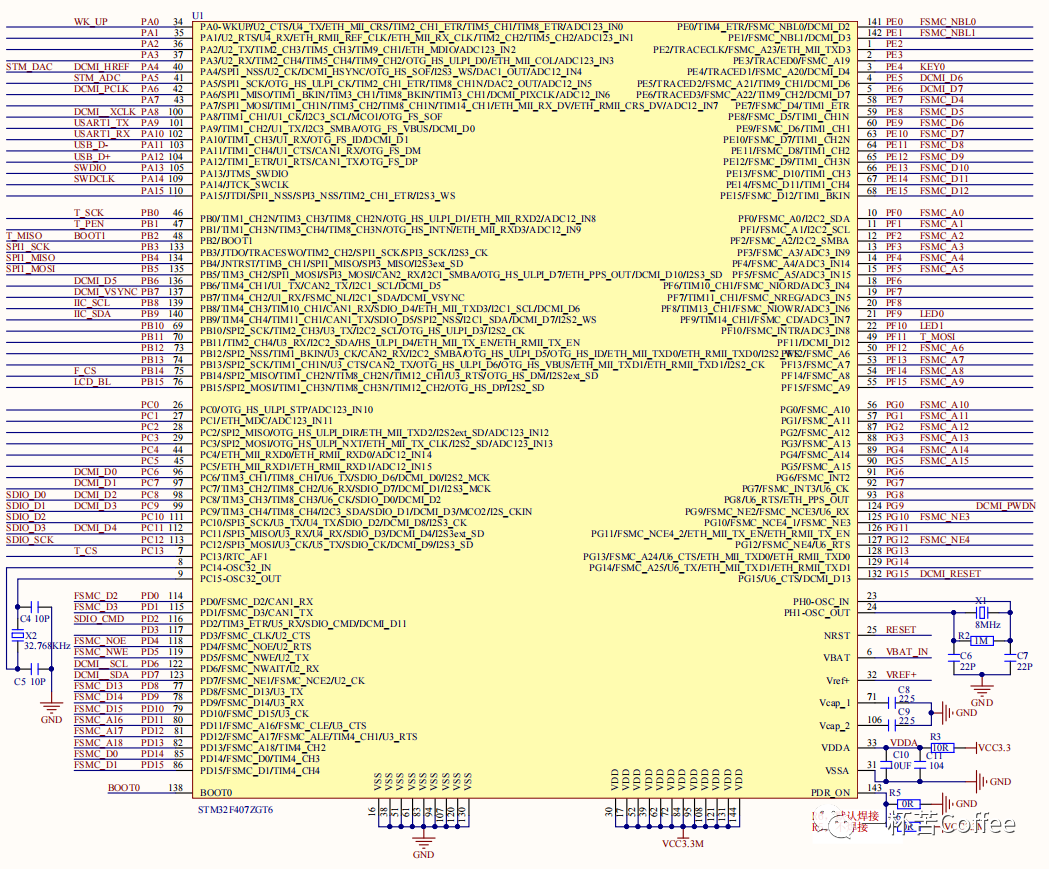

參考ST評估板MB1219的SDRAM部分電路如下,STM32使用SDRAM的目的是擴充芯片內存,由FMC接口控制,電路沒什么復雜的,設計時注意了解各個信號的作用,然后參考規格書把信號一一對應連接上即可。

評估板MB1219使用的主控是STM32F769NI,參考STM32F7xx規格書第86頁的Table 12. FMC pin definition的SDRAM欄,有詳細的信號定義。下圖中的BA0和BA1接的信號為A14和A15,這里沒有錯,是ST工程師在設計評估板時,FMC總線上還掛了SRAM和Nor Flash,而A14和A15是SRAM和Nor Flash的,但對應SDRAM實際為BA0和BA1。

SDRAM參考設計電路

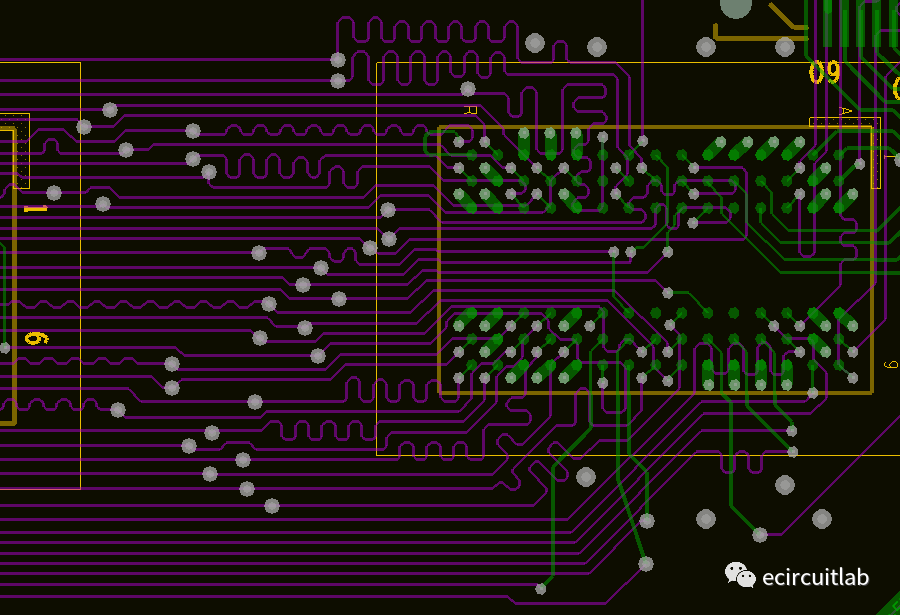

完成原理圖設計,后面剩下的是大家比較關心的Layout要不要做信號線等長的問題,這個問題在網上一直是很多人熱衷討論的一個問題,各有說法。其實對于SDRAM,只要走線不會長度差得特別離譜,比如差不多十幾個厘米這樣的,不等長影響不會很大,但如果PCB空間資源足夠的話建議按照500mil的規則做等長。如下圖ST的評估板MB1219就做了等長。

條件允許,推薦SDRAM做500mil約束等長

-

STM32

+關注

關注

2271文章

10923瀏覽量

357108 -

PCB設計

+關注

關注

394文章

4697瀏覽量

86129 -

靜態存儲器

+關注

關注

0文章

10瀏覽量

7539 -

SDRAM控制器

+關注

關注

0文章

28瀏覽量

8179 -

電容充放電

+關注

關注

0文章

94瀏覽量

5861

發布評論請先 登錄

相關推薦

SDRAM連接電路設計詳解

怎么成為硬件電路設計高手?

硬件電路設計之STM32最小系統電路設計

STM32F103在電路板上怎樣做配套的電路設計呢?

高速SDRAM存儲器接口電路設計

關于SDRAM電路的設計

STM32CubeMX | 31-使用硬件FMC讀寫SDRAM(W9825G6KH)

STM32上的SDRAM硬件電路設計

STM32上的SDRAM硬件電路設計

評論