一看到DDR,聯想到的就是高速,一涉及到高速板有些人就比較茫然。高速板主要考慮兩個問題點,當然其它3W,2H是基本點。

一是時序,因為有的DDR要跑幾百M,所以對應的時鐘周期比較短,如果傳輸線的長度相差較多,會導致數據先到,有的數據后到,數據就不完整。

二是,阻抗,高速信號頻率高,波長短,在微波領域是短線傳輸。如果阻抗不匹配就會產生反射,反射回來的信號與原信號疊加,就改變了原來信號的形狀。電磁場與微波相關書籍講得比較多,涉及到二階偏微分方程,這里只說結論,我們拿來用就可以了。

總結一下,就兩點:

1、等長

2、阻抗要匹配

這兩點也是我們做PCBLAYOUT設計時注意的重點,由此也前人也總結出一些相關原則。比如信號分組,同層同組,3W間距等等。

下面我們以DDR3為例,把原理搞清楚,然后根據原理說說實際LAYOUT時要怎么操作。

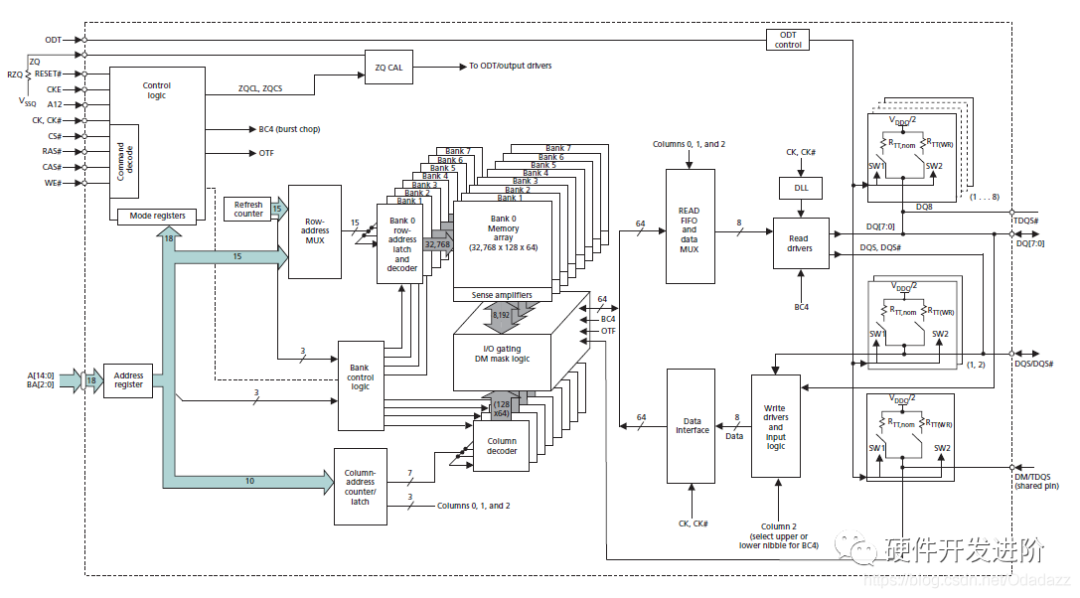

CPU對DDR的訪問,也就是讀和寫的操作,不管是讀還是寫,你得知道從哪里讀,往哪里寫吧?所以得知道地址,這個操作叫做尋址。

我覺得我還不能把DDR的原理講得很清楚,先放下來,好像也不影響我們做DDR的應用設計。

單片DDR3的引腳說明:

我們大概了解了DDR的原理后,就明白,地址線和控制線可以放一組,數據線另外放一組,但因為考慮到設計方面的問題,數據線可以按一個字節進行分組,比如8位放一組,D0-7作為一組,也可以16位放一組,D0-15.一般這兩種用得比較多。

以DDR3為例:

數據線1:11根,D0-D7,LDQM(數據掩碼),LDQS0.LDQSN0(其中,LDQS0和LDQSN0為差分時鐘)

數據線2:11根,D8-D23,UDQM(數據掩碼),UDQS0.UDQSN0(其中,UDQS0和UDQSN0為差分時鐘)

地址線、控制線和時鐘為一組:

A0-A15,BA0-BA2,

CKE,CLK-CLKN ,

CASN,CSN0,xRASN,RESET,WEN,ODT

說明:TI的文檔是把地址和數據的時鐘放在一組的,但是等長時,地址線與地址的時鐘等長,數據線與數據的時鐘等長。我這里是把數據和地址的時鐘分別放到了數線線和地址線組。

因此次只是單片DDR,不涉及拓撲結構。

此次設計并沒有同層同組,而是把數據線放在第一層和第三層,主要做了等長

同層同組的目的主要是為了等長:信號不在不同的層傳輸速度不一樣,另外在不同的層,因為有的有過孔,有的可能沒有過孔,過孔的長度和厚板以及過孔穿到哪一層有關,所以過孔的長度也會影響信號的長度,這次是放在第一層和第三層,第一層和第三層中間的PP一般比較薄,如下圖,只有3.2mil,所以影響長度有限。另外因為層不一樣導致的傳輸速度不一樣,只要把等長誤差做到10mil以內就不用考慮了。

| 層名 | 介質 | 厚度(mil/OZ) |

|---|---|---|

| L1 | Copper | 1.4mil/成品銅厚1oz |

| PP | FR4 | 3.2mil |

| L2 | Copper | 1.2mil/1.0oz |

| CORE | 5mil | |

| L3 | Copper | 1.2mil/1.0oz |

| PP | 37.3mil | |

| L4 | Copper | 1.2mil/1.0oz |

| CORE | 5mil | |

| L5 | Copper | 1.2mil/1.0oz |

| PP | 3.2mil | |

| L6 | Copper | 1.4mil/成品銅厚1oz |

總結:

平時都要求DDR走線同層同組,根本原因是等長。

同層的原因:信號在內層和外層傳輸速度不一樣,所以要盡層同層。

同組的原因:是為了設計好設計規則。方便看規則。只要能檢查到,不同組也是可以的。

下方D8-D15,有的是走在第一層,有的是走在第三層,實測沒有問題!

-

DDR3

+關注

關注

2文章

276瀏覽量

42357 -

cpu

+關注

關注

68文章

10901瀏覽量

212687 -

DDR

+關注

關注

11文章

715瀏覽量

65459 -

高速信號

+關注

關注

1文章

231瀏覽量

17730

發布評論請先 登錄

相關推薦

ddr4和ddr3內存的區別,可以通用嗎

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

基于Digilent介紹DDR3和mig

DDR3內存或退出市場三星等大廠計劃停產DDR3內存

Virtex7上DDR3的測試例程

FPGA學習-DDR3

基于AXI總線的DDR3讀寫測試

DDR3的原理和應用設計

DDR3的原理和應用設計

評論