如果你還在用“笨方法”一個節點一個節點地檢查電路中是否有floating的gate,那么你真的該仔細閱讀一下這次的內容,并嘗試在項目中使用文中介紹的方法進行floating gate檢查。

ADE Assembler介紹

ADE Assembler是一個交互式的、能同時進行多個仿真的集成環境,旨在將設計的所有部分結合在一起,以開始圍繞制造的設計。

在這種環境中,用戶可以合并設計的多個模塊測試,包括變量、器件參數、工藝角、檢查和斷言以及它們的規范等,每個測試都可以有獨立的設置內容。

ADE Assembler簡單理解可以認為是ADE XL的一個升級版本,自然包含不少新功能,其中一項:circuit checks便是接下來要使用的功能。

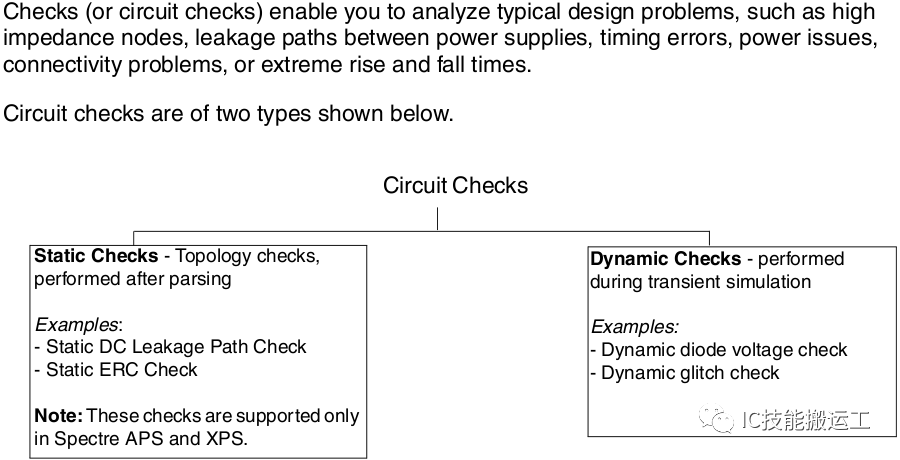

circuit check分成動態檢查(dynamic check)和靜態檢查(static check)兩種,靜態檢查利用拓撲結構實現,不需要運行瞬態仿真,動態檢查需要運行瞬態仿真,接下來就需要利用動態檢查實現電路中floating gate的檢查。

為什么要檢查floating gate 為什么要大費周章檢查floating gate呢?原因很簡單,電路中存在floating gate會產生很多不確定性影響。 最常見的是高阻節點處floating gate導致電路下電后漏電,有很多人通過電路下電后漏電情況間接判斷電路中是否存在floating gate. 但是通過漏電間接檢查電路中是否存在floating gate并不十分可靠,因為有些比較隱蔽的、可能存在漏電風險的高阻節點處floating gate通過這種方法可能檢查不到,所以推薦使用下面介紹的方法。 使用ADE Assembler檢查floating gate

注意:ADE Assembler是IC617及其之后版本的Cadence IC套件才有的工具,所以使用前需要先確認一下工具是否需要升級。

檢查floating gate使用dynamic check,需要運行瞬態仿真,所以,檢查結果體現的是在瞬態仿真過程中電路存在的floating gate, 通常會檢查電路下電后是否存在floating gate,下面以此為例。

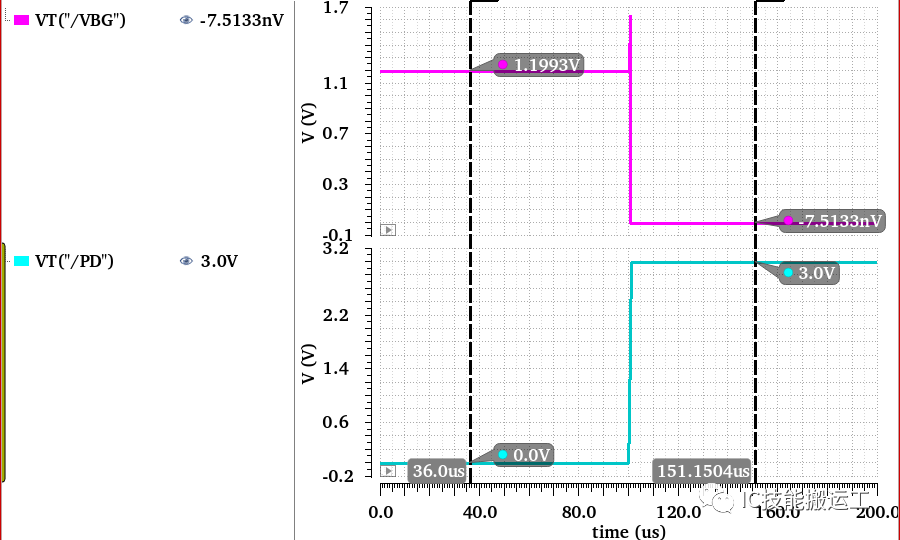

首先用ADE L仿真電路的下電過程,需要采用瞬態仿真,其它操作流程沒有特別需要注意的地方,確認仿真成功運行之后,保存ADE L的設置,留作在ADE Assembler中使用。

以上是仿真帶隙基準電路的下電過程,從仿真波形可以看出,電路正常工作一段時間之后被下電,包含了完整的工作過程和下電過程。

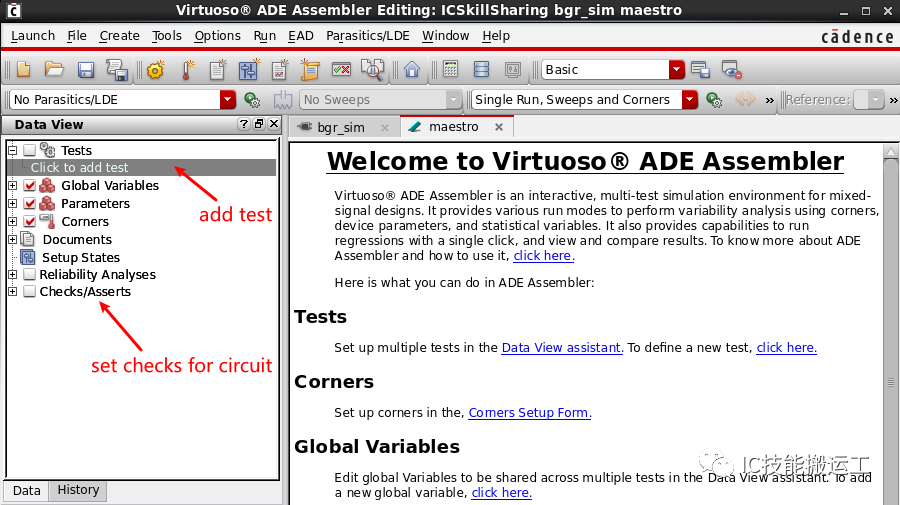

在原理圖編輯界面,選擇:Launch->ADE Assembler,根據實際情況選擇「Create」或者「Open」選項,然后一路確認,即可啟動ADE Assembler工具。

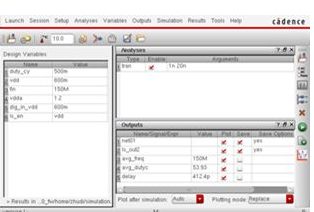

打開ADE Assembler界面如上圖所示,基本與ADE XL一致,IC617和IC618界面也很相近,略有不同,但是不影響使用。

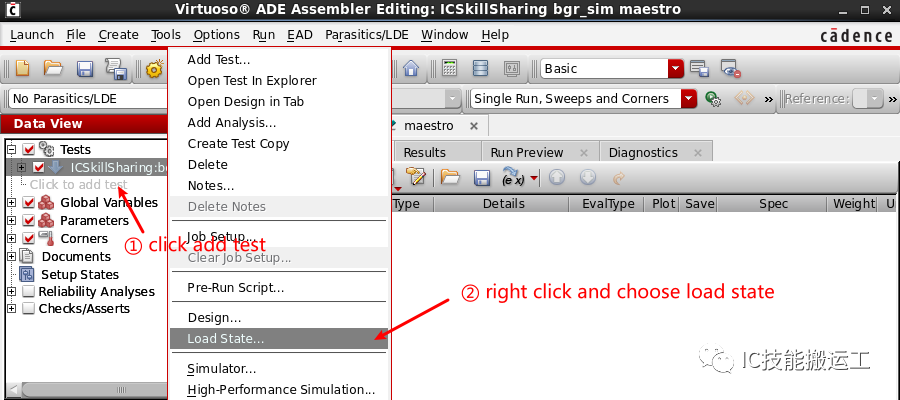

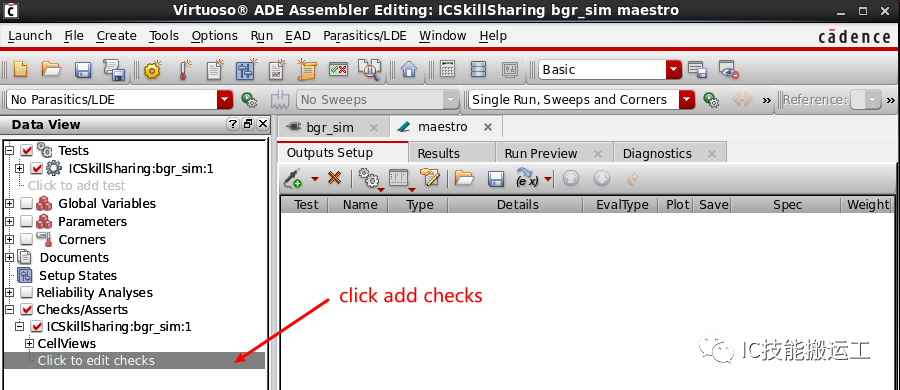

在左側Data View的最下面,有一個Checks/Asserts項目,這就是電路檢查項目,首先添加test設置,只需要load之前ADE L仿真保存的state即可。

接下來,勾選并展開Checks/Asserts選項,點擊「Click to edit checks」,開始設置電路檢查項目。

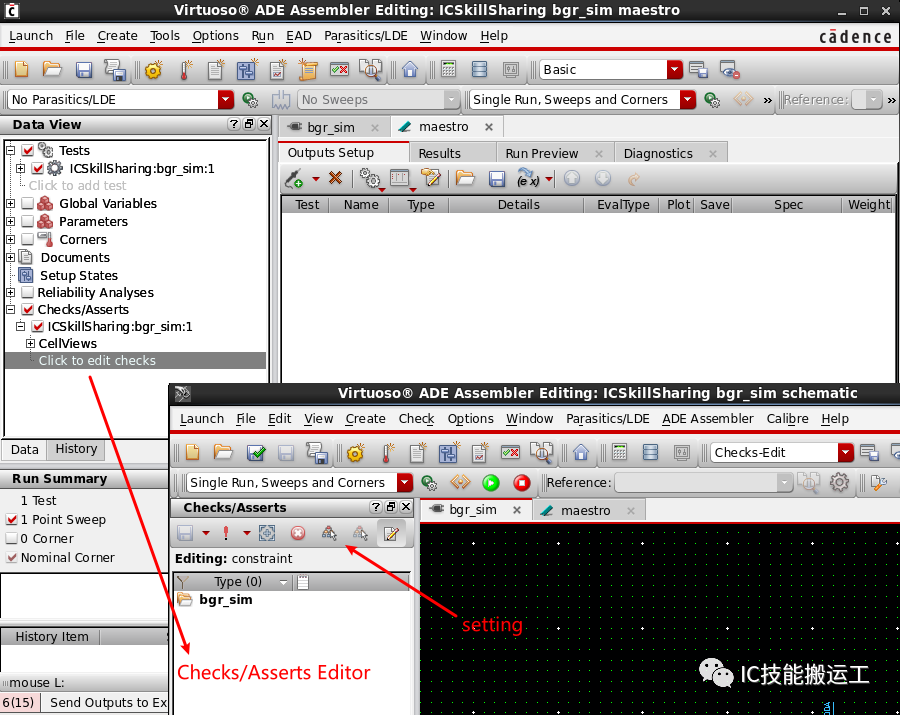

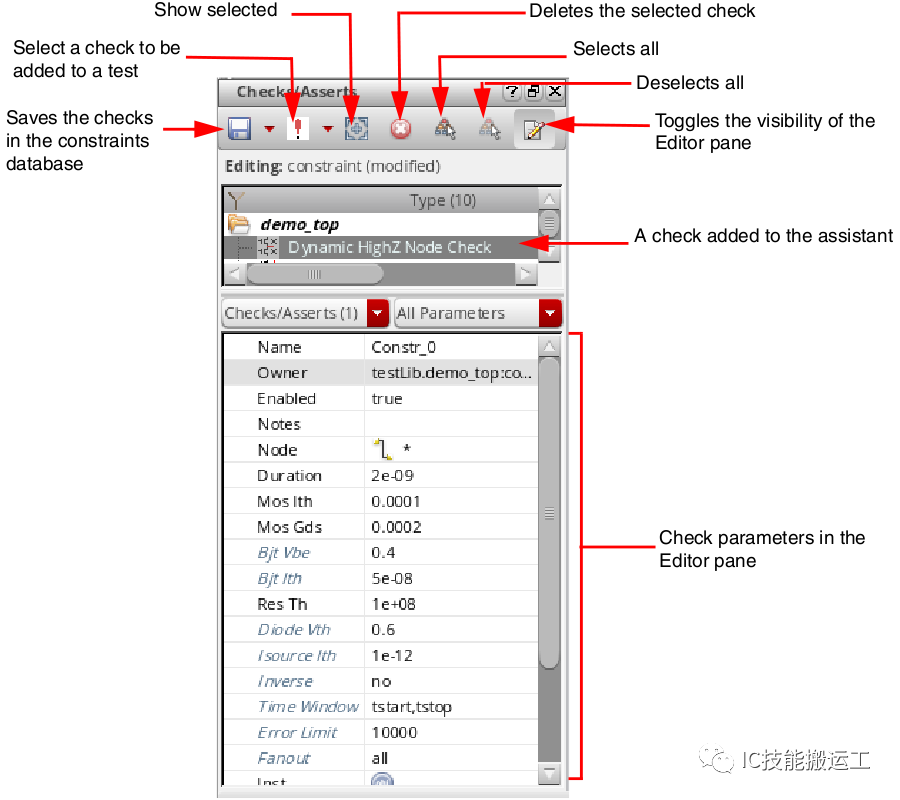

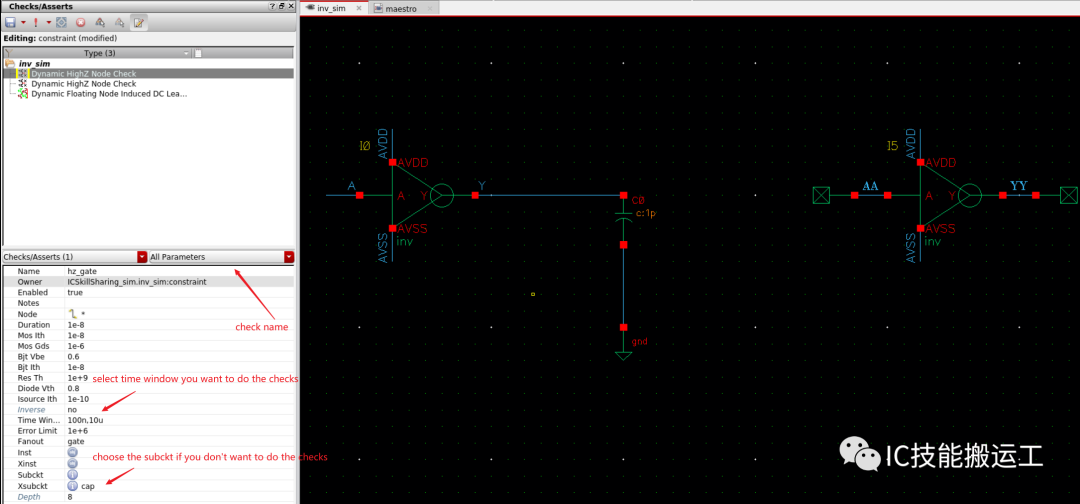

操作完成之后跳轉到另一個窗口,并自動打開Checks/Asserts Editor,下面簡單介紹一下該窗口的內容,部分截圖來自Cadence手冊。

上圖中「setting」所指的區域包含對Checks的一些操作,比如:保存、刪除、增加檢查等。

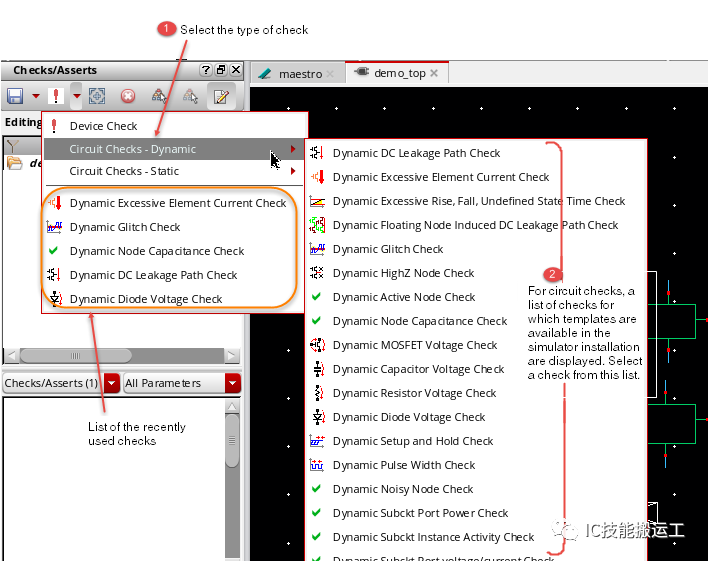

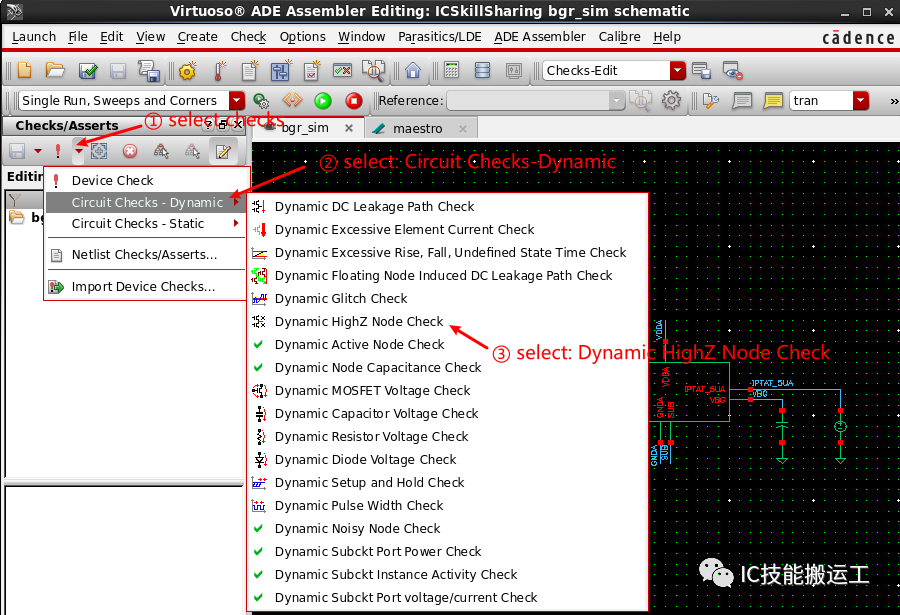

接下來點擊上圖中紅色感嘆號處的圖表,彈出如下面所示的對話框,包含各種檢查以及各種檢查對應的具體細節。

依次選擇:Circuit Checks-Dynamic->Dynamic HighZ Node Check,然后結束操作,可以看到左側會多出一些信息。

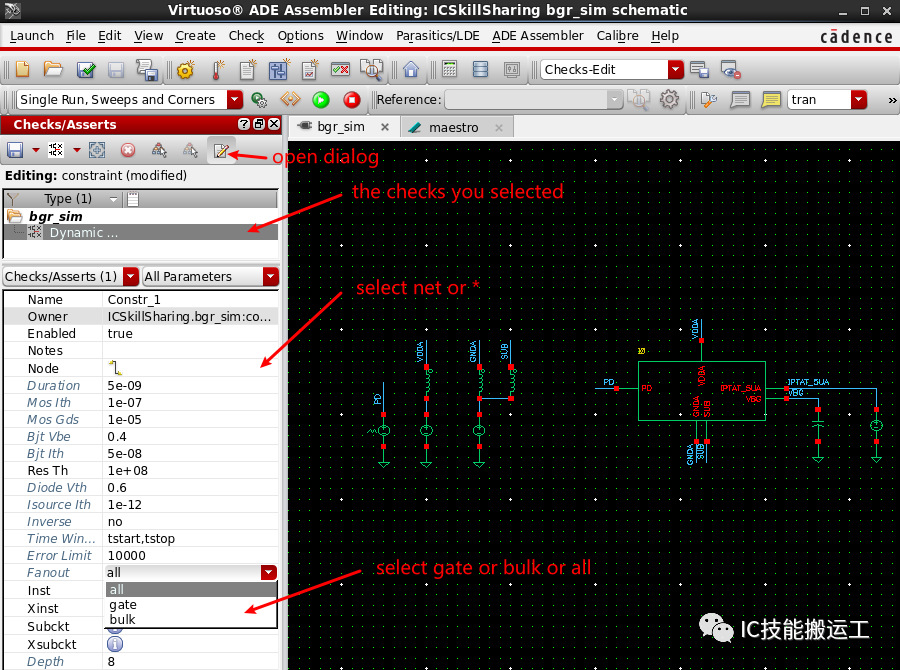

左側信息欄內按照下圖所示填寫內容即可,主要注意兩個地方,第一個是Node一欄,可以按照需要選擇檢查的信號,但是推薦檢查所有信號,在里面填入「*」.

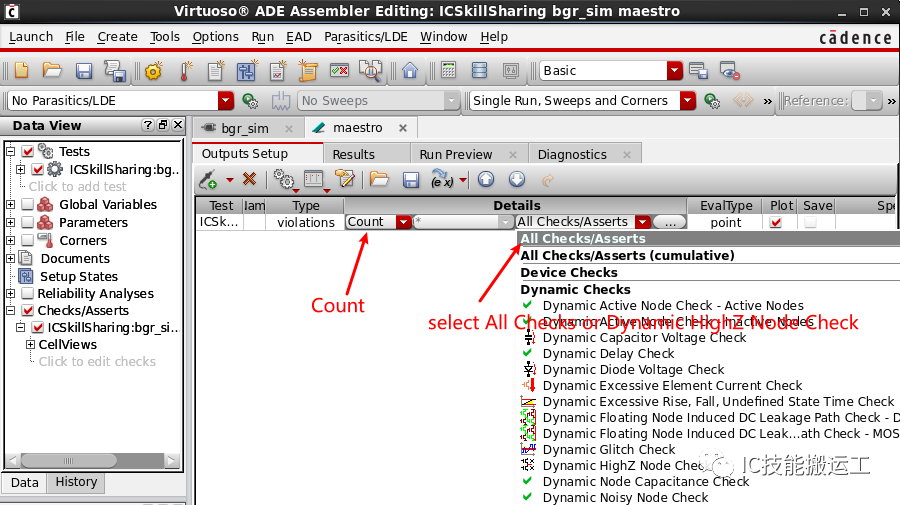

在Fanout一欄,根據檢查類型選擇gate或者bulk,即指定仿真器檢查floating gate或者floating bulk,如果沒有特別需要也可以選擇all,最后保存設置,并返回最初的ADE Assembler界面。 接下來進行輸出信息設置,在Output Setup界面,選擇:Add new output->your test name->Violation Filter,添加違例設置。

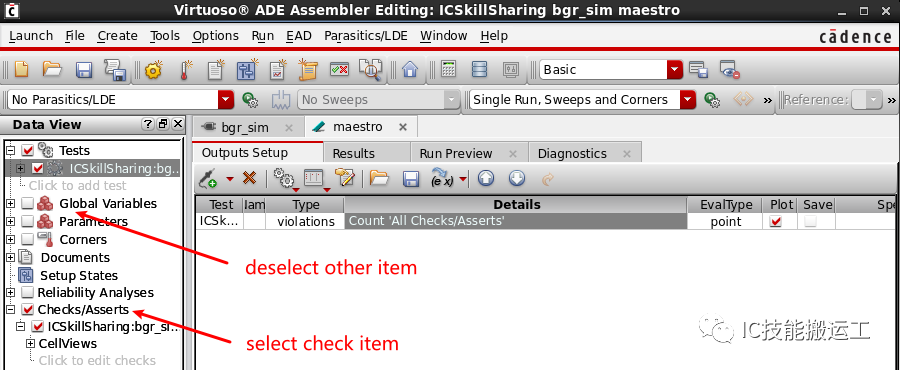

在Details一欄下面雙擊,會彈出三個可選框,具體內容有興趣的同學可以查看一下Cadence手冊,所有值保持默認即可,也可以根據具體檢測內容靈活選擇,小目同學的設置如上圖所示。 完成上面的設置之后,運行仿真,在運行仿真前記得勾選左側Checks/Asserts選擇框,并將不必要的項目取消選擇。

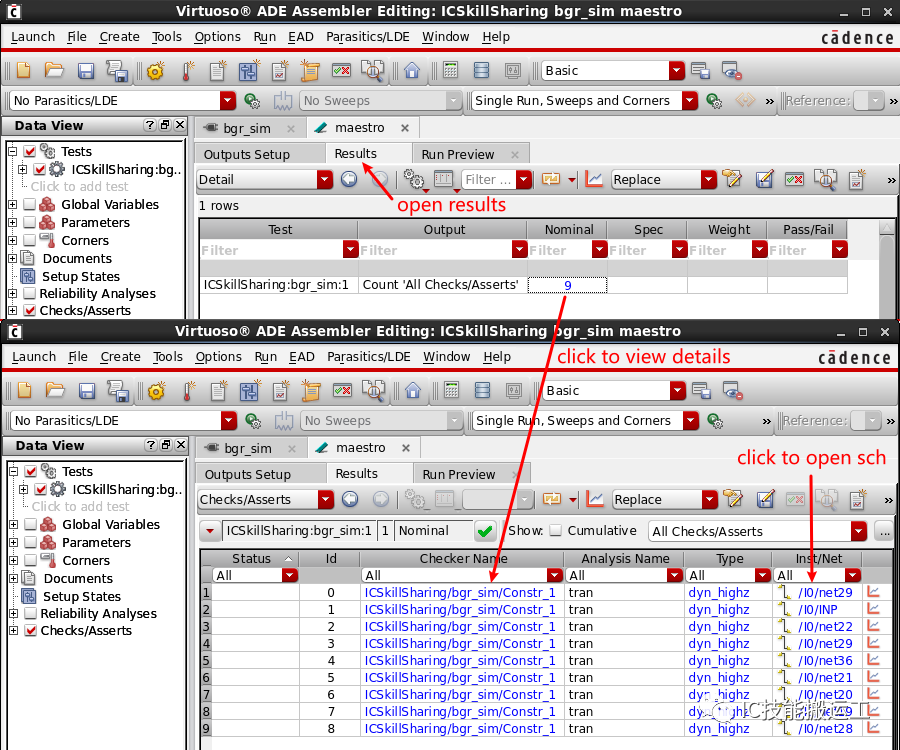

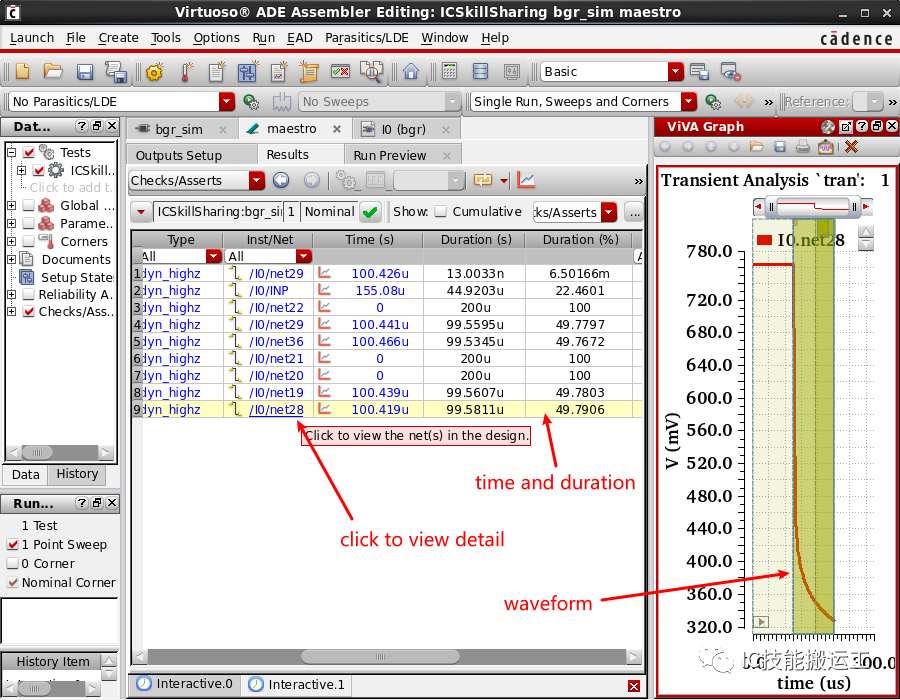

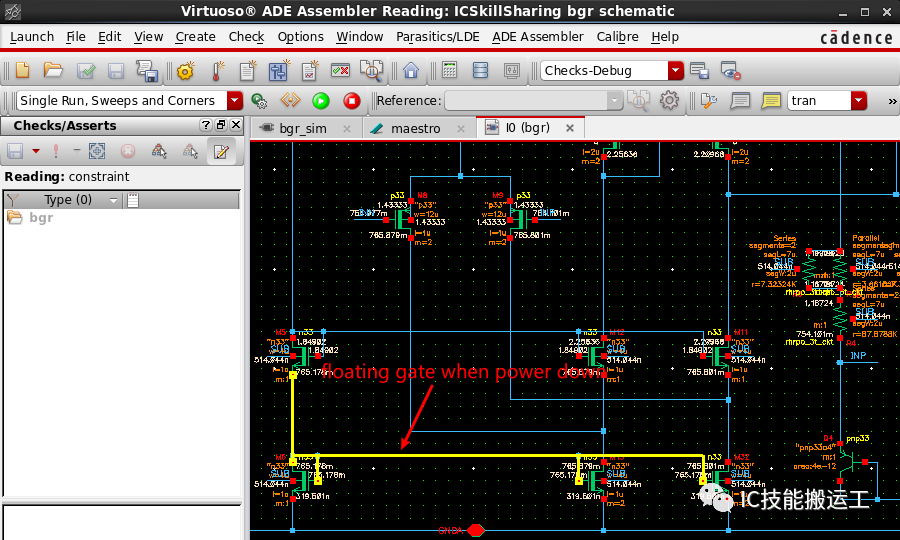

仿真完成之后,通過結果查看器檢查電路中存在的違例,查看結果過程中,通過點擊鏈接可以打開原理圖直接查看違例情況以及對于的瞬態波形。

在檢查設置時,Fanout一項小目同學選擇gate,所以上面結果顯示:被檢查的電路存在9個floating gate的違例,我們可以通過點擊查看具體違例產生的時間、對應的節點和電路波形。

根據結果確定電路中相應節點是否存在隱患,根據實際情況對電路進行修改,添加高阻節點放電通路等。

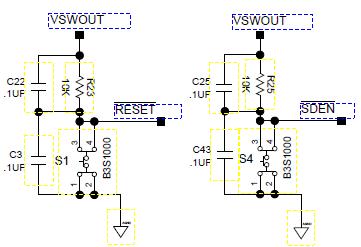

從結果來看,檢查中報出的floating gate隱患主要是該電路中未添加gate的power down電路,所以導致電路下電后存在floating gate,該隱患可能導致電路下電后異常漏電。

審核編輯:湯梓紅

-

電路

+關注

關注

172文章

5962瀏覽量

172726 -

原理圖

+關注

關注

1300文章

6358瀏覽量

234887 -

仿真

+關注

關注

50文章

4124瀏覽量

133867 -

ade

+關注

關注

0文章

29瀏覽量

15470

原文標題:如何利用ADE Assembler檢查電路中的floating gate?

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

無法為單個數據類型找到Assembler浮點庫IEEE 754

ADE7756中文資料

ADE7116/ADE7156/ADE7166/ADE716

HV Floating MOS-Gate Driver IC

什么是BAS (Basic Assembler Progra

ADE7854_ADE7858_ADE7868_ADE7878 pdf

Mixing_C_and_Assembler_With_the_MSP430

8052單片機RTC和LCD驅動的單相能量測量集成電路ADE5166/ADE5169/ADE5566/ADE5569數據表

8052單片機RTC和LCD驅動的單相能量測量集成電路ADE7116/ADE7156/ADE7166/ADE7169/ADE7566/ADE7569數據表

如何利用ADE Assembler檢查電路中的floating gate?

利用ADE9153A在系統中添加電能監控功能的PCB布局考量

如何利用ADE Assembler檢查電路中的floating gate

如何利用ADE Assembler檢查電路中的floating gate

評論