一、概述:

SAR ADC 是逐次逼近 ADC 的簡稱(successive approximation register),SAR ADC 的主要優點是低功耗、小尺寸、高精度,分辨率和速度適中,采樣延時短,是一種經濟型的 ADC 實現方案,故在MCU/SOC 中廣泛采用。

二、SAR ADC工作原理:

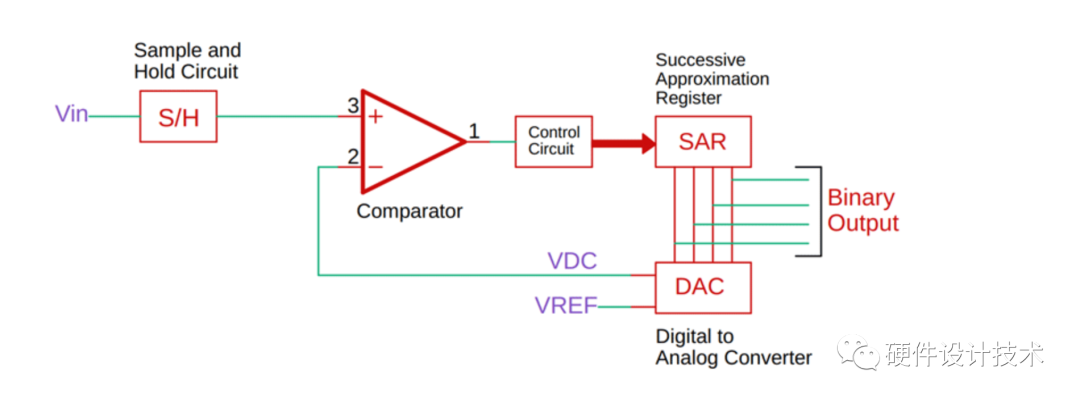

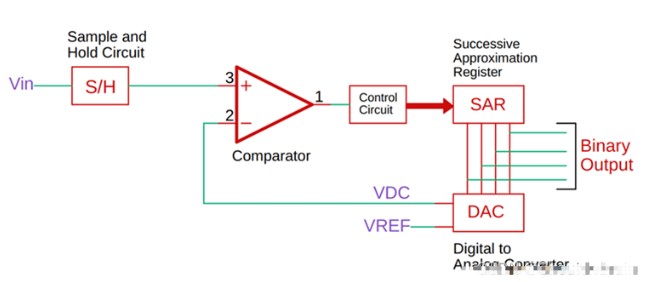

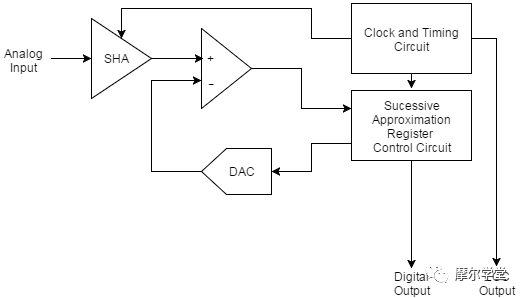

SAR ADC 的基本結構包括:

采樣保持電路(Sample and Hold)

比較器(Comp)

控制電路(Control)

D/A 轉換電路(DAC)

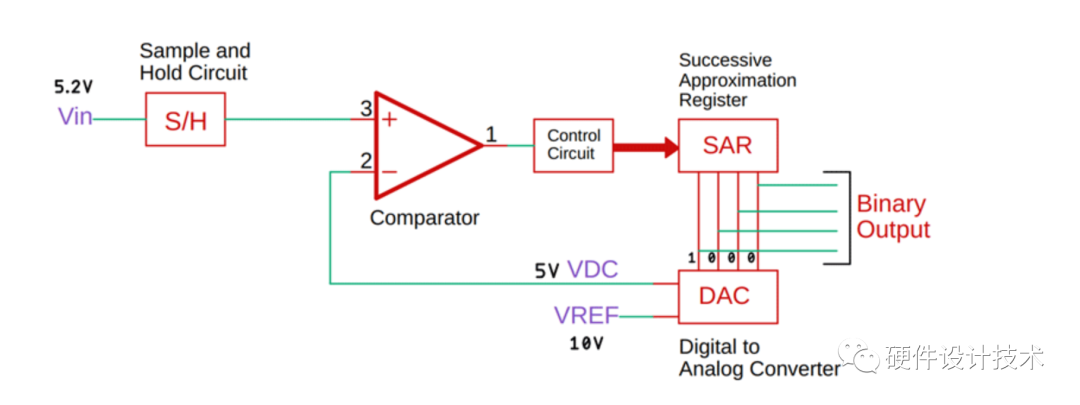

如下圖所示,假設采樣的輸入信號為 5.2V。ADC 的參考電壓為 10V。當轉換開始時,逐次逼近寄存器將最高有效位設置為 1,并將所有其他位設置為零。這意味著該值變為 1000,這意味著對于 10V 參考電壓,DAC 將產生 5V 值,即參考電壓的一半。現在,該電壓將與輸入電壓進行比較,并根據比較器的輸出,逐次逼近寄存器的輸出將發生變化。

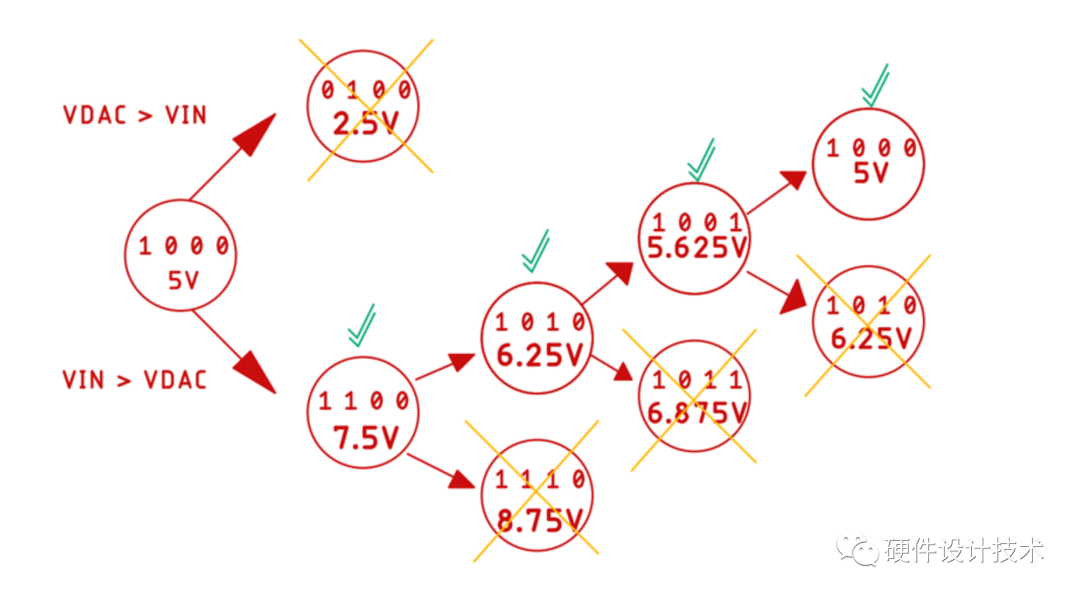

這意味著如果 Vin 大于 DAC 的輸出,最高有效位將保持原樣,而下一位將被設置用于新的比較。否則,如果輸入電壓小于 DAC 值,則最高有效位將設置為零,下一位將設置為 1 以進行新的比較。現在,如果看到下圖,DAC 電壓為 5V,并且由于它小于輸入電壓,最高有效位之前的下一位將設置為 1,而其他位將設置為零,此過程將一直持續到最接近輸入電壓的值達到。

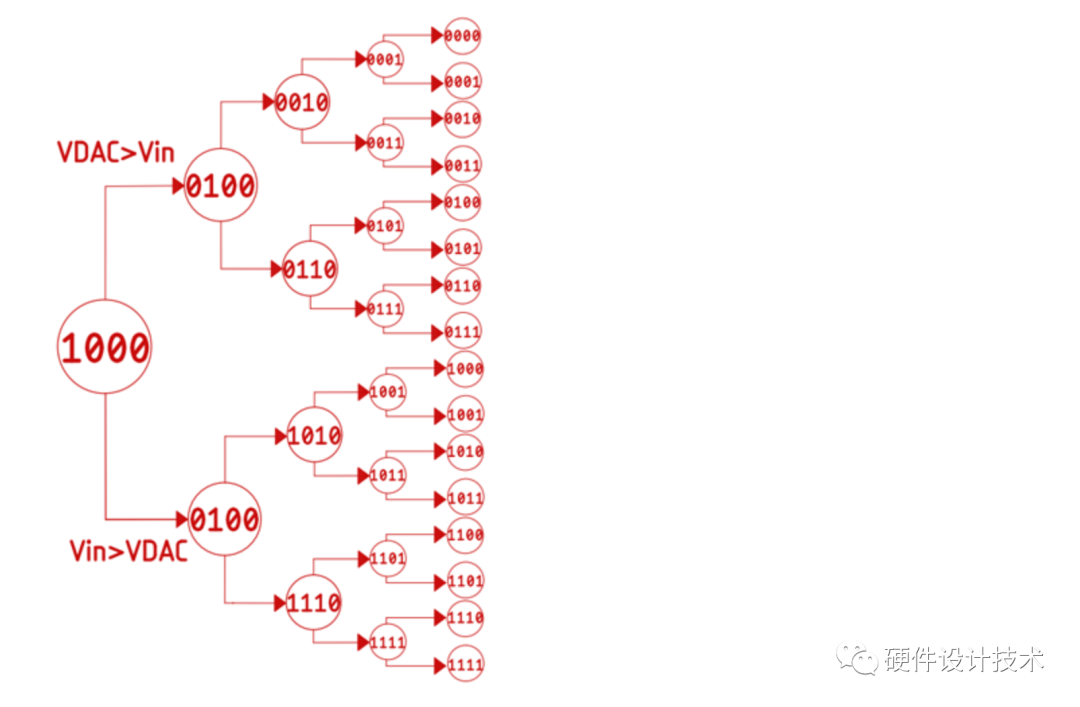

這就是逐次逼近型 ADC 一次改變 1 位以確定輸入電壓并產生輸出值的方式。無論四次迭代中的值是什么,都將從輸入值中獲得輸出數字代碼。最后,四位逐次逼近 ADC 的所有可能組合列表如下所示。

三、SAR ADC關鍵指標:

3.1、轉換時間:

一般來說,我們可以說對于一個 N 位 ADC,需要 N 個時鐘周期,這意味著這個 ADC 的轉換時間將變為:

Tc = N* Tclk --------Tc 是轉換時間的縮寫

SAR ADC與其他 ADC 不同的是,SAR ADC 的轉換時間與輸入電壓無關。由于我們使用 4 位 ADC講解,為了避免混疊效應,我們需要在 4 個連續時鐘脈沖后進行采樣。

3.2、速度:

SAR ADC 的典型轉換速度約為每秒 2 - 5 兆樣本 (MSPS),但很少有能達到 10 (MSPS) 的。

3.3、分辨率:

SAR ADC 的分辨率約為 8 - 16 位,但某些類型可達 20 位。

四、SAR ADC的優點和缺點:

與其他類型的 ADC 相比,SAR ADC 具有許多優點。它具有高精度、低功耗、易于使用且延遲時間短的特點。延遲時間是信號采集開始的時間以及可從 ADC 獲取數據的時間,通常此延遲時間以秒為單位定義。但也有一些數據表將此參數稱為轉換周期,在特定 ADC 中,如果數據可在一個轉換周期內獲取,我們可以說它具有一個對話周期延遲。如果數據在 N 個周期后可用,我們可以說它有一個轉換周期的延遲。

SAR ADC 的一個主要缺點是其設計復雜性和生產成本。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5394瀏覽量

122423 -

SAR

+關注

關注

3文章

421瀏覽量

46547 -

adc

+關注

關注

99文章

6594瀏覽量

547446 -

比較器

+關注

關注

14文章

1768瀏覽量

108100 -

MCU控制

+關注

關注

0文章

48瀏覽量

6872

原文標題:ADC講解: SAR-ADC

文章出處:【微信號:硬件設計技術,微信公眾號:硬件設計技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SAR ADC簡介及工作過程

這個SAR ADC怎么樣?

序列 SAR ADC 使您能夠在 PSoC 4 上配置和使用不同操作模式的 SAR ADC

SAR ADC的原理以及SAR ADC驅動電路設計要點

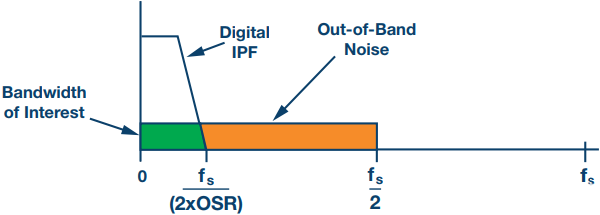

使用過采樣增加SAR ADC的動態范圍

SAR ADC的隔離

評論