本文介紹一個FPGA開源項目:UDP RGMII千兆以太網通信。該項目在我之前的工作中主要是用于FPGA和電腦端之間進行圖像數據傳輸。本文簡要介紹一下該項目的千兆以太網通信方案、以太網IP核的使用以及Vivado工程源代碼結構。

Vivado 的 Tri Mode Ethernet MAC IP核需要付費才能使用,因此本文提供完整工程源碼。

01軟硬件平臺

- 軟件平臺:Vivado 2017.4;

- 硬件平臺:XC7K410TFFG900-2;

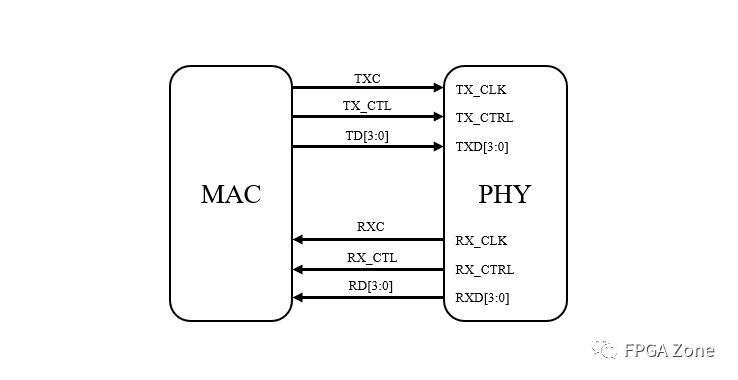

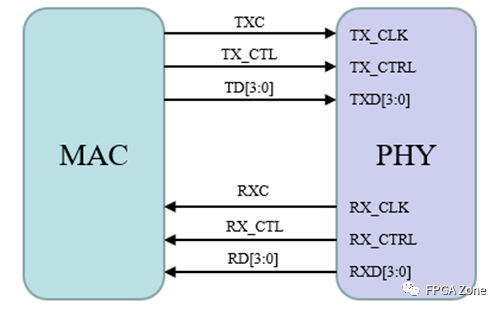

02RGMII接口

本設計采用 RGMII 接口的 88E1512 芯片。RGMII 接口的主要優勢在于,它可以同時適用于1000M、100M、10M三種速率,并且接口占用引腳數較少。

RGMII 使用 4bit 數據接口采用上下沿 DDR(Double Data Rate)的方式在一個時鐘周期內傳輸 8bit 數據信號,即上升沿發送或者接收數據的低4位[3:0],下降沿發送或者接收數據的高4位[7:4]。同理,使用 1bit 控制接口采用 DDR 的方式在一個時鐘周期內傳輸 2bit 控制信號。

- 發送端:tx_clk,tx_d[3:0],tx_ctrl;

- 接收端:rx_clk,rx_d[3:0],rx_ctrl;

- 三種速率模式

RGMII 接口適用于1000M、100M、10M三種傳輸速率。

當工作于1000M時,時鐘信號TXC和RXC均為 125MHz,4bit數據信號上下沿值均有效,控制信號上下沿值也均有效。

當工作于100M時,時鐘信號TXC和RXC均為25MHz,4bit數據信號只有上升沿值[3:0]有效,相當于此時數據信號切換為單沿SDR(Single Data Rata)4位輸模式。控制信號仍為上下沿有效。

當工作于10M時,時鐘信號TXC和RXC均為2.5MHz,數據信號和控制信號的使用和100M速率時完全相同。

03UDP通信方案

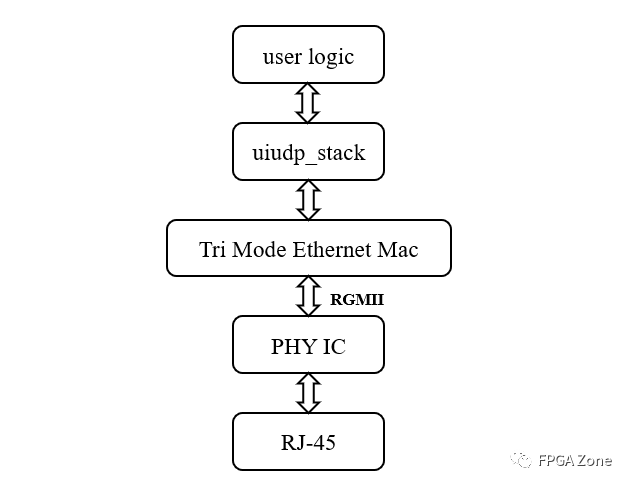

該以太網通信方案參考米聯客例程設計,硬件接口采用RGMII,IP核調用Vivado 的 Tri Mode Ethernet MAC。通信方案如下圖所示,最上層為用戶邏輯模塊,用于處理和使用解析后的以太網通信數據;uiudp_stack 模塊采用米聯客例程提供的協議棧網表文件;FPGA 以太網IP核采用Tri Mode Ethernet Mac;PHY芯片采用 88E1512;最后 RJ-45 接口通過網線與上位機連接。

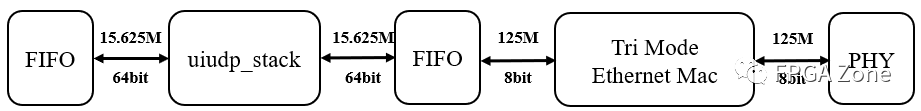

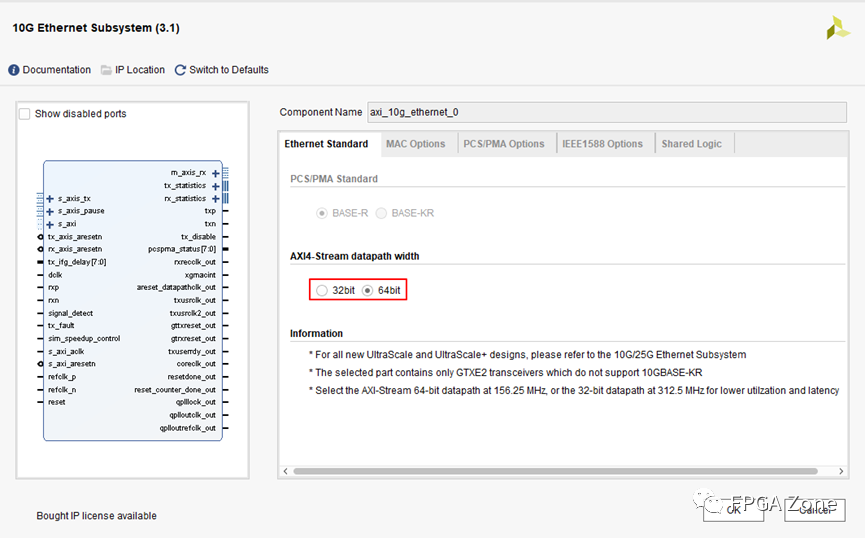

下圖為以太網數據環路傳輸測試方案,在電腦上通過網絡調試助手向FPGA發送任意小于1472字節長度的UDP數據包。由于Tri Mode Ethernet Mac IP核接口數據流為8bits/125M,而uiudp_stack為64bits/15.625M,因此需要在中間插入FIFO緩存模塊,進行數據位寬轉換以及數據跨時鐘域處理。

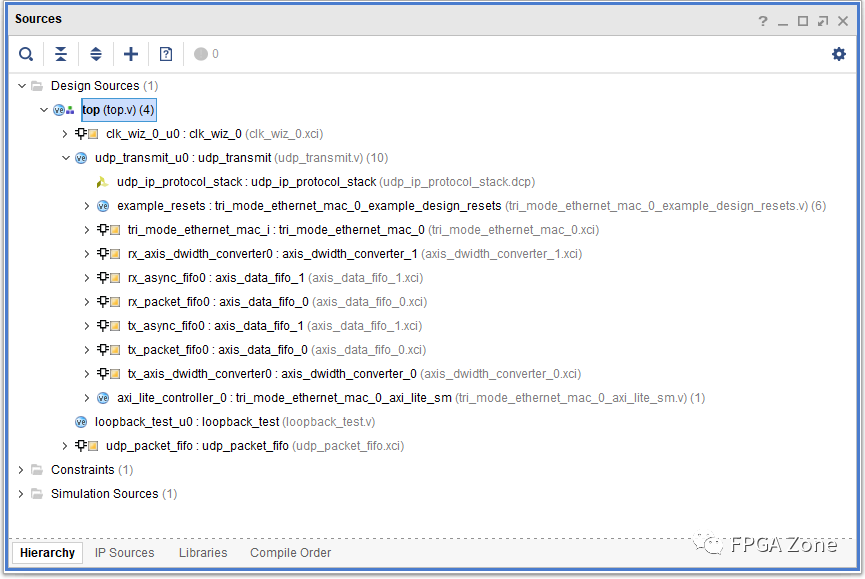

04工程源碼結構

下圖是該項目 Vivado 工程源碼結構:

其中,

- udp_transmit:UDP以太網數據收發模塊;

- loopback_test:UDP以太網數據回環傳輸測試模塊;

- tri_mode_ethernet_mac_0_axi_lite_sm:用于配置、讀取以太網IP核寄存器等。

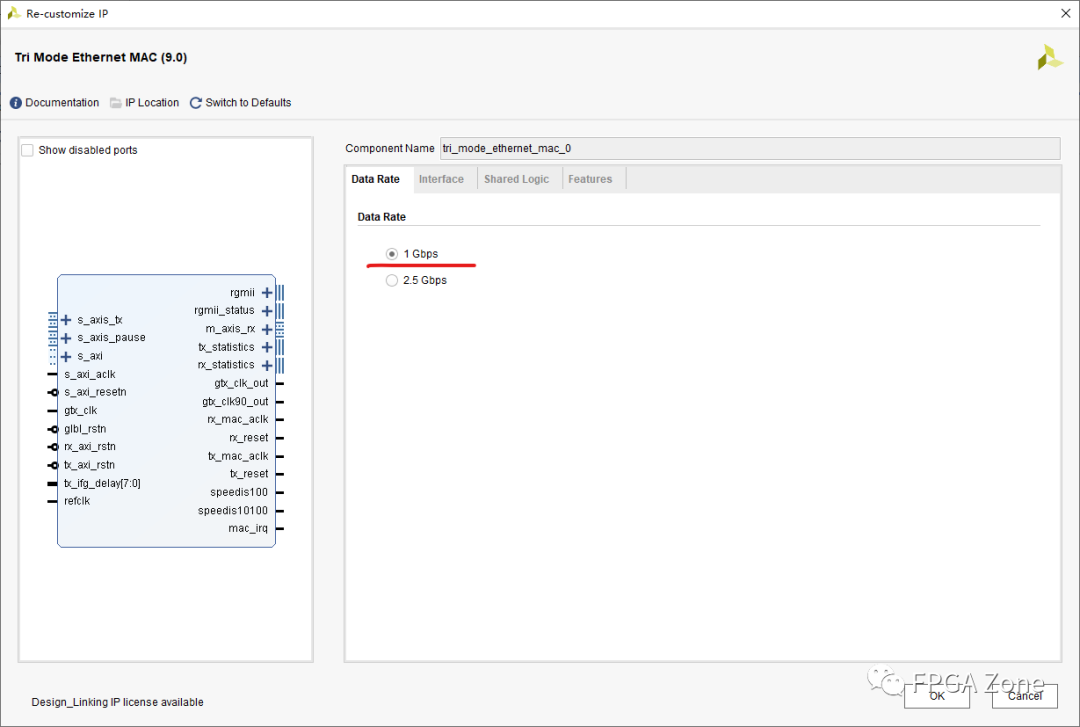

05IP核參數配置

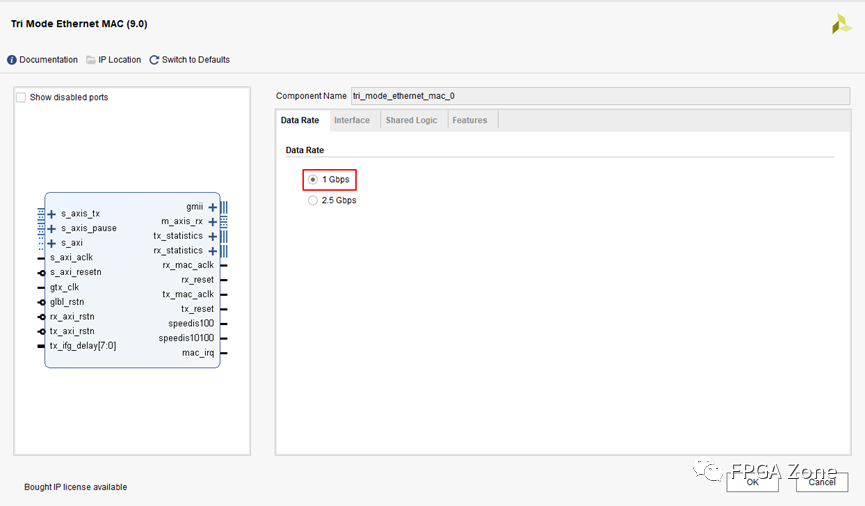

使用千兆通訊,因此將速率設為 1Gbps;

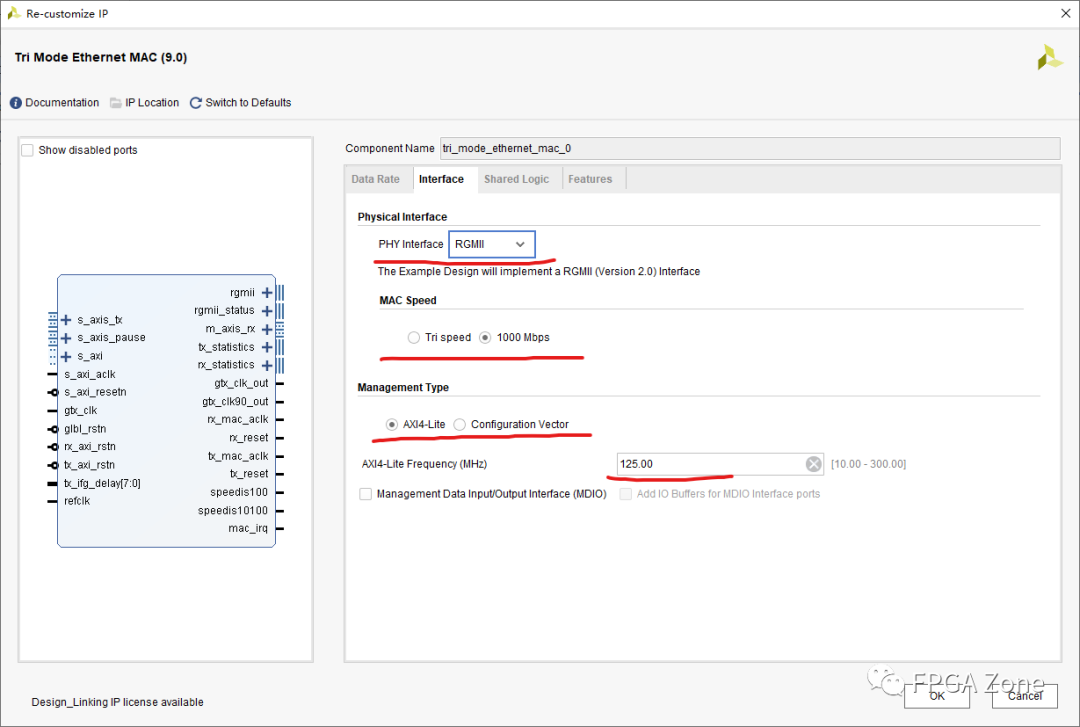

接口參數配置如下:

另外,有關 UDP 協議棧 uiudp_stack 的詳細信息這里不再介紹,其pdf文檔和源碼一起提供,有需要的小伙伴可以自己去查閱。

06其它注意事項

- PHY芯片 復位信號 :上電后將復位信號拉高;

- FPGA RGMII輸出 I/O 口 電平標準 :配置成 SSTL 電平標準。

-

FPGA

+關注

關注

1637文章

21842瀏覽量

608531 -

千兆以太網

+關注

關注

0文章

69瀏覽量

13949 -

UDP

+關注

關注

0文章

329瀏覽量

34176 -

Vivado

+關注

關注

19文章

819瀏覽量

67308 -

RGMII

+關注

關注

0文章

28瀏覽量

12247

發布評論請先 登錄

相關推薦

DE2-115開發板以太網通信問題

以太網通訊控制儀器,使用UDP協議,儀器無響應

簡談基于FPGA的千兆以太網設計

基于FPGA的UDP RGMII千兆以太網設計

基于FPGA的UDP RGMII千兆以太網通信方案

基于FPGA的UDP RGMII千兆以太網通信方案

評論