近日,第五屆集成電路EDA設計精英挑戰賽正式啟幕。作為國內EDA領域的專業賽事之一,芯華章已連續四年參與支持賽事,持續助力產業人才培養、深化產學研合作,為中國EDA產業培養和儲備優秀的新生代技術力量。今年,芯華章發布“基于VCD的FSM覆蓋率統計”企業賽題,歡迎各位同學們前來“破題”!

一、 賽題名稱

基于VCD的FSM覆蓋率統計

二、 背景知識

Coverage是衡量數字驗證質量的重要指標,FSM Coverage作為其中重要一環,衡量了驗證過程中的狀態和狀態轉移覆蓋狀況。通過檢查各狀態和狀態轉移是否被覆蓋到,我們可以檢查預期的功能是否被覆蓋;相反的,通過檢查是否有不在設計范圍內的狀態或狀態轉移被意外覆蓋到,進而檢測到設計中的漏洞。

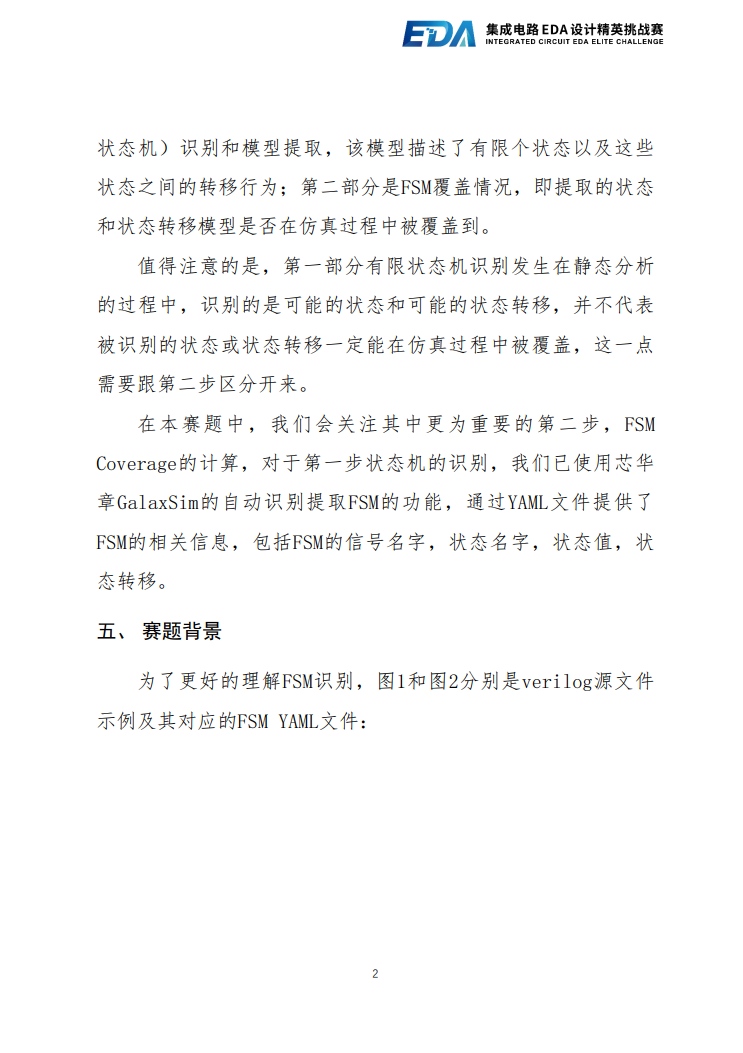

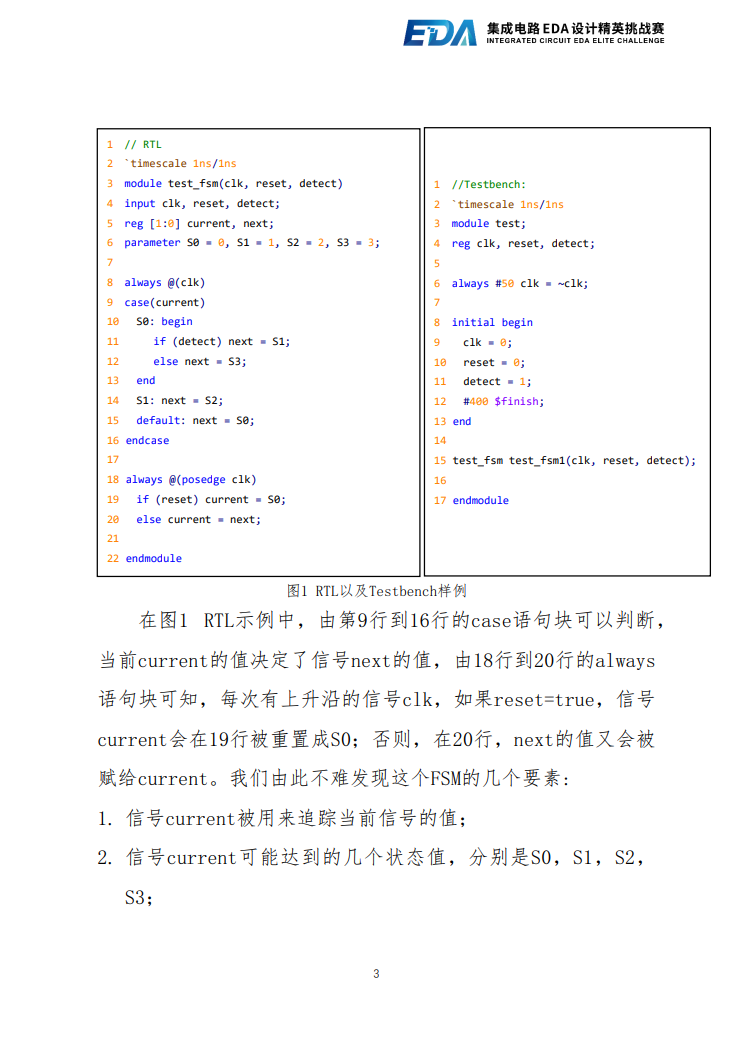

FSM Coverage通常包括兩部分內容,第一部分是FSM(有限狀態機)識別和模型提取,該模型描述了有限個狀態以及這些狀態之間的轉移行為;第二部分是FSM覆蓋情況,即提取的狀態和狀態轉移模型是否在仿真過程中被覆蓋到。

值得注意的是,第一部分有限狀態機識別發生在靜態分析的過程中,識別的是可能的狀態和可能的狀態轉移,并不代表被識別的狀態或狀態轉移一定能在仿真過程中被覆蓋,這一點需要跟第二步區分開來。

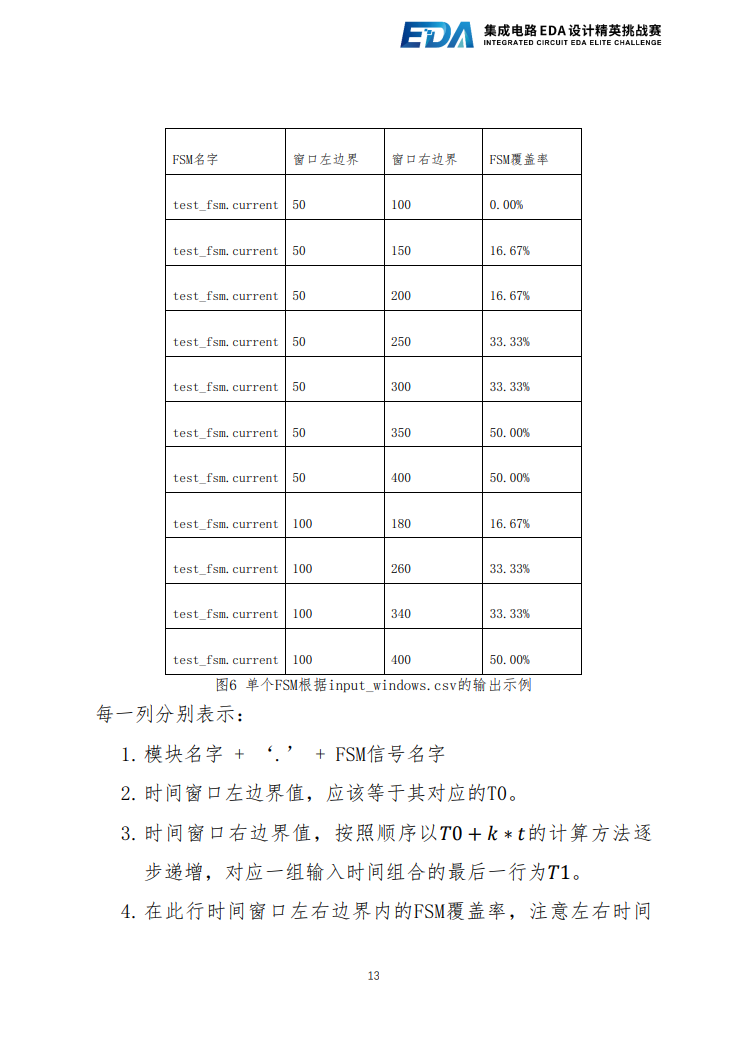

在本賽題中,我們會關注其中更為重要的第二步,FSM Coverage的計算,對于第一步狀態機的識別,我們已使用芯華章GalaxSim的自動識別提取FSM的功能,通過YAML文件提供了FSM的相關信息,包括FSM的信號名字、狀態名字、狀態值、狀態轉移。

三、 賽題指南

向左滑動查看更多內容>>

掃碼下載芯華章賽題文檔

四、 賽題Chair

李 康

李康博士,西安電子科技大學微電子學院副教授,碩士導師。研究方向主要包括數字集成電路設計、優化與自動化技術。熟悉體系結構與組成技術,并長期從事面向高速網絡交換的電路設計以及PPA優化方法研究。同時開展可靠性器件與電路模型技術研究,開發數字電路可靠性退化與壽命的預測模型與高可靠性數字電路設計方法,建立起超深亞微米集成電路可靠性評估平臺。研究AI與設計自動化領域的技術相結合的高效高精度功耗預測技術,研發出系統芯片的功耗評估工具。先后承擔相關方向的VLSI 重大專項、國家自然基金項目、科技部重點研發計劃、部委預研及企業合作研究項目10余項,發表SCI與EI索引論文20余篇,授權專利8項。

五、 大賽時間

2023(第五屆)集成電路EDA設計精英挑戰賽賽程時間安排如下:

EDA設計精英挑戰賽現已正式開放報名,關注官網(http://eda.icisc.cn),獲取更多大賽信息。

六、 獎項設置

麒麟杯(1支):20萬

菁英杯(1-2支):8萬

一等獎(最高15%):2萬

二等獎(最高30%):1萬

關于芯華章科技

芯華章聚集全球EDA行業精英和尖端科技領域人才,以智能調試、智能編譯、智能驗證座艙、智能云原生等技術支柱,構建芯華章平臺底座,提供全面覆蓋數字芯片驗證需求的七大產品系列,包括:硬件仿真系統、FPGA原型驗證系統、智能場景驗證、形式驗證、邏輯仿真、系統調試以及驗證云,為合作伙伴提供自主研發、安全可靠的芯片產業解決方案與專家級顧問服務。同時,芯華章致力于面向未來的EDA 2.0 智能化電子設計平臺的研究與開發,以技術革新加速系統創新效率,讓芯片設計更簡單、更普惠。

-

芯華章

+關注

關注

0文章

178瀏覽量

11457

原文標題:誠邀破題!集成電路EDA設計精英挑戰賽芯華章賽題發布!

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【賽題發布】2025集創賽中科億海微賽道正式啟動!

2024 FPGA和EDA雙賽事安路科技再創佳績

廣立微助力2024中國研究生創“芯”大賽·EDA精英挑戰賽

e絡盟社區攜手恩智浦發起智能空間樓宇自動化挑戰賽

誠邀破題!集成電路EDA設計精英挑戰賽芯華章賽題發布!

誠邀破題!集成電路EDA設計精英挑戰賽芯華章賽題發布!

評論