續(xù)上一集,LTspice(3) 差放分幾種玩法?基于CSA23x-1

通過簡單的例子大概知道怎么去寫一個仿真模型,就像是畫電路圖將網(wǎng)表直接寫出一樣,根本不需要原理圖直接畫pcb那么騷。感覺比直接畫原理圖還要有意思的多。

有點像是憑空搭洞洞板的感覺。記得讀書時候考試科目就是拿洞洞板搭電路。

回到正題,之前語句中使用了E1 這個東西,那么E1是做什么用的?

.subckt div N1 N2 GND

R1 N1 0 100k

E1 N2 0 N1 0 50

.ends div

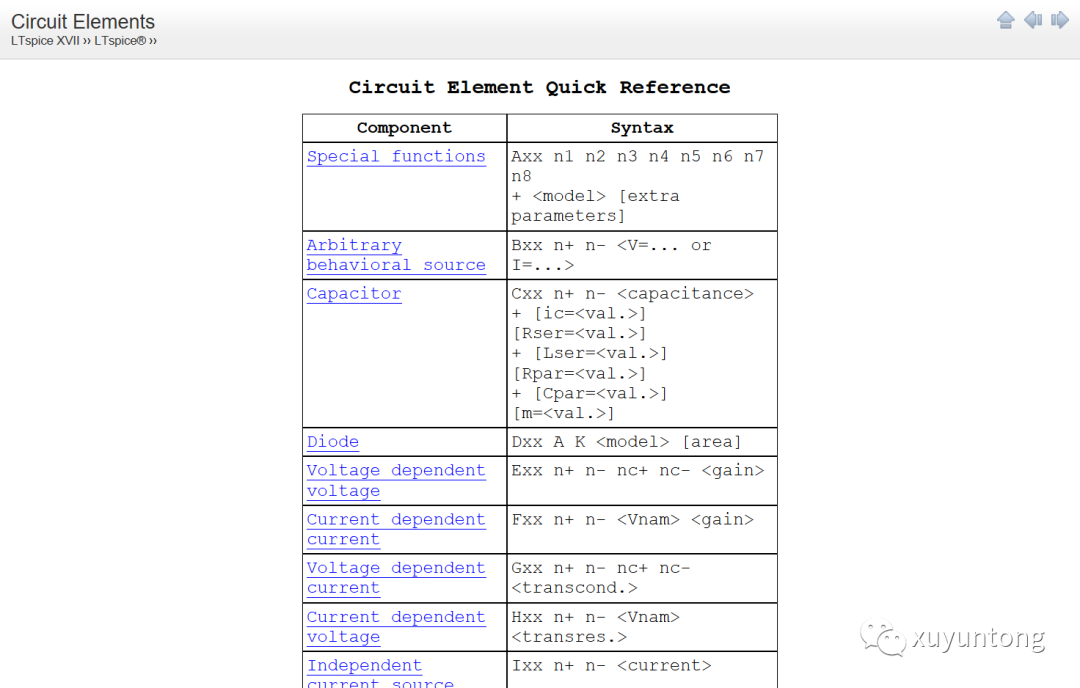

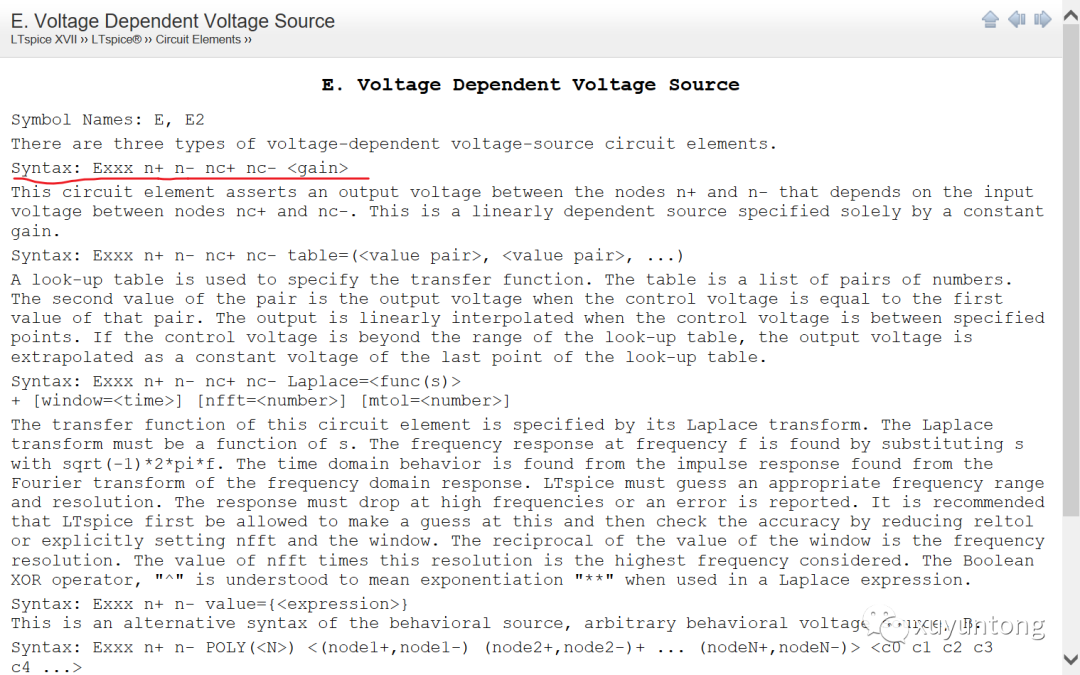

打開LTspice幫助找到以下頁面 點到 voltage dependent voltage 里面有關(guān)于電壓源的描述

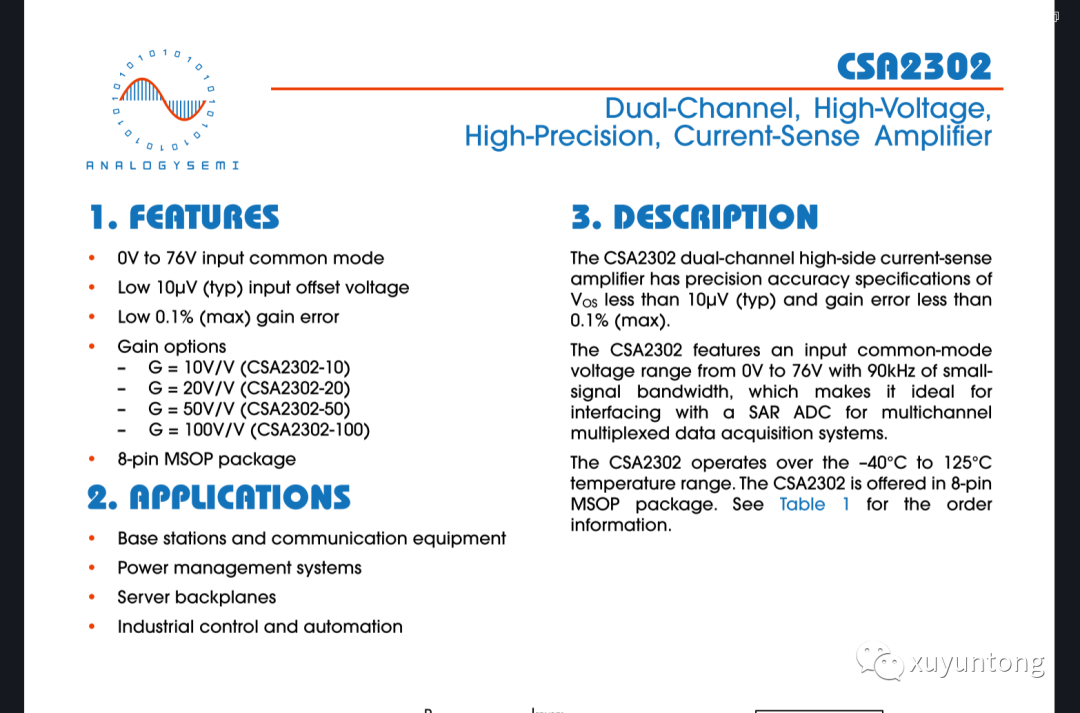

大概意思就是說,輸出電壓是N+和N-輸入電壓是Nc+和NC-其關(guān)系是兩個之間的GAIN的倍數(shù)。因為CSA23設置的是50倍所以我們整個50倍的。

*

* This is the circuit definition

.subckt CSA23 IN+ IN- VOUT REF GND

*set input and output pins

*the setting gain is equal to 50

*join to network Vo

E1 VO REF IN+ IN- 50

*join to offset 1mV m=micro Meg=mega

E2 VOUT REF value={V(VO,REF)+1m}

.ends CSA23

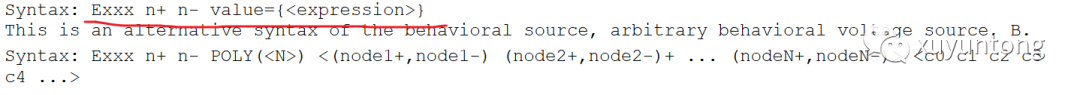

其中第9行代碼寫到,value={V(VO,REF)+1m}這個似乎沒有看過,接著往下拉。

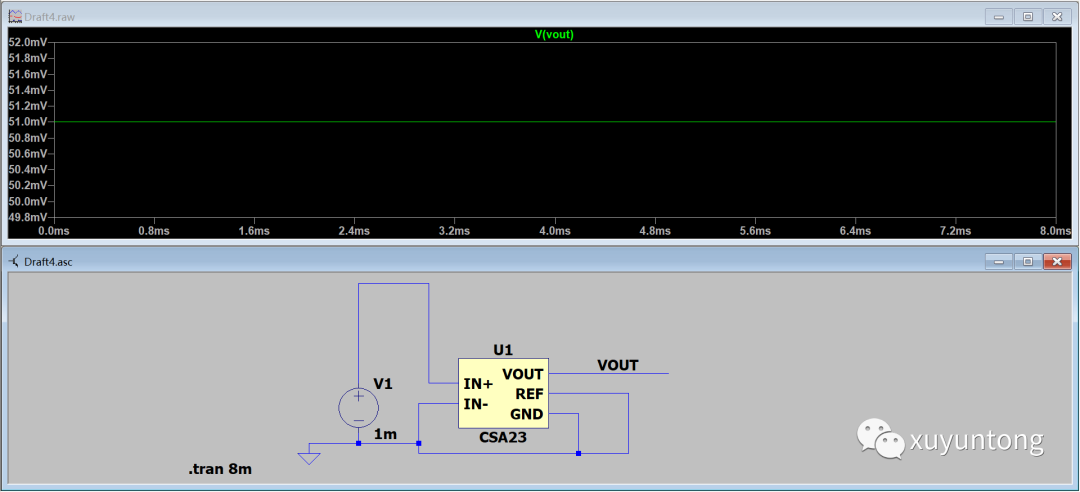

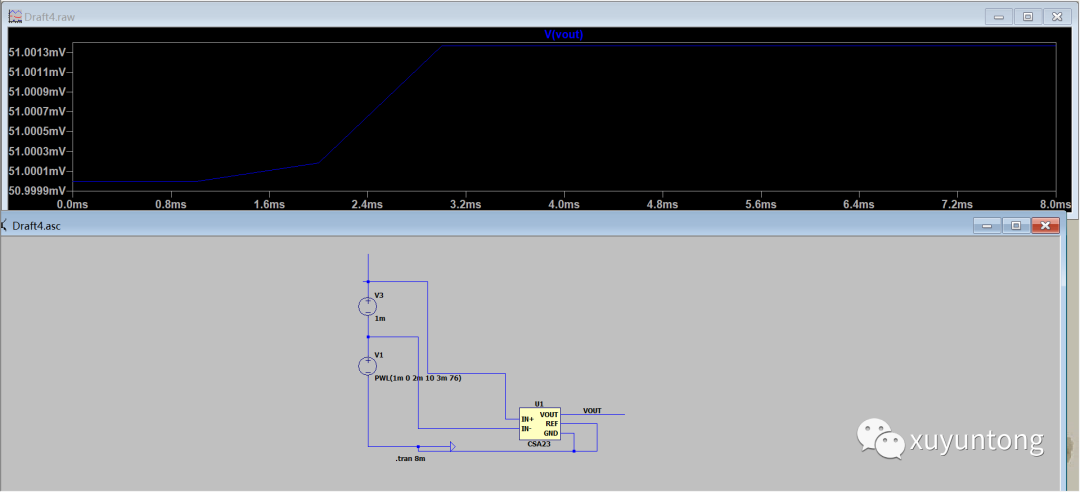

他是可以支持自定義表達式的,就是說你想要什么對應關(guān)系直接把你想要的對應關(guān)系寫進去就行,這里我只加個offset。新建器件仿真得出下圖。50倍增益1mV的失調(diào)電壓。基本function有了可以開始整活了。

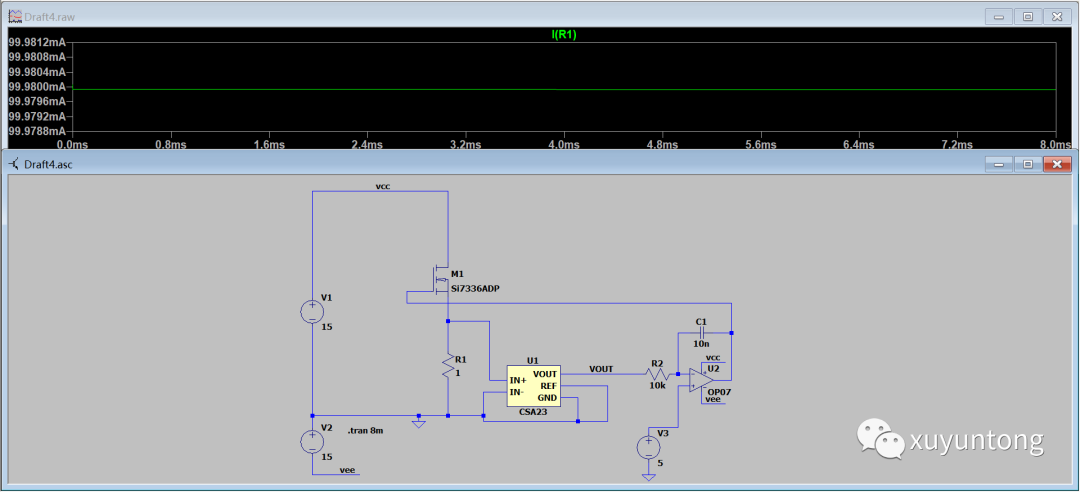

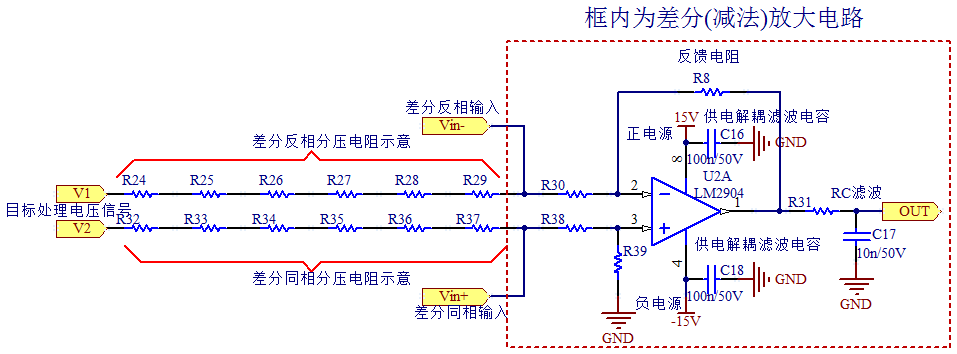

上回似乎說到用ldo做恒流源,但是此次可以用CSA23做恒流源。其實現(xiàn)如下

R1100mAGAIN+offset=5V所以其電流約等于99.98mA,當然初始誤差可以通過dac校準掉,對我們沒有多大影響,但是共模的變化就會導致誤差動態(tài)變化,這個就比較難校準掉,所以建議選擇共模抑制比比較好的運算放大器。

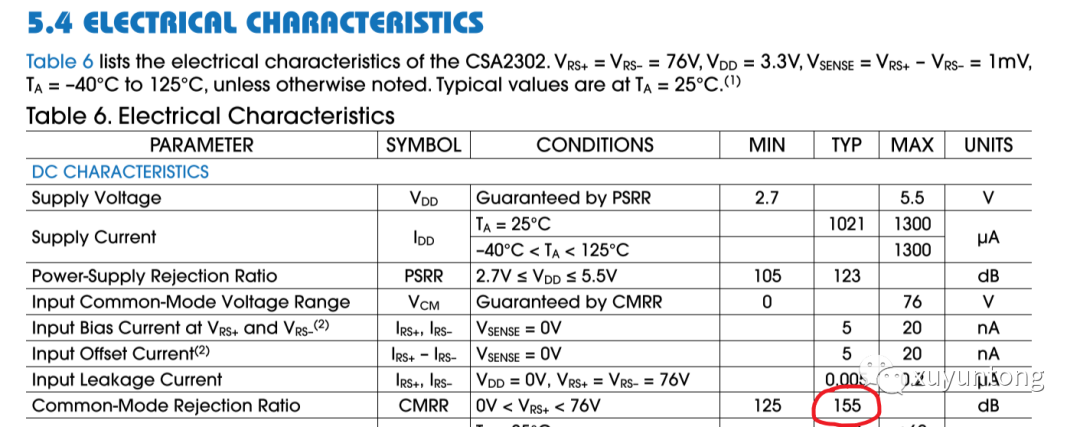

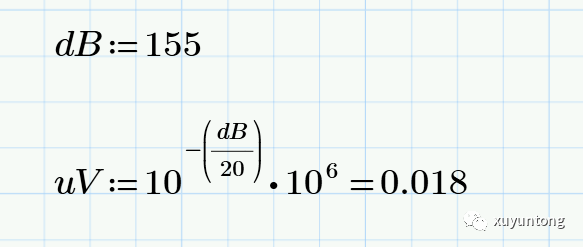

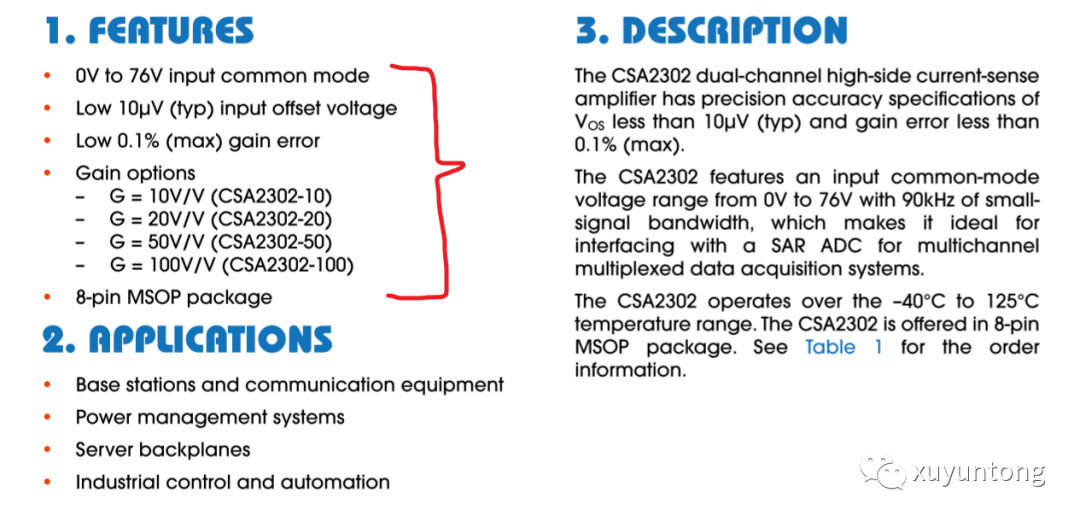

CSA2302的CMRR在0~76V的范圍內(nèi)典型值為155db,代入計算。

db和倍數(shù)的關(guān)系是這樣

20log(10,AV)=db

得出的是輸入的共模電壓每變化1V那么輸出電壓變化0.018uV

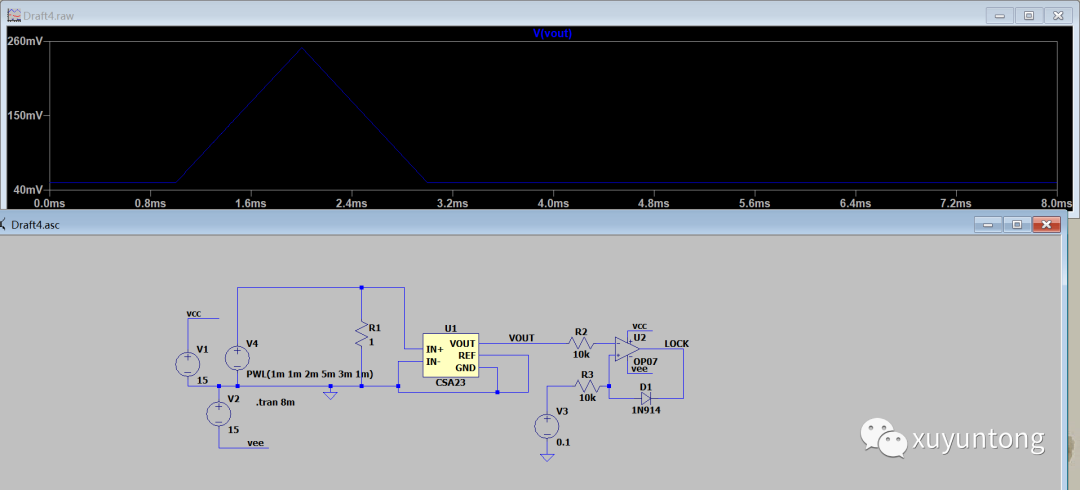

既然如此那我們再次更新下模型。

*

* This is the circuit definition

.subckt CSA23 IN+ IN- VOUT REF GND

*set input and output pins

*the setting gain is equal to 50

*join to network Vo

E1 VO REF IN+ IN- 50

*join to offset 1mV m=micro Meg=mega

E2 VOUT REF value={V(VO,REF)+1m+V(IN-,0)*0.018u}

.ends CSA23

看到不同共模電壓變化的時候輸出電壓變化并不是特別大。其V1作為電壓源設置從0V到76V輸出電壓變化非常小。因為比較高的CMRR其電流高位采樣的精度就有保證。剩下的事就交給DAC去吧~

-

運算放大器

+關(guān)注

關(guān)注

215文章

4966瀏覽量

173377 -

PCB設計

+關(guān)注

關(guān)注

394文章

4697瀏覽量

86095 -

LDO電源

+關(guān)注

關(guān)注

0文章

63瀏覽量

10486 -

CMRR

+關(guān)注

關(guān)注

0文章

84瀏覽量

14826 -

LTspice

+關(guān)注

關(guān)注

1文章

118瀏覽量

13448

發(fā)布評論請先 登錄

相關(guān)推薦

LTspice差放分幾種玩法?基于CSA23x-2

LTspice差放分幾種玩法?基于CSA23x-2

評論