就像PCB中的高縱橫比通孔和小直徑通孔一樣,半導體封裝中的3D互連也面臨著與3D晶片堆棧的熱力學行為相關的可靠性挑戰。同樣的挑戰也出現在用于2.5和3D封裝的硅中間層的3D互連中。具有諷刺意味的是,這些可靠性挑戰最初是在圍繞半導體的學術文獻中觀察到的,現在PCB行業正在處理與電子組裝規模較小相同的挑戰。

目前的垂直互連技術由硅通孔組成,其中銅互連用于在中間插口或堆疊小片中的電觸點之間路由垂直連接。隨著越來越多的設計以更高的功率運行,并且在垂直堆疊中包含更多的骰子,3D集成封裝的熱機械可靠性成為系統級設計中需要解決的一個重要問題。

#1

TSV可靠性失效機制

TSV的可靠性研究已經進行了多年,并提出了許多提高TSV可靠性的解決方案。確保任何制造結構的可靠性需要了解主要失效機制,在TSV中可以觀察到的兩種主要失效機制是:

CTE失配引起的應力

TSV電遷移失敗

這些失效機制可以在用于2.5D/3D封裝的中間體的TSV中觀察到,也可以在用于3D堆疊小芯片的TSV中觀察到。

#2

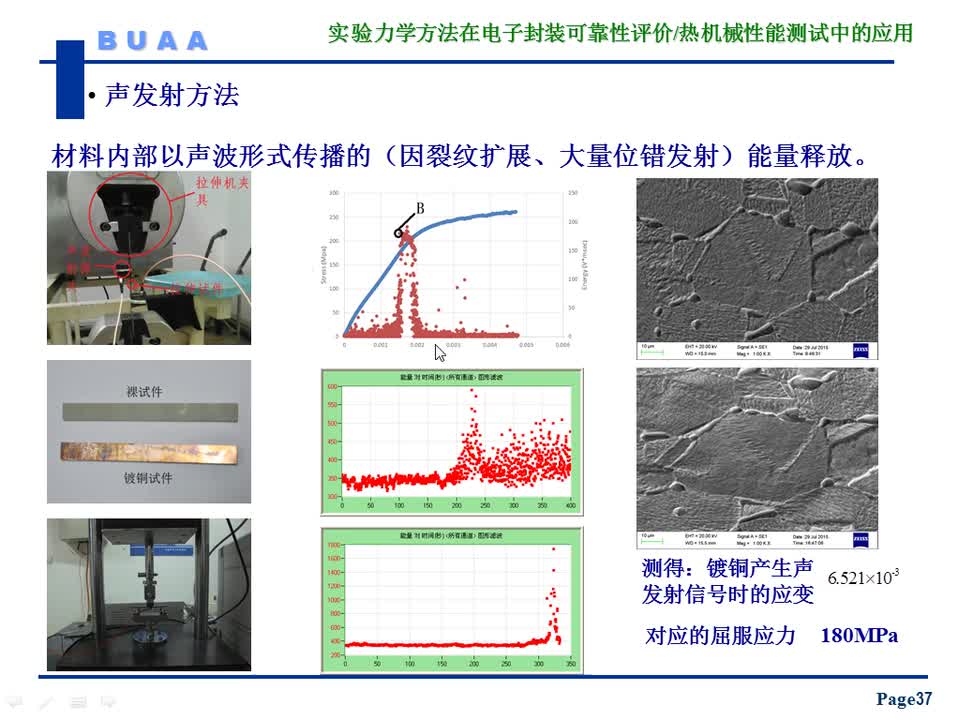

應力導致開裂

應力誘發的TSV結構失效主要是由于硅(2-3ppm/°C)和銅(16-17ppm/°C)之間的CTE不匹配。與PCB中使用的較大過孔和HDI PCB中使用的微過孔一樣,TSV各部分的應力集中將導致不同類型的機械誘發故障。此外,熱循環會導致TSV結構的應力集中區域出現疲勞。

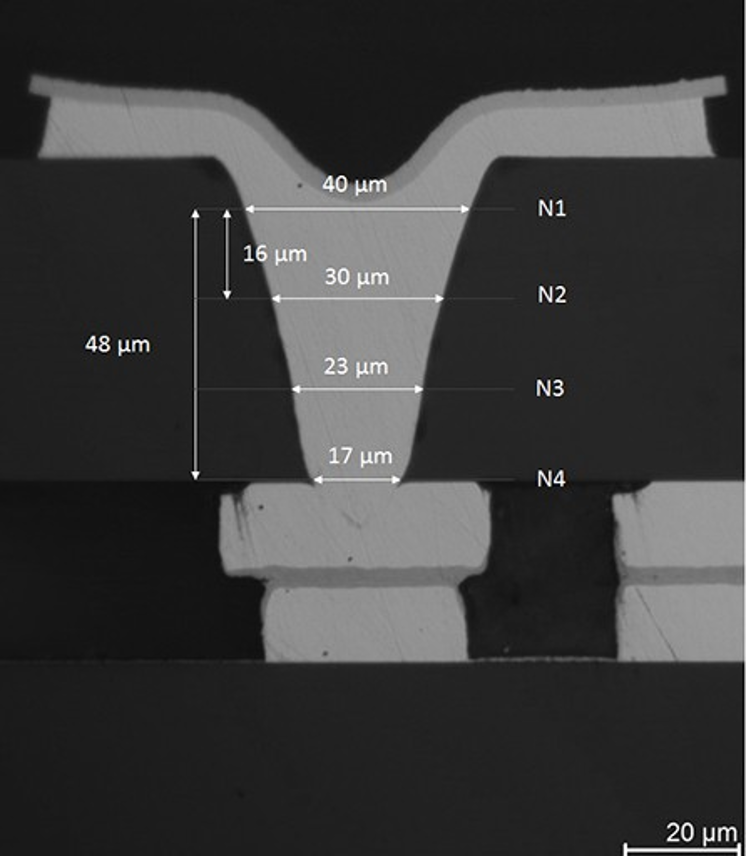

如果我們檢查TSV結構的橫截面,它看起來非常類似于HDI PCB中的盲通結構。較大的熱失配會在TSV的上下表面產生應力集中,導致銅斷裂、擴散和污染等多種影響。

掃描電鏡圖像顯示TSV在微凸點頂部的橫截面

(來源:弗勞恩霍夫電子納米系統研究所)

在這種類型的結構中可能出現的一些問題包括:

將銅泵入后端管線(BEOL)區域或再分配層(RDL)

銅沿銅-半導體界面從種子層剝離

退火效應(銅形態的變化)由于反復的熱循環和膨脹/收縮

銅在長時間暴露于高溫后從結構中擴散出去

形成脆性金屬間化合物,更容易斷裂

#3

TSV中的電遷移

電遷移是長期可靠性的另一個驅動因素,當TSV結構開始出現裂紋時,電遷移會加速機械失效。TSV中的電遷移發生的機制與集成電路中的軌道相同:金屬在電流影響下的擴散。中間層和3D堆疊小芯片中使用的TSV必須通過堆疊攜帶一些電流,為封裝中的組件提供電源和信號.

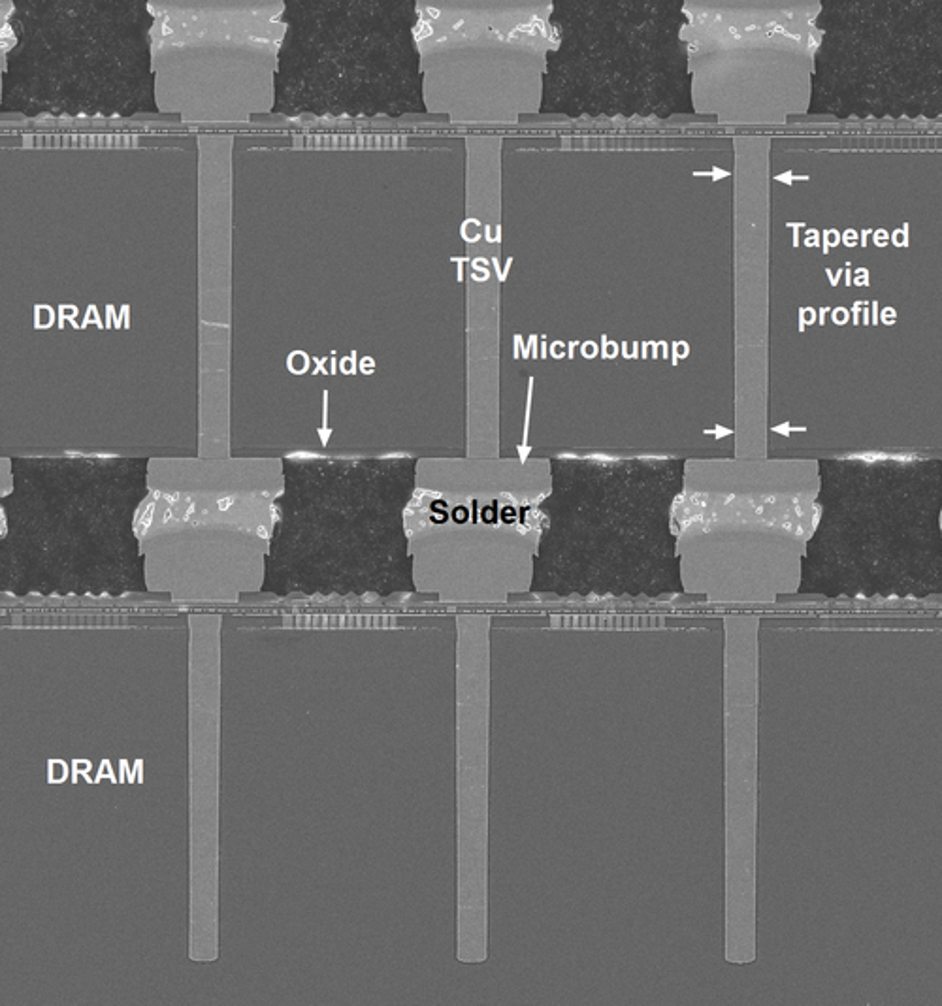

較小的TSV通常用于3D堆疊芯片,由于尺寸較小,在給定電壓水平下通常攜帶更大的電流密度。根據布萊克方程,這意味著對于傳播信號中包含的給定功率水平,它們更有可能經歷電遷移失敗。當我們觀察用于具有HBM接口的DRAM 3D堆疊的典型TSV的橫截面時,可以確定更容易發生電遷移的位置。

(用于DRAM堆棧的TSV)

一旦制造完成,TSV通常會留下輕微的錐度,其中結構底部的通孔更薄。較薄的區域由于其截面積較小,因此電流密度較大,因此電遷移更有可能首先發生在那里。結果會形成空洞,最終導致開路。一旦空洞開始形成,空洞也會成為應力集中的區域,并可能發生機械斷裂。

#4

工藝優化有助于提高可靠性

在TSV中,電遷移和機械應力之間存在重要的相互作用,這需要工藝優化以確保這些問題得到解決。具有更均勻輪廓的TSV可以防止應力集中,使用阻擋層來防止電遷移,使用高熱退火和拋光來防止泵送,以及保形襯里沉積工藝可以幫助防止TSV中的銅斷裂,污染和擴散。 接下來,給各位推薦一個大型行業技術交流論壇。

審核編輯:劉清

-

pcb

+關注

關注

4322文章

23124瀏覽量

398514 -

DRAM

+關注

關注

40文章

2319瀏覽量

183605 -

HDI

+關注

關注

6文章

200瀏覽量

21320 -

TSV

+關注

關注

4文章

115瀏覽量

81490 -

3D立體堆疊芯片

+關注

關注

0文章

2瀏覽量

4802

原文標題:什么影響TSV的可靠性?

文章出處:【微信號:CEIA電子智造,微信公眾號:CEIA電子智造】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么原因會影響TSV的可靠性呢?

什么原因會影響TSV的可靠性呢?

評論