說到本文內容,可能需要先嘮嘮半導體、微電子和集成電路之間的關系。

半導體產業往往指以半導體材料為基礎的整個產業鏈生態,這里可以包括半導體材料的生產(屬于化學產業),利用半導體材料生產加工的產業,幫助半導體材料生產加工的工具設計及生產產業......是一個非常廣泛的產業鏈體系。

微電子從字面理解來看,就是小型電子產品的設計、生產、制造產業,小到多少呢?一般說來我們認為產品的金屬線條最寬不要超過10um吧(參考最早的晶體管尺寸看)。

集成電路設計產業,重點是“設計”,是隸屬于半導體和微電子產業的一個分支。是利用設計工具,設計一個將不同微小電子器件集合在一個電路,以實現相應功能的過程。微小電子器件,就參考微電子的尺寸吧。而因為現在大部分集成電路設計都是使用半導體材料為硬件載體來實現功能的,所以又隸屬于半導體產業。

多說一句,一個比較容易迷惑的概念就是芯片,我們一般將集成電路產品的成品形態叫做芯片,但還有一種生物芯片的概念,與電路沒有關系,是純生物學反應的一塊chip上面可以檢測出巨大的生物信息,所以叫做芯片。不屬于電子學范疇,更不是半導體產業了。

晶圓怎么來的?

集成電路設計的產品,基于半導體材料實現硬件載體,這里要說的是襯底材料,也就是晶圓最原始的材料,一般說這些材料可以分為元素半導體和化合物半導體,其中元素半導體多見于Ge(鍺)、Si(硅)這些六價元素。而化合物半導體,是合成半導體材料,如GaAs(砷化鎵)、GaN(氮化鎵)、Ga2O3(氧化鎵)、SiC(碳化硅)等。根據不同材料的電氣特性,可以設計不同應用的產品。

- Si元素地球上含量大,具有耐高壓、反向漏電流小、效率高、使用壽命長、可靠性好、熱傳導好,并能在200高溫下運行等優點,所以常被應用在大規模集成電路(VLSI,Very Large Scale Integration Circuits)的基底材料。

- GaAs(砷化鎵),高頻、高溫、低溫性能好,噪聲小、抗輻射能力強,適用于制作轉移器件,適用于高頻場合,如移動電話、衛星通訊、微波點對點連線、雷達系統等。缺點在于有毒,且生產工藝要求較高,與Si相比,不易于規模化生產(Si晶圓有12寸,但純GaAs晶圓主流只有6寸)。

- GaN(氮化鎵)作為砷化鎵的下一代產品,禁帶寬度大,可以有更好的線性度和耐壓性,并提供較大的電流驅動能力,所以現在常被用于快充設備的充電驅動芯片。

以Si晶圓為例,如果想拿到硅晶圓,則首先需要生產硅晶棒(單晶硅硅錠),具體的生產流程不做贅述,簡單說來就是靠高溫融化固體硅材料,然后通過旋轉晶種,使得其他硅晶體按照整齊的格式重新吸附在晶種周圍,越長越大。最后實現硅晶棒,其直徑一般就是4寸、6寸(~100mm)、8寸(~200mm)、12寸(~300mm)等。

之后,需要將硅錠切成厚度均勻的薄片,這就是最原始的單晶硅晶圓。

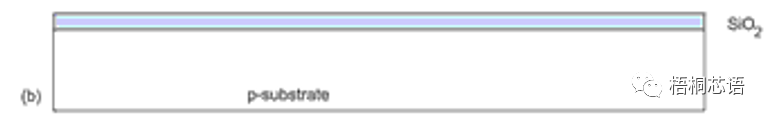

原始的單晶硅晶圓是無法用于生產的,同時由于Si元素無法單獨穩定存在于現實環境中,其表面會形成一層二氧化硅(SiO2),如下面藍色部分。

所以在做生產之前,需要先對單晶硅晶圓進行研磨(把SiO2層去除)、拋光(確保表面光滑,晶格結構整齊)、外延摻雜(外延摻雜三價元素,如硼、鎵等,使得晶圓為p型襯底晶圓)(外延摻雜五價元素,如磷、銻、砷等,使得晶圓為n型襯底晶圓)。如下所示黃色部分:

而外延摻雜后的晶圓內部晶格也會發生一些變化,下圖中(a)是沒有摻雜的單晶硅,(b)是摻雜了砷元素的n型襯底晶圓,(c)是摻雜了硼元素的p型襯底晶圓。一般來說我們主要使用p型襯底晶圓進行生產。

摻雜的工藝很多,比如說電鍍工藝、濺射工藝、蒸發工藝、化學沉淀工藝(CVD)等,襯底外延摻雜一般用的就是CVD工藝了。

當然如果外延摻雜其他元素,如GaAs,之后的晶圓也可以用于GaAs襯底進一步生產使用。

MASK(掩膜板)是什么?

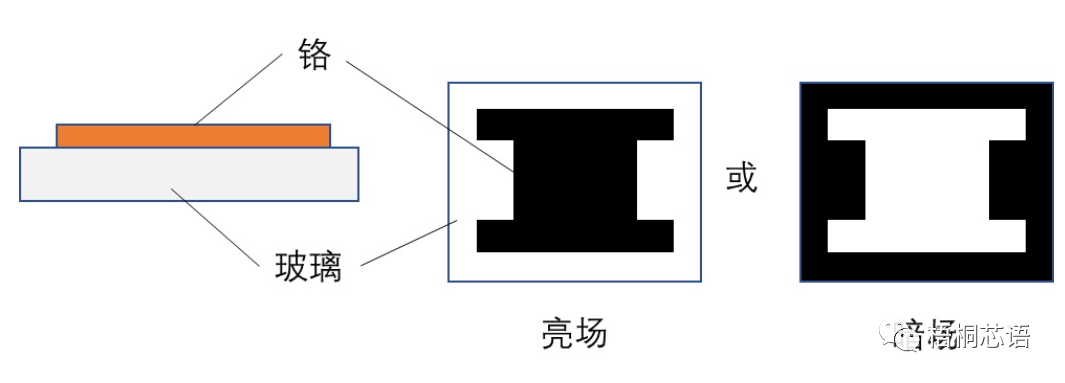

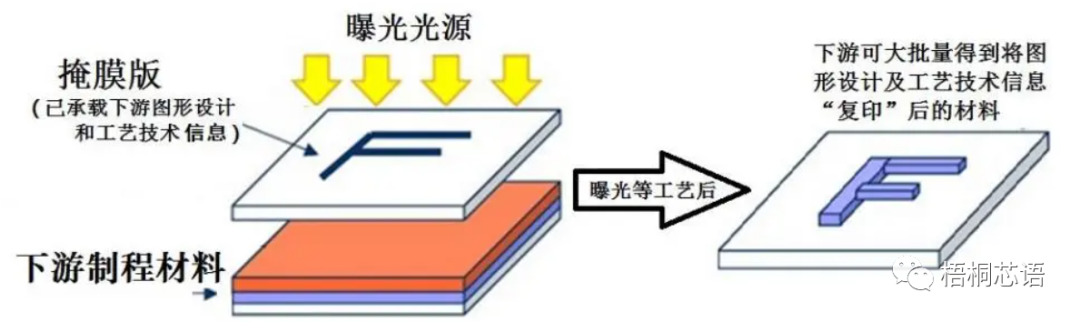

在晶圓上生產芯片的前提,是先做好掩膜板。掩膜板是一種在玻璃(石英板)上利用鉻金屬實現不同圖案的板子。石英板是透光的,而鉻金屬是阻光的,所以根據鉻的形狀,光透過板子,就會在板子另一面顯影出圖形的樣子。(這和照相底片的原理是類似的)

實際在生產的時候還會利用縮圖透鏡縮小尺寸,在晶圓上達到實際芯片的尺寸。

掩膜板是一個大約26mmx32mm的長方形板子,而制造一顆晶圓需要的圖形不止一層掩膜板,根據實際工藝的不同,每個芯片所需的掩膜板數量不同,而因為掩膜板制造工藝屬于高端工藝,價格不菲,因此越是功能復雜,可靠性要求高,功耗和性能同時有要求,那么掩膜板層數也會比較多,NRE成本(28nm工藝一層mask大約為7萬美元)和生產成本也相應提高了。

需要注意的是,一般說來芯片不是非常大,一塊掩膜板上可以同時做多個芯片的圖形。生產時,需要移動掩膜板多次,才能在一張晶圓上完成該層圖形的光刻工作。

*** Photolithography (光刻)是什么?***

通過掩膜板在晶圓上實現光刻,是生產芯片過程中非常重要的動作。每一次光刻都需要做以下步驟的工作:

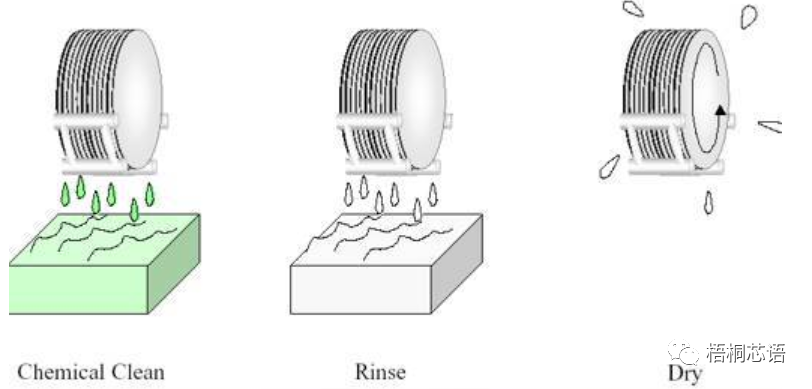

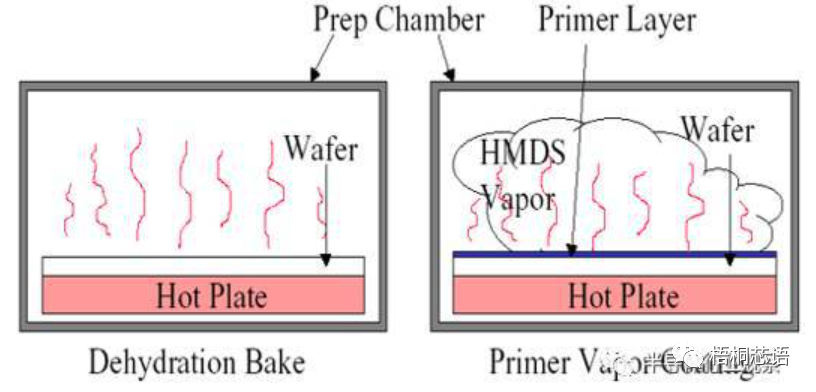

- 表面準備:清洗和烘干表面(清洗硅片的目的是去除污染物去除顆粒、減少針孔和其它缺陷,提高光刻膠黏附性。烘干是為了除去晶圓表面潮氣,增加光刻膠和表面黏附性)

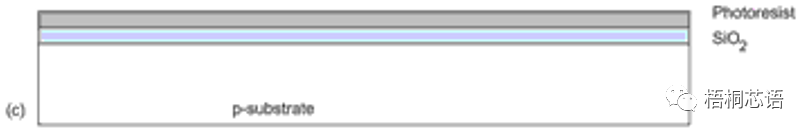

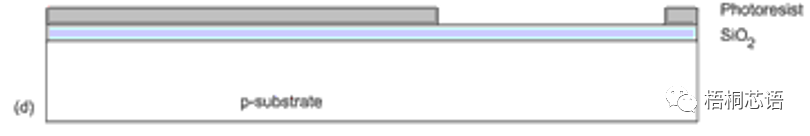

完成以上工作后,晶圓表面干凈整齊,準備涂光刻膠。以晶圓第一層光刻工作為例,由于表面氧化,此時SiO2層是晶圓表面層:

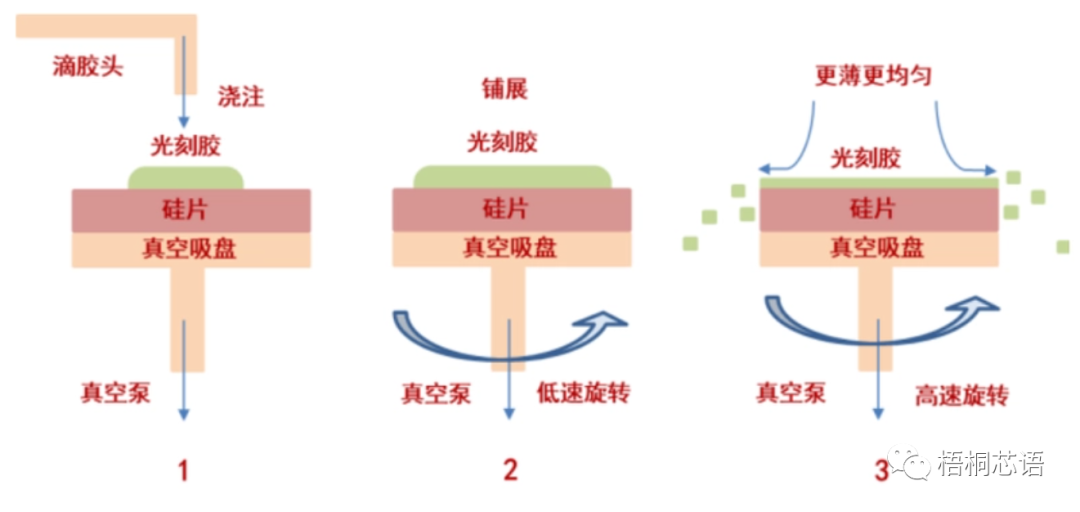

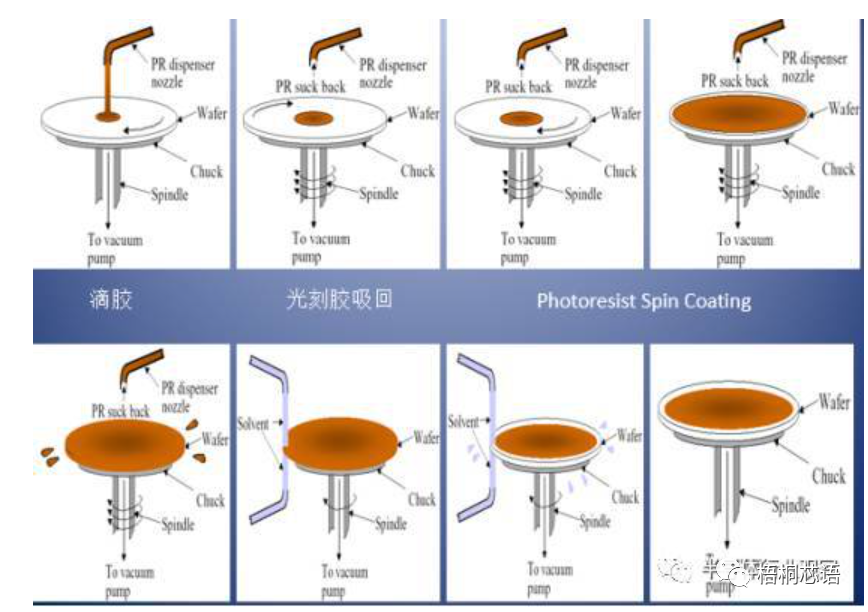

- 涂覆光刻膠:在表面旋轉涂覆一層薄光刻膠膜(光刻膠液體滴在硅片中心,通過旋轉使得光刻膠均勻的鋪在晶圓之上)

在這之后,晶圓上就均勻地覆蓋了一層光刻膠。以晶圓第一層光刻工作為例,在SiO2層之上,均勻地覆蓋了一層光刻膠。

- 前烘:完成光刻膠的涂抹之后,需要進行軟烘干操作,這一步驟也被稱為前烘。前烘能夠蒸發光刻膠中的溶劑溶劑、能使涂覆的光刻膠更薄。

- 對準:光刻對準技術是曝光前一個重要步驟作為光刻的三大核心技術之一,一般要求對準精度為最細線寬尺寸的 1/7---1/10。隨著光刻分辨力的提高 ,對準精度要求也越來越高 ,例如針對 45am線寬尺寸 ,對準精度要求在5am 左右。

- 曝光:使用特定波長的光對覆蓋襯底的光刻膠進行選擇性地照射。光刻膠中的感光劑會發生光化學反應,從而使正光刻膠被照射區域(感光區域)、負光刻膠未被照射的區域(非感光區)化學成分發生變化。這些化學成分發生變化的區域,在下一步的能夠溶解于特定的顯影液中。

- 顯影:去除未聚合的光刻膠。通過在曝光過程結束后加入顯影液,正光刻膠的感光區、負光刻膠的非感光區,會溶解于顯影液中。這一步完成后,光刻膠層中的圖形就可以顯現出來。為了提高分辨率,幾乎每一種光刻膠都有專門的顯影液,以保證高質量的顯影效果:(以晶圓第一層光刻工作為例)

- 堅膜:增加光刻膠溶劑揮發。刻膠顯影完成后,圖形就基本確定,不過還需要使光刻膠的性質更為穩定。硬烘干可以達到這個目的,這一步驟也被稱為堅膜。

- 顯影檢查:檢查表面的對準和缺陷

- 刻蝕:穿過光刻膠膜的開口,去除晶圓頂層薄膜。

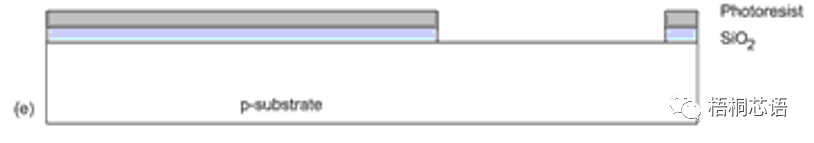

如下以晶圓第一層光刻工作為例,暴露出來的SiO2層,通過刻蝕的方式就被去除掉了。

- 去除光刻膠(剝離):從晶圓上去除光刻膠膜。如下以晶圓第一層光刻工作為例,去掉光刻膠膜后,SiO2層所展示的圖形,就與n-well的MASK圖形一致了。

- 最終檢查:對刻蝕的不規則性和其他問題進行表面檢查

光刻完成后,我們看到光刻膠無法覆蓋的區域,表面裸露在外面,在這個裸露的區域,有2種制造工藝。

向上生長,是利用外延、氧化、蒸發、濺射等方式,在裸露區域的上方逐步增加出一塊材料。

而向內生長,則是在裸露的區域通過液體擴散,或離子注入的方式在裸露區域內部實現材料的晶體結構改變。

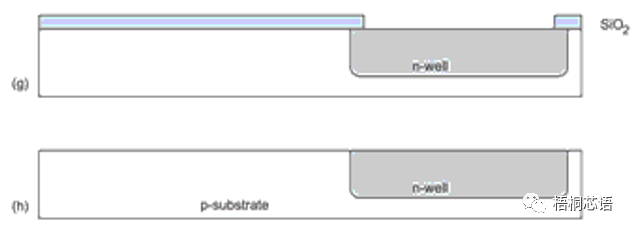

以晶圓第一層光刻工作為例,此時通過離子注入的方式,在SiO2無法覆蓋的部分實現n-well,并移除SiO2,并重新做表面氧化即可進入下一層MASK的光刻工作。

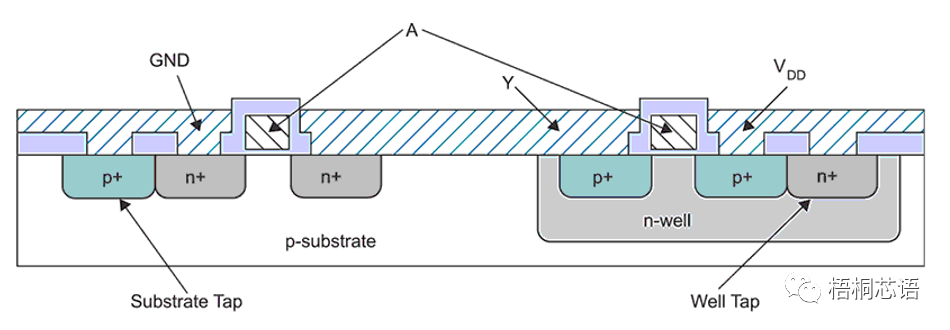

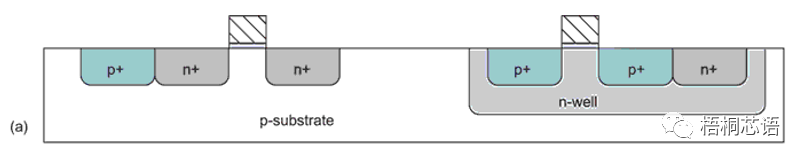

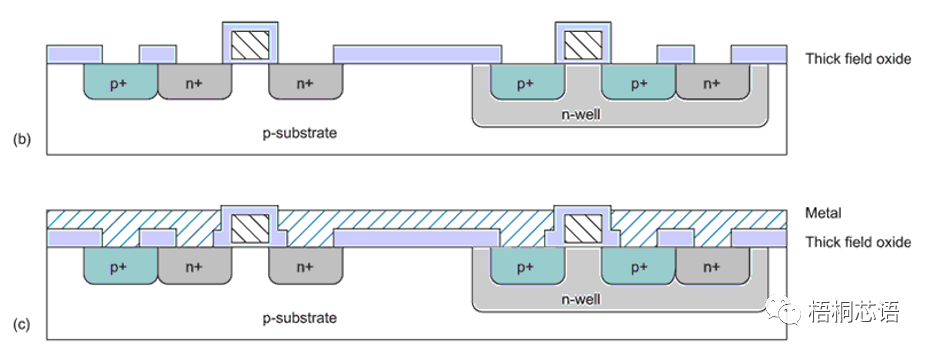

實現一個CMOS反相器

可以看到每一層光刻所需要的步驟是很復雜而且精密的,如果實現一個CMOS反相器電路,那么需要怎么做呢?

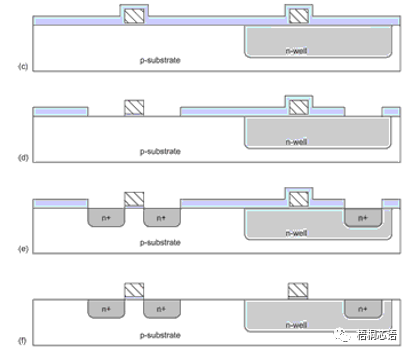

其實第一層n-well的mask圖形刻蝕以及離子注入剛才已經說了,連貫起來就是:

接下來是gate poly的生長(這里不是向內生長,而是向上生長),需要注意的是thin gate oxide層需要在干燥環境里做氧化(干氧化),速度慢,但是精度好把控。

接著是n+的注入(向內生長),在這之前需要先在表面進行SiO2氧化,這個可以采用濕氧化,在潮濕的環境中實現,精度不高,但速度快。

下面通過注入的方式,實現p+圖形。

最后實現metal 1的向上生長。

以上看來,如果希望簡單實現一個CMOS反相器,則需要至少5層MASK(不包含電路連接)。如果2天做3層光刻,則這個電路需要大約4天時間。

不止CMOS

我們常常聽到的都是CMOS集成電路,C是互補的意思(Complementary)。其實CMOS不是全部。

因為電子管的發展延續,實際上我們最早理解的開關過程,是通過PN節開始的。而從電子管向晶體管發展,首先出現的是1947年,威廉·肖克利,(William Shockley)利用鍺元素,實現的第一個雙極性節晶體管(PN節),代表器件包括TTL和ECL等。

1959年貝爾實驗室研制金屬半導體場效應管(MOSFET),并于1960年發布。在20世紀70年代,電路比較簡單,往往都只是純粹的PMOS器件電路,或NMOS器件電路。但隨著生產工藝的提高,利用PMOS和NMOS器件分別在正壓差和負壓差表現的互補性,20世紀80年代后,互補性金屬氧化物電路結構開始盛行,也就是我們所說的CMOS電路。因此CMOS不是器件類型,而是電路結構。

而從生產工藝來說,也有從P阱工藝,到N阱工藝,再到雙阱工藝,接著是三阱工藝,等等的發展,以至于我們可以一次又一次的減小器件尺寸,提高電路穩定性,增加芯片性能的可能。

精度的累計

由于一般的芯片,MASK層數都會在十幾層以上,多的可以到40多層,生產周期不說,成本不計,如果生產時每一層的精度都有1%的誤差,則整個芯片生產出來后就完全不能工作了。

現在的工藝尺寸已經達到5nm以下(金屬寬度預計3nm以下),國內也基本能夠實現22nm的量產了。再往下,幾乎就是對著一個原子大小進行設計和生產了。試想如果發生地震(就算非常輕微的),或者人走過來,我們能不能保證這一個原子跟目標原子的排布與我們的預期一致?

因此,集成電路生產制造工藝是一種非常精密的制造產業,牽扯到光學、化學、物理、機械、工程、電子、數學等大量基礎學科的高精尖產業人才培養和積累。作為國內的集成電路設計半導體產業從業者,我們應該知道路還很長,我們還有差距,但未來仍然是光明的,我們仍然需要努力前行。

-

半導體

+關注

關注

335文章

28032瀏覽量

225603 -

驅動芯片

+關注

關注

13文章

1325瀏覽量

55235 -

CMOS反相器

+關注

關注

0文章

19瀏覽量

6838 -

GaN器件

+關注

關注

1文章

43瀏覽量

7968 -

NMOS管

+關注

關注

2文章

121瀏覽量

5654

發布評論請先 登錄

相關推薦

畢業研究生繼續送資料—微電子學概論、半導體集成電路等

【招聘】集成電路IC設計——摩爾精英

射頻集成電路半導體和CAD技術討論

芯片,集成電路,半導體含義

芯片,半導體,集成電路,傻傻分不清楚?

集成電路與半導體

一文讓你讀懂半導體、微電子和集成電路

半導體,微電子,集成電路都是什么關系?

半導體,微電子,集成電路都是什么關系?

評論