硬件設(shè)計者發(fā)明了許多技術(shù)和工具來實現(xiàn)所需的體系結(jié)構(gòu),以滿足他們的使用需求。就處理器硬件而言,有兩種類型的概念可以實現(xiàn)處理器硬件體系結(jié)構(gòu):一個是RISC,另一個是CISC。

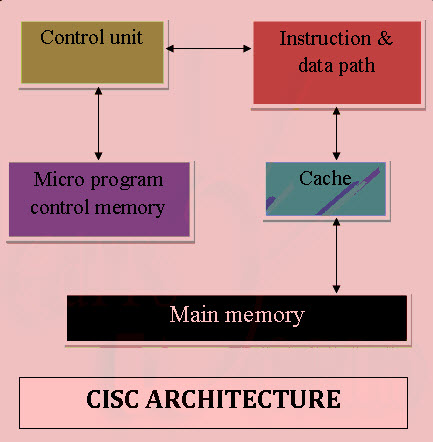

一、什么是CISC架構(gòu)

CISC方法試圖最小化每個程序的指令數(shù)量,從而犧牲每個指令的周期數(shù)量。基于CISC體系結(jié)構(gòu)的計算機旨在降低內(nèi)存成本。因為,大型程序需要更多的存儲空間,因此增加了內(nèi)存成本,并且大型內(nèi)存變得更加昂貴。為了解決這些問題,可以通過將操作數(shù)量嵌入單個指令中來減少每個程序的指令數(shù)量,從而使指令更加復(fù)雜。

1.MUL將存儲器中的兩個值加載到CISC中的單獨寄存器中。

2.CISC通過實現(xiàn)硬件并執(zhí)行操作來使用盡可能少的指令。

3.指令集體系結(jié)構(gòu)是允許程序員與硬件之間進行通信的媒介。數(shù)據(jù)執(zhí)行部分,數(shù)據(jù)的復(fù)制,刪除或編輯是微處理器中使用的用戶命令,并且使用該微處理器操作指令集體系結(jié)構(gòu)。

4.上面的指令集體系結(jié)構(gòu)中使用的主要關(guān)鍵字如下。

指令集:為執(zhí)行程序而給出的一組指令,它們通過操縱數(shù)據(jù)來指導(dǎo)計算機。指令的形式為-操作碼(操作碼)和操作數(shù)。其中,操作碼是應(yīng)用于加載和存儲數(shù)據(jù)等的指令。操作數(shù)是其中應(yīng)用了指令的存儲器寄存器。

尋址模式:尋址模式是訪問數(shù)據(jù)的方式。根據(jù)所應(yīng)用指令的類型,尋址模式可以有多種類型,例如直接模式(訪問直接數(shù)據(jù))或間接模式(訪問數(shù)據(jù)的位置)。具有相同ISA的處理器在組織上可能會非常不同。具有相同ISA和幾乎相同組織的處理器仍然不完全相同。

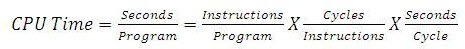

CPU性能由基本定律給出

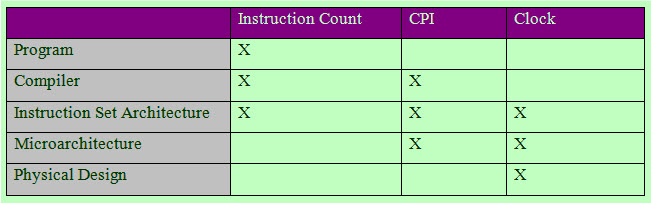

因此,CPU性能取決于指令計數(shù)、CPI(每條指令的周期)和時鐘周期時間。所有這三個都受指令集體系結(jié)構(gòu)的影響。

上圖中,突出了指令集體系結(jié)構(gòu)的重要性。

二、CISC處理器案例

IBM 370/168:于1970年問世。CISC設(shè)計是一個32位處理器和四個64位浮點寄存器。

VAX 11/780:CISC設(shè)計是32位處理器,它支持Digital Digital Corporation提供的許多尋址模式和機器指令。

英特爾80486:于1989年發(fā)布,它是CISC處理器,其指令長度從1到11不等,將有235條指令。

三、CISC體系結(jié)構(gòu)的特征

1.指令解碼邏輯將很復(fù)雜。

2.需要一條指令來支持多種尋址模式。

3.較少的芯片空間足以用于通用寄存器,以直接在存儲器上操作0的指令。

4.各種CISC設(shè)計都為堆棧指針設(shè)置了兩個特殊的寄存器,用于處理中斷等。

5.MUL被稱為“復(fù)雜指令”,需要程序員來存儲功能。

四、CISC體系結(jié)構(gòu)的優(yōu)點

1.微編程是易于實現(xiàn)的匯編語言,并且比硬接線控制單元便宜。

2.對新指令進行微編碼的簡便性使設(shè)計人員可以使CISC機器向上兼容。

3.隨著每條指令變得更加完善,可以使用更少的指令來執(zhí)行給定任務(wù)。

五、CISC體系結(jié)構(gòu)的缺點

1.由于不同指令占用的時鐘時間不同,因此機器的性能會降低

2.即使在現(xiàn)實中有各種專門的指令甚至很少使用,在典型的編程事件中也僅使用現(xiàn)有指令的20%。

3.ISC指令將條件代碼設(shè)置為每條指令的副作用,此設(shè)置需要花費一些時間-并且隨著后續(xù)指令更改條件代碼位-因此,編譯器必須在發(fā)生這種情況之前檢查條件代碼位。

-

CISC

+關(guān)注

關(guān)注

1文章

31瀏覽量

19523 -

RISC

+關(guān)注

關(guān)注

6文章

465瀏覽量

83809

發(fā)布評論請先 登錄

相關(guān)推薦

CISC架構(gòu)的特征及優(yōu)缺點

CISC架構(gòu)的特征及優(yōu)缺點

評論