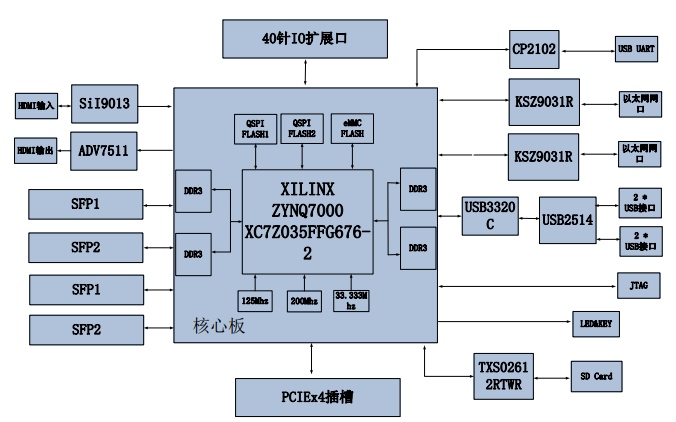

(基于TI KeyStone架構C6000系列TMS320C6657雙核C66x定點/浮點DSP以及Xilinx Zynq-7000系列SoC處理器XC7Z035-2FFG676I設計的異構多核評估板,由核心板與評估底板組成。)

ZYNQ7035PL Cameralink回環例程

1.1.1例程位置

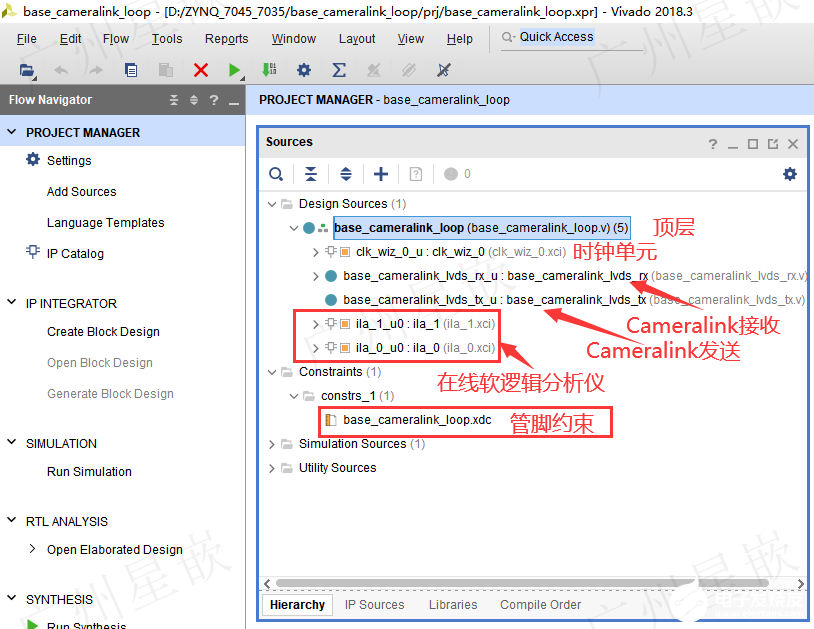

ZYNQ例程保存在資料盤中的DemoZYNQPLbase_cameralink_loopprj文件夾下。

1.1.2功能簡介

Cameralink回環例程將J3、J4當作兩個獨立的BaseCameralink接口使用,一個接收,另一個發送。

Cameralink接收端,利用XilinxISERDESE2原語進行串/并轉換,將LVDS串行數據轉換成28bit的cameralink并行數據。解串后的并行數據通過ila進行在線分析和查看,并實時檢測并行數據是否有誤碼。

Cameralink發送端,利用XilinxOSERDESE2原語進行并/串轉換,將本地28bit cameralink并行數據串行化為LVDS數據發送出去。

1.1.3Cameralink接口時序說明

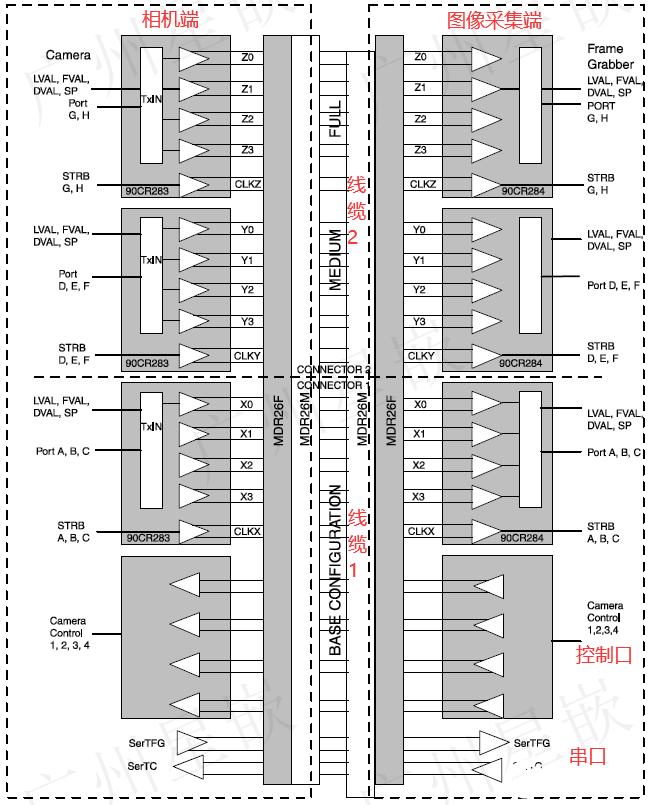

1.1.3.1Cameralink三種配置模式

Base模式:只需一根Cameralink線纜;4對差分數據、1對差分時鐘;

Medium模式:需要兩根Cameralink線纜;8對差分數據、2對差分時鐘;

Full模式:需要兩根Cameralink線纜;12對差分數據、3對差分時鐘。

各種模式下,統一都包含一組控制口和一組串口。控制口有4根信號,用于圖像采集端對相機的IO控制;串口用于圖像采集端對相機參數的配置。

1.1.3.2單路差分數據與時鐘之間時序關系

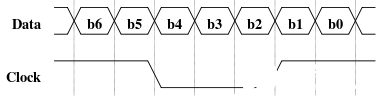

單路Cameralink差分數據與隨路的差分像素時鐘之間的時序關系如下圖所示:

一個時鐘周期內傳輸7bits串行數據,首先傳輸串行數據的最高位,最后傳輸串行數據的最低位。7bits數據起始于像素時鐘高電平的中間位置,即數據的最高位在Clock高電平的中間時刻開始傳輸。

Clock高電平時間比Clock低電平時間多一個bit位。

1.1.3.3通道傳輸數據與圖像數據映射關系

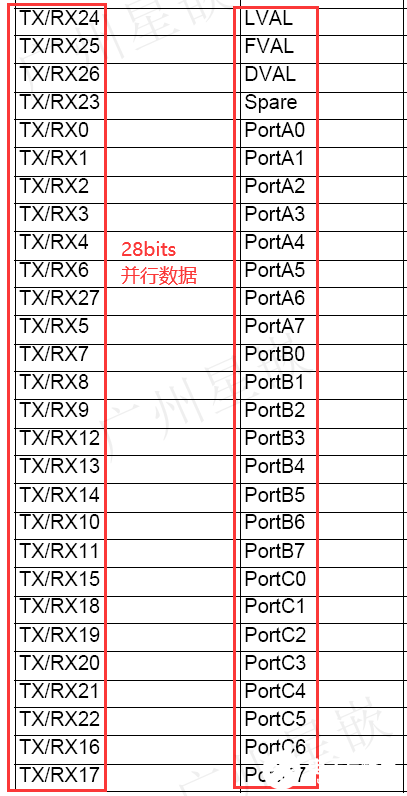

1路差分數據通道上,一個Clock像素時鐘周期傳輸7bits串行數據,那么4路差分數據通道總共就是4*7bits=28bits,我們稱這28bits數據為并行數據,為了方便描述,這28bits數據記為TX/RX27~0。Cameralink Base模式下,這28bits數據與圖像行/場同步/數據有效標記、圖像數據的映射關系如下圖所示:

TX/RX24映射為行同步標記LVAL,TX/RX25映射為場同步標記FVAL,TX/RX26映射為圖像數據有效標記DVAL,TX/RX23未使用,其余位對應圖像數據。

1.1.3.428位并行數據與4路差分數據傳輸通道之間的映射關系

上述28位并行數據是如何通過4路差分數據傳輸通道進行傳輸的呢?28位并行數據映射到4路差分數據傳輸通道各個時刻點的位置關系如下圖所示:

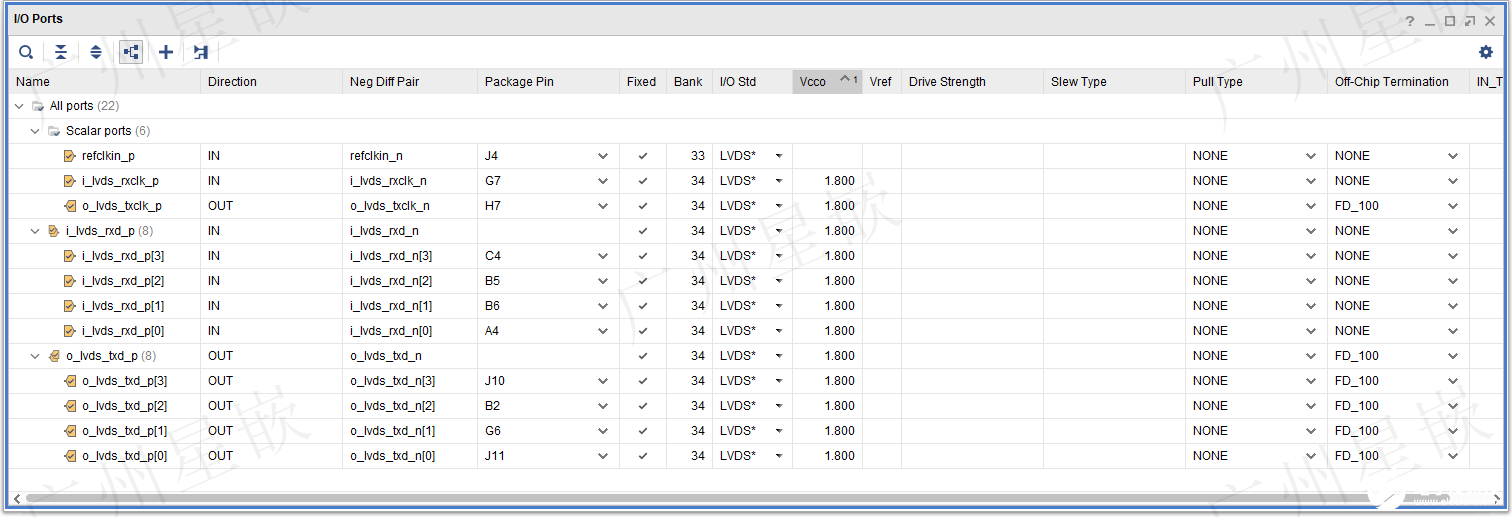

1.1.4管腳約束

ZYNQ PL工程管腳約束如下圖所示:

1.1.5例程使用

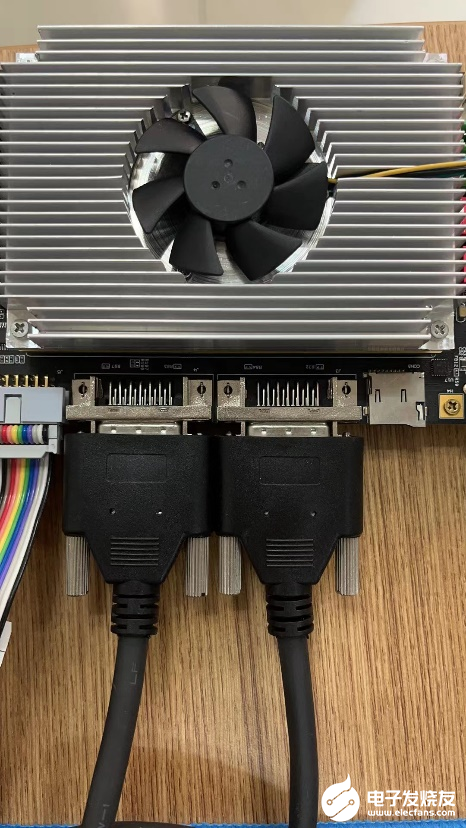

1.1.5.1連接Cameralink線纜

使用Cameralink線纜將J3、J4兩個接口連接在一起:

1.1.5.2加載運行ZYNQ程序

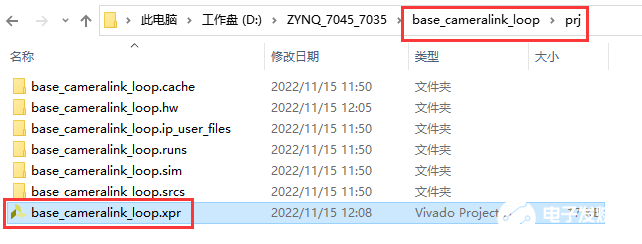

1.1.5.2.1打開Vivado工程

打開Vivado示例工程:

工程打開后界面如下圖所示:

1.1.5.2.2下載ZYNQ PL程序

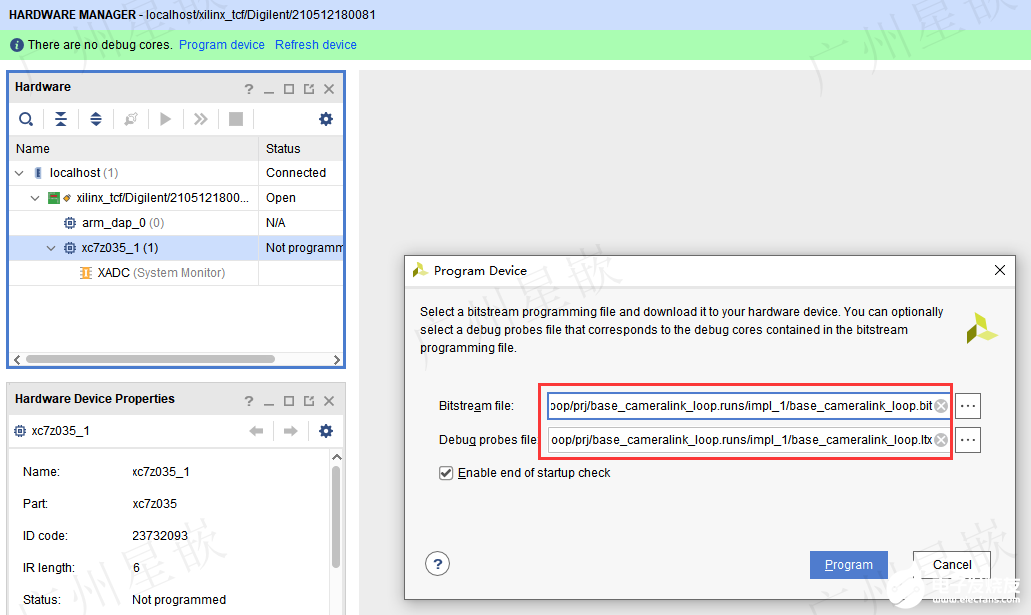

下載bit流文件base_cameralink_loop.bit,并且配套base_cameralink_loop.ltx調試文件,如下圖下載界面所示:

1.1.5.3運行結果說明

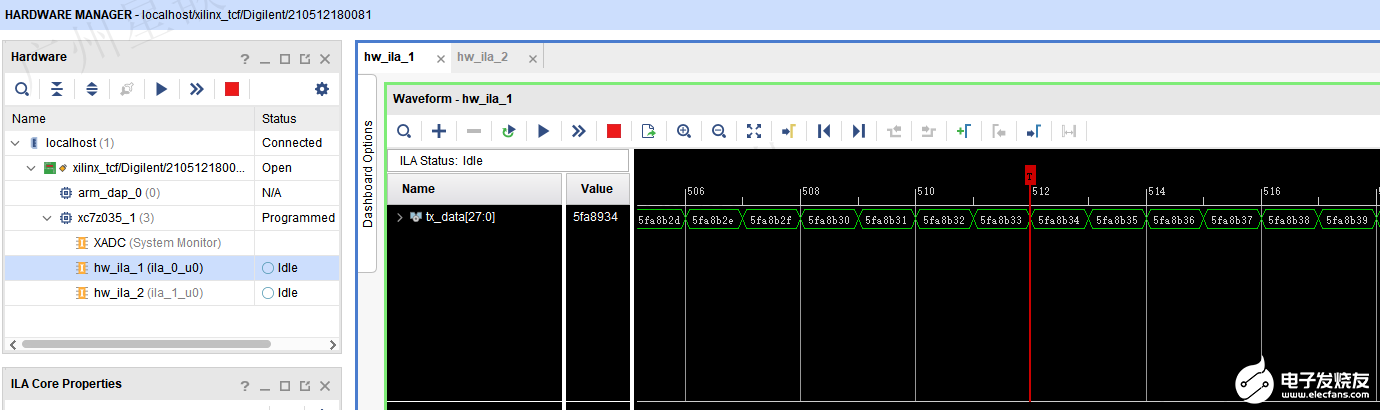

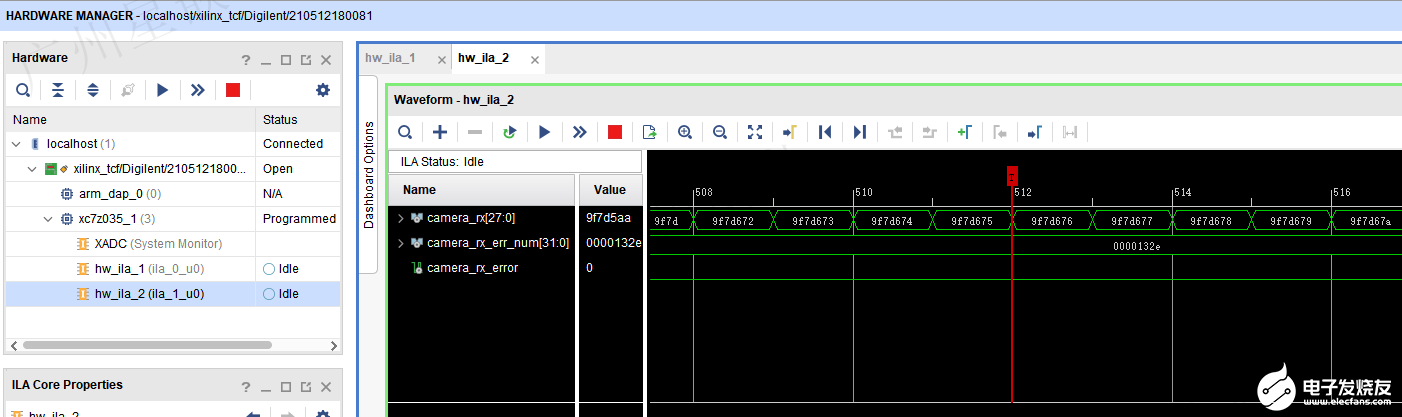

ZYNQ PL端提供的ILA調試窗口,可以實時抓取采集Cameralink并行信號以及錯誤檢測信號的時序波形。

hw_ila_1調試界面抓取Cameralink并行發送數據,是一個28bits的累加數:

hw_ila_2調試界面抓取Cameralink并行接收數據、接收誤碼統計以及接收誤碼實時標識信號,如下圖所示:

cameralink_rx_err_num顯示有數值,則說明Cameralink接收過程中存在誤碼。可能在開始通信初始化期間存在誤碼現象,導致cameralink_rx_err_num誤碼統計累加。待程序下載完畢后,如果Cameralink通信正常的話,cameralink_rx_err_num誤碼統計應該不會再累加。如果cameralink_rx_err_num誤碼統計繼續不斷累加,則通過觸發camera_rx_error信號可以捕捉到誤碼具體發生時刻。

1.1.5.4退出實驗

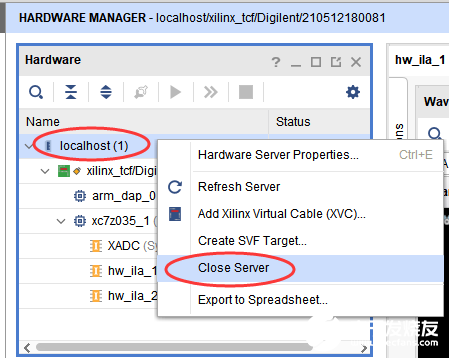

Vivado調試界面HardwareManager窗口,右鍵單擊localhost(1),在彈出的菜單中點擊CloseServer,斷開ZYNQ JTAG仿真器與板卡的連接:

最后,關閉板卡電源,實驗結束。

本文轉載自:星嵌電子

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19404瀏覽量

230880 -

soc

+關注

關注

38文章

4199瀏覽量

218858 -

lvds

+關注

關注

2文章

1045瀏覽量

65958 -

Zynq

+關注

關注

10文章

610瀏覽量

47253

發布評論請先 登錄

相關推薦

[XILINX] 正點原子ZYNQ7035/7045/7100開發板發布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

zynq XC7Z100板卡學習資料:基于zynq XC7Z100 FMC接口通用計算平臺

zynq 7020 PS和zynq PL是如何通話的?

基于ZYNQ的CameraLink圖像采集與邊緣檢測開發詳解

【稀缺資源】基于FPGA的CameraLink OUT視頻案例

【稀缺資源】基于FPGA的CameraLink OUT視頻案例

【稀缺資源】基于FPGA的CameraLink OUT視頻案例

Xilinx Zynq7035算力指標

Xilinx Zynq7035 PL SFP光口通信例程

Xilinx Zynq7035 PL Cameralink回環實現

ZYNQ7000開發平臺的AX7Z035開發板用戶手冊免費下載

ZYNQ7035 PL Cameralink回環例程

ZYNQ7035 PL Cameralink回環例程

評論