什么是同步器

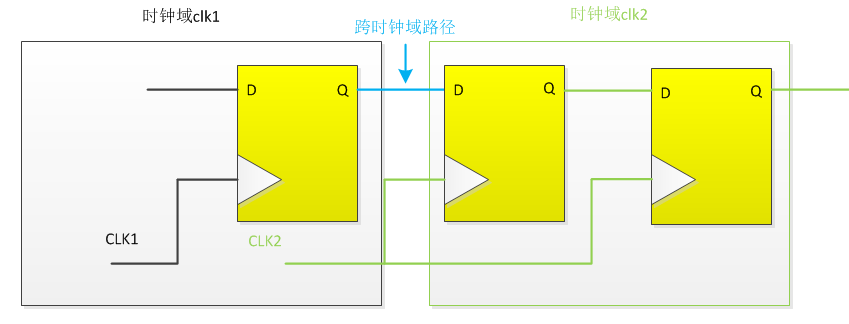

如圖1所示電路結(jié)構(gòu)就叫同步器。左邊為時鐘域clk1,右邊兩個FF為時鐘域clk2,藍色的為CDC(clock domain cross)路徑。這種電路結(jié)構(gòu)常用于兩個不同的時鐘域數(shù)據(jù)傳輸。其實前面講的異步復(fù)位同步釋放本質(zhì)上也是同步器,只是前面的復(fù)位信號是復(fù)位端口產(chǎn)生的,不是某個寄存器打拍過來的,異步復(fù)位信號也可以視作一個不同時鐘域的信號。由此你也可以知道同步器的作用之一就是消除亞穩(wěn)態(tài)。

圖1. 同步器跨時鐘域圖

用更直觀的代碼告訴大家,就是如下verilog代碼:

reg [ 1:0] d1;

reg [ 1:0] ql;

reg [ 1:0] q2;

always@(posedge clk1)

begin

if(rst == 1'b1) d1 <= 2'h0;

else d1 <= din;

end

always@(posedge clk2)

begin

if(rst == 1'b1) ql <= 2'h0;

else q1 <= d1

end

always@(posedge clk2)

begin

if(rst == 1'b1) q2 <= 2'h0;

else q2 <= q1;

end

亞穩(wěn)態(tài)及其傳播

重點!

通過兩級寄存器,即使產(chǎn)生亞穩(wěn)態(tài)也在兩個寄存器之間,降低傳遞到后級的概率,從而減輕亞穩(wěn)態(tài)對后級影響。

理論上,亞穩(wěn)態(tài)產(chǎn)生后持續(xù)時長是隨機的,意味著永遠持續(xù)下去也是可能的,然而由于實際電路中存在的噪聲和能量變化等一定會讓亞穩(wěn)態(tài)很快產(chǎn)生不平衡,迅速向0或者1靠攏。舉個例子,就像筆尖上放一個圓球,理論上可以找一個位置永遠平衡,然而實際上由于一點點的震動都會導(dǎo)致圓球迅速掉下去。如圖2所示,在時鐘發(fā)射沿到來后,亞穩(wěn)態(tài)產(chǎn)生后持續(xù)時間為Tmet,在捕獲沿到來時,dout的亞穩(wěn)態(tài)已經(jīng)消除,這樣亞穩(wěn)態(tài)就不會往后級傳播,也就是說亞穩(wěn)態(tài)在一個時鐘周期內(nèi)穩(wěn)定就可以防止往下一級傳播。實際中亞穩(wěn)態(tài)的穩(wěn)定都很快。而同步器打2拍就是為了在時鐘頻率很高的時候,捕獲沿采到亞穩(wěn)態(tài)向下一級傳播的時候,還有一級寄存器隔離,然亞穩(wěn)態(tài)在一個時鐘周期內(nèi)穩(wěn)定下來。

假設(shè),亞穩(wěn)態(tài)在一個時鐘周期內(nèi)穩(wěn)定不下來的概率為P,0

圖2. 亞穩(wěn)態(tài)產(chǎn)生過程

同步器同步n bit數(shù)據(jù)

當(dāng)n=1時,參見上面的亞穩(wěn)態(tài)傳播,1bit數(shù)據(jù)產(chǎn)生亞穩(wěn)態(tài)以后就算錯了也是變成0或者1第二拍也會正確,所以同步1bit數(shù)據(jù)可以采后面幾拍的數(shù)據(jù),這樣就能保證采集過來的數(shù)據(jù)是正確的,后面會試驗給大家看。當(dāng)然,要實現(xiàn)這點首先是快時鐘必須是慢時鐘的好幾倍才行,至少2倍。

多bit數(shù)據(jù)傳輸和1bit數(shù)據(jù)唯一的區(qū)別就是多路對齊,保證每一路數(shù)據(jù)延遲一致 ,這樣就和傳輸1bit數(shù)據(jù)一樣了。下面給大家推薦一個約束set_bus_skew,可以約束一條總線上每根線的延遲相差不大。

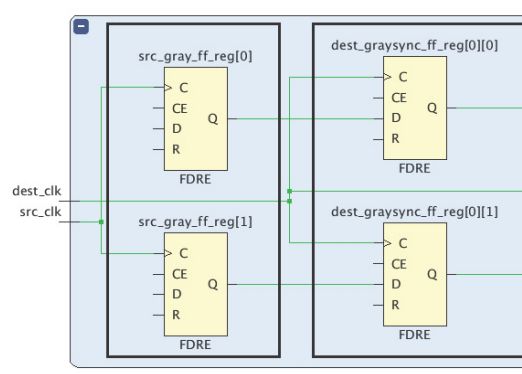

命令用法——set_bus_skew [-from 寄存器名] [-to 寄存器名] xx ns。比如在圖3中約束src_gray_ff_reg到dest_graysync_ff_reg之間的兩根線延遲保持一致,完整命令如下,保證兩根線延遲都在2.5ns,一個快時鐘域周期:

set_bus_skew -from [get_cells src_gray_ff_reg[ ]] -to [get_cells {dest_graysync_ff_reg[0][ ]}] 2.500

圖3. 寄存器圖

同步器傳輸數(shù)據(jù)的情景分析

情景1

同步器只能正確處理同源的兩個時鐘域之間的信號,如果不同源,很可能出現(xiàn)發(fā)射沿打出的數(shù)據(jù)還沒穩(wěn)定就被捕獲沿采集到,這樣數(shù)據(jù)就會出錯。

情景2

兩個時鐘域的頻率不能太接近,且快時鐘最好是慢時鐘的整數(shù)倍,這樣保證邊沿不會出現(xiàn)捕獲沿不在數(shù)據(jù)不穩(wěn)定的時候出現(xiàn),不然會采錯數(shù)據(jù)。

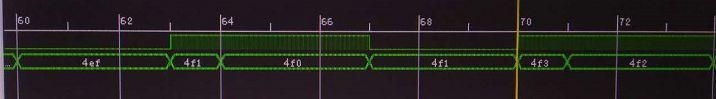

下圖是100M和96.34M時鐘用同步器采集的結(jié)果,err和err1為高電平都是代表數(shù)據(jù)有錯的時候。可以發(fā)現(xiàn)數(shù)據(jù)出錯頻繁,而且間隔不均等,本質(zhì)上就是因為兩個時鐘的相位關(guān)系不是像整數(shù)倍一樣規(guī)律,很可能出現(xiàn)捕獲沿采集不穩(wěn)定數(shù)據(jù)。其實小數(shù)倍的時候,小數(shù)位數(shù)越多越容易出現(xiàn)這種問題。

圖4. 時鐘頻率不匹配導(dǎo)致錯誤

情景3

快時鐘最好是慢時鐘的整數(shù)倍的時候,不加約束也可以有方法比較穩(wěn)定的正確抓取數(shù)據(jù) 。

下圖是50M時鐘到200M時鐘跨時鐘域同步的結(jié)果,沒有加約束,大家可以看到數(shù)據(jù)在從0x4ef到0x4f0過度的時候第一拍出錯了,出現(xiàn)了1個0x4f1,而后面的三拍數(shù)據(jù)是對的,看后面出錯的數(shù)據(jù)也是這樣,也就是說,每采集到的4個數(shù)里面,用出現(xiàn)次數(shù)多的數(shù)覆蓋次數(shù)少的數(shù)就可以了,因為原本是4倍關(guān)系,所以理論上連續(xù)的4個數(shù)是要一致的。

如下圖在兩個位置的總線都加了set_bus_skew約束5ns后,采集的數(shù)據(jù)一直沒有出錯,也根本不用覆蓋的方法去剔除錯誤數(shù)據(jù)了。

正確傳輸條件總結(jié):

- 只能慢時鐘到快時鐘

- 兩時鐘域必須同源

- 兩時鐘最好是整數(shù)倍關(guān)系,否則正確與否只能隨緣

- (可選)滿足以上3點情況下,添加set_bus_skew可以保證每次采樣都正確

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

120939 -

CDC

+關(guān)注

關(guān)注

0文章

57瀏覽量

17838 -

同步器

+關(guān)注

關(guān)注

1文章

98瀏覽量

14673 -

時鐘域

+關(guān)注

關(guān)注

0文章

52瀏覽量

9552

發(fā)布評論請先 登錄

相關(guān)推薦

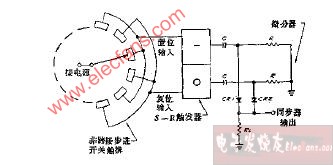

同步器原理電路

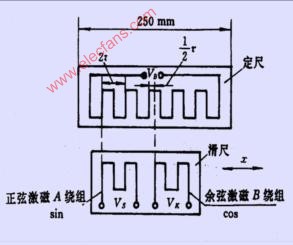

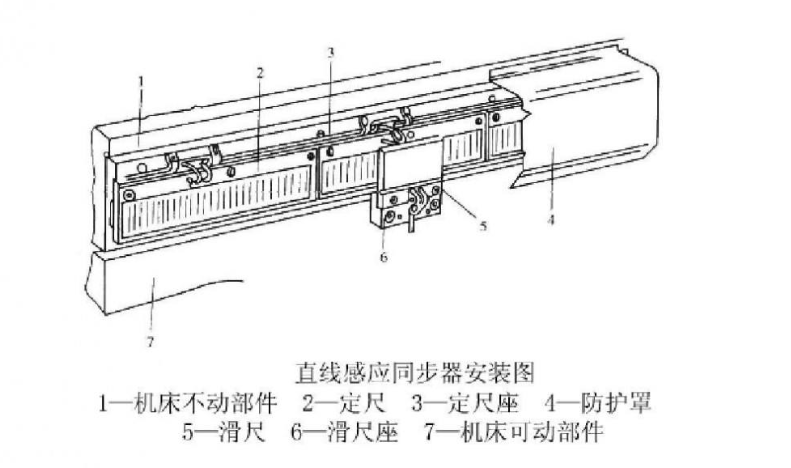

感應(yīng)同步器介紹

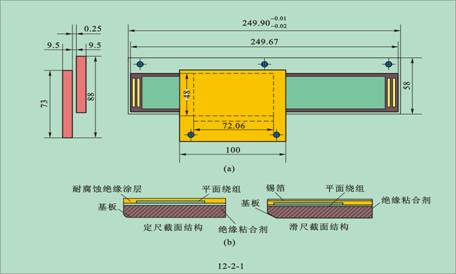

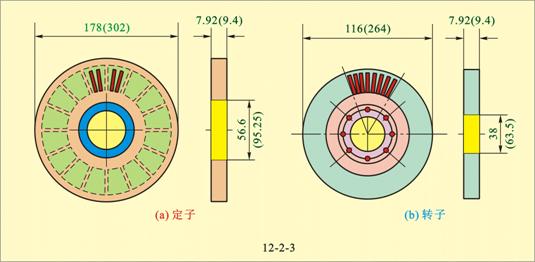

什么是感應(yīng)同步器?感應(yīng)同步器的結(jié)構(gòu)特點

感應(yīng)同步器的工作原理,感應(yīng)同步器的應(yīng)用

感應(yīng)同步器,什么是感應(yīng)同步器

感應(yīng)同步器的基本結(jié)構(gòu)

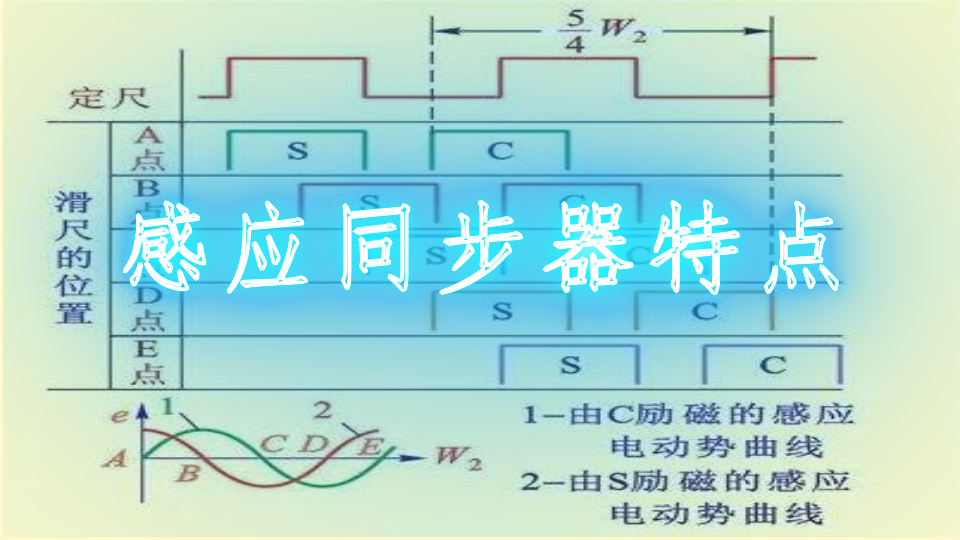

感應(yīng)同步器的工作原理

感應(yīng)同步器的應(yīng)用

同步器的作用

感應(yīng)同步器特點

感應(yīng)同步器的組成和特點

變速器同步器的作用及工作原理?

解讀同步器構(gòu)造及工作原理?

什么是同步器?同步器傳輸數(shù)據(jù)的情景分析

什么是同步器?同步器傳輸數(shù)據(jù)的情景分析

評論