大多數低功耗設計手法在嚴格意義上說并不是由后端控制的,Clock Gating也不例外。在一顆芯片中,絕大多數的Clock Gating都是前端設計者或者EDA綜合工具自動加上去的,后端只有在極端例外的情況下才會動到它們。

盡管如此,Clock Gating的影響與后端息息相關,甚至會引起后端的一些問題,因此我們有必要從頭理解一下它的原理。

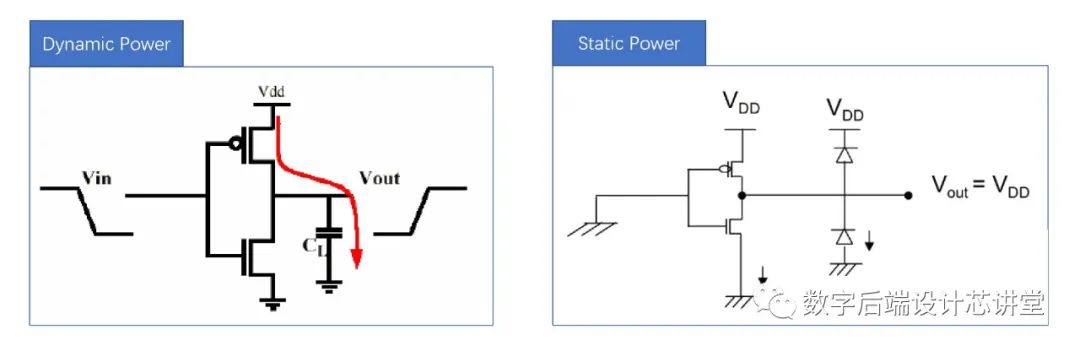

芯片功耗從原理上區分主要有兩大類:靜態功耗(Static Power)和動態功耗(Dynamic Power)。二者的形成原因如下:

所謂動態功耗,主要是由于信號的翻轉從而導致器件內部的寄生RC充放電引起的,而靜態功耗則是由器件在通電狀態下的泄漏電流(Leakage Current)引起的。對此,為了節約動態功耗,最初有個十分簡單的想法:在芯片實際工作過程中,有些信號或者功能并不需要一直處于活動狀態,那么就可以在它們不用的時候將其時鐘信號關閉。這樣一來時鐘信號不再翻轉,從而能夠有效減少動態功耗,而控制時鐘信號開關的就是Clock Gating。

那么Clock Gating是如何被加入到design中的呢?它主要有兩種來源:設計者從RTL階段加入或者由綜合工具自動加入。

下面的例子介紹了在RTL階段加入Clock Gating的方法:

可以看到在加入Clock Gating之后,DFF的clock信號前多了一個使能端EN,從而可以控制該時鐘信號的打開與關閉。

除此之外,在綜合階段,EDA工具同樣支持自動插入Clock Gating。以Synopsys公司的Design Compiler工具為例,簡單的插入Clock Gating的方法如下:

Clock Gating在后端會引起一些問題,尤其在Setup Timing以及時鐘樹綜合階段,有時候會需要做一些特殊的處理。關于為何Clock Gating容易引起setup timing 的問題,請參考歷史文章:

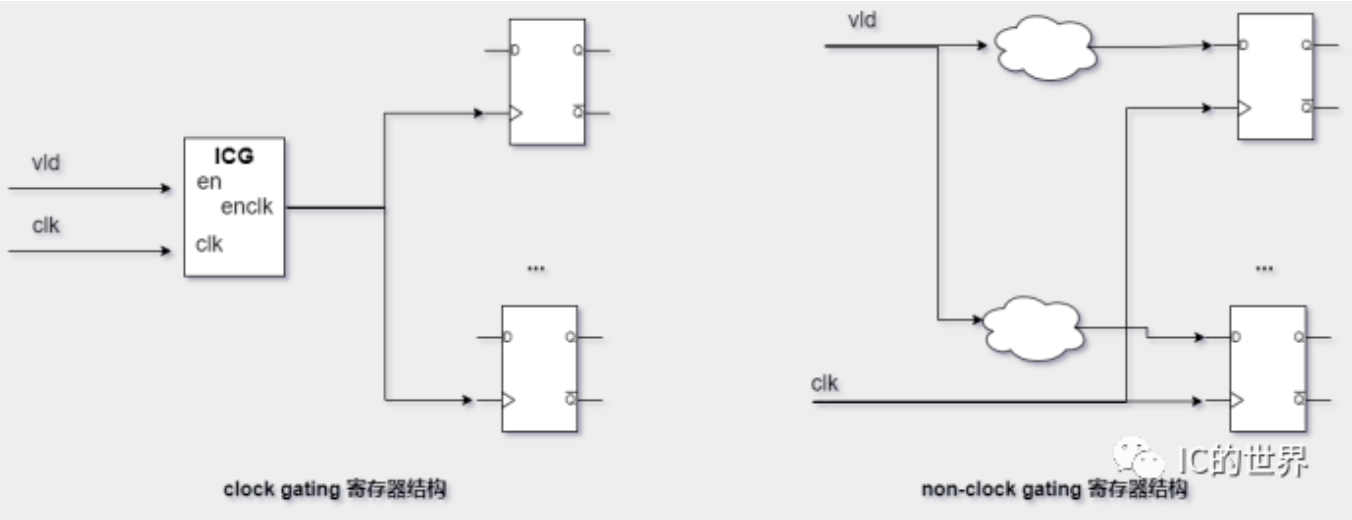

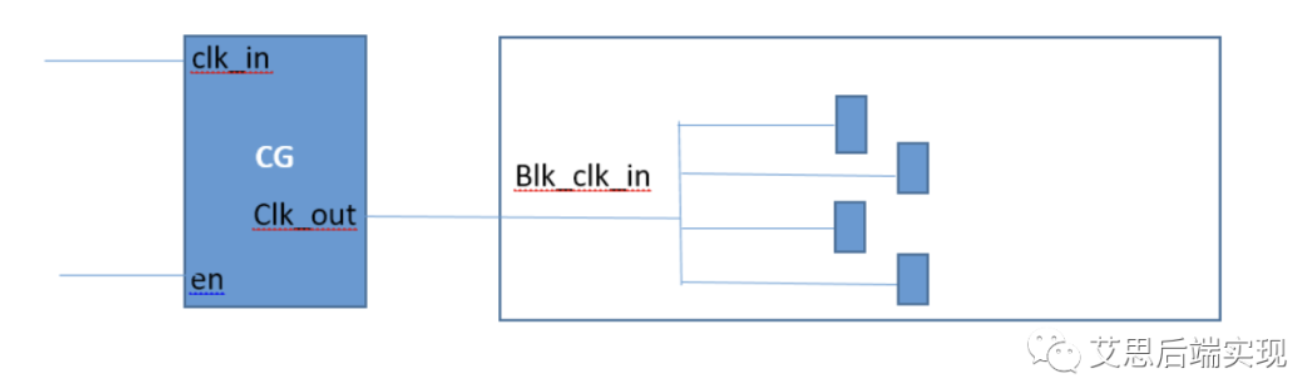

為了盡量避免ICG的setup timing,解決辦法之一是將ICG放在距離register(sink)盡量近的地方:

當然,EDA工具也提供了一些優化方法以便在早期發現和解決ICG的問題,這些技巧希望大家在實踐中多多嘗試和挖掘。

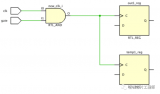

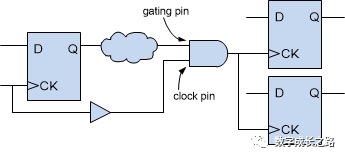

編輯根據作者在DC中做了一下實驗,帶ICG的DFF如下所示:

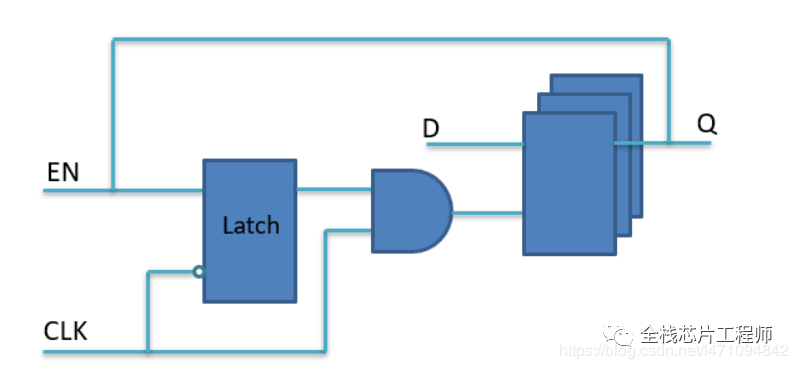

ICG的結構如下所示:

需要注意的是,只有當寄存器的位寬達到一定大小時,DC才會自動將其使能端綜合為ICG單元(經過測試,3個及3個以上的位寬會綜合為ICG單元)。

事實上,由于ICG單元本身帶來了 面積占用 ,只有當寄存器位寬達到一定的大小時,使用ICG才能達到即降低面積又降低功耗的效果,這是在我們今后的使用中需要注意的地方。

-

寄存器

+關注

關注

31文章

5363瀏覽量

120945 -

EDA工具

+關注

關注

4文章

268瀏覽量

31891 -

RTL

+關注

關注

1文章

385瀏覽量

59911 -

低功耗設計

+關注

關注

0文章

80瀏覽量

16188 -

dff

+關注

關注

0文章

26瀏覽量

3430

發布評論請先 登錄

相關推薦

降低電路漏電功耗的低功耗設計方法

RTL實例化的clock gating cell淺見

主要演示BL702/704/706系列mcu低功耗性能

一文搞懂BL開發板系列MCU低功耗性能

基于SCM算法為CPU電壓調節設計研究

什么是門控時鐘 門控時鐘降低功耗的原理

ASIC的clock gating在FPGA里面實現是什么結果呢?

低功耗設計基礎:Clock Gating

低功耗設計基礎:Clock Gating

評論