《基于“礦板”低成本學習Zynq系列》之四-第一個工程HelloWorld一下 (qq.com)

一.前言

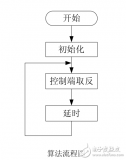

前面我們了解了板子的原理圖和資源,進行了基本的狀態確認,現在我們來搭建開發環境創建HelloWorld工程,打印HelloWolrd來演示開發過程。

二.硬件工程

2.1創建工程

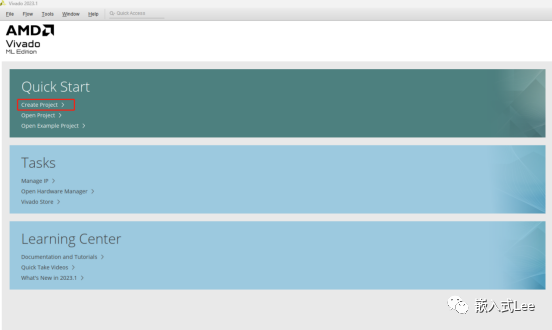

打開vivado

Create Project

Next

指定工程名,路徑,Next

指定RTL工程不添加源碼,Next

搜xc7z010選擇xc7z010clg400-1,next

完成

2.2創建處理器IP

Create Block Design

指定名字xc7z010,OK

點擊空白處的+號

搜索zynq,雙擊ZYNQ7處理器系統

點擊Run Block Automation

點擊OK

雙擊如下框圖

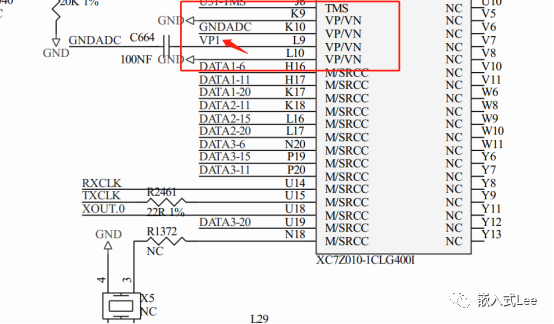

2.2.1配置串口引腳

從原理圖和絲印可以看到

TXD對應A.16 RXD對應F.15

進入以下地址https://www.xilinx.com/support/package-pinout-files.html

選擇zynq 7000

選擇xcz010 CLG400封裝

分別搜索F15 A16

找到分別對應MIO25和MIO24

所以這里選擇UART1對應MIO24和MIO25,勾選UART1

配置波特率為115200

2.2.2配置DDR

2.2.3時鐘配置

時鐘源和原理圖對應為33.33MHz

DDR和CPU時鐘默認

刪除其他未用的配置

2.2.4驗證設計

點擊如下圖標

2.3輸出HDL

點擊Sources選擇剛創建測設計,右鍵點擊->Generate Output Products

默認配置點擊Generate

再次右鍵點擊設計->Create HDL Wrapper

2.4生成bit文件

默認配置即可

2.5導出硬件

File->Export->Export Hard ware

導出的是xsa文件

三.軟件工程

3.1啟動Vitis

Tools->Launch Vitis IDE

3.2創建Vitis工程

在原硬件工程下創建sdk目錄

選擇該目錄 launch

3.3創建平臺工程

指定工程名Next

選擇之前生成的xsa文件打開

選擇不跑系統即standalone,使用core0

生成工程如下

3.4編譯平臺工程

當前平臺工程是out of date,右鍵點擊->Build Project

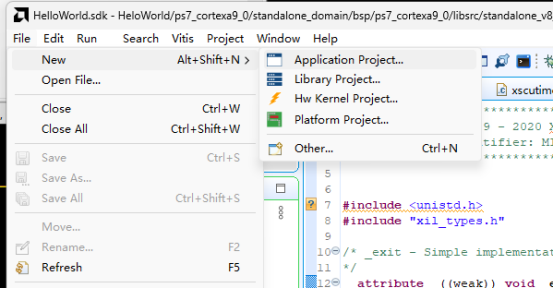

3.5創建應用工程

File->New->Application Project...

Next

默認選擇剛才創建的平臺

指定工程名,其他默認即可

選擇HelloWorld的Demo

3.6編譯應用

右鍵點擊HelloWorld_system工程Build Project

3.7仿真

選擇工程,點擊甲殼蟲旁邊的三角形,Debug Configurations...

雙擊Single Application Debug

由于默認是NAND啟動,可能提示DONE不為高,這里PL端沒用,所以Target下先不勾選編程FPGA,點擊Debug,后面再說明如何修改啟動模式。

右下角看到下載進度

斷點停在了main函數

點擊如下圖標運行

打印如下

四.總結

以上創建了硬件工程和軟件的HelloWolrdDemo,成功的打印了信息,說明板子環境都是OK的可以作為開發板使用。后面就可愉快的學習之旅了。

審核編輯:湯梓紅

-

原理圖

+關注

關注

1300文章

6356瀏覽量

234816 -

開發環境

+關注

關注

1文章

229瀏覽量

16672 -

Zynq

+關注

關注

10文章

610瀏覽量

47242

發布評論請先 登錄

相關推薦

玩轉Zynq連載28——[ex50] 第一個Zynq系統工程“Hello Zynq”

Niobe第一個應用程序

Niobe第一個應用程序

低成本 MiniZed Zynq SoC 開發板

Proteus的第一個工程

《基于“礦板”低成本學習Zynq系列》之四-第一個工程HelloWorld一下

《基于“礦板”低成本學習Zynq系列》之四-第一個工程HelloWorld一下

評論