日前Intel發(fā)布消息稱該公司將在2021年至2024年期間陸續(xù)投產(chǎn)7nm、4nm、3nm、20A、18A等五代工藝節(jié)點(diǎn)。眾所周知臺(tái)積電在芯片制造和代加工方面擁有很強(qiáng)的實(shí)力,而如果此次Intel的20A和18A真的能夠邁入將邁入埃米時(shí)代,將有可能實(shí)現(xiàn)反超。

Intel將于6月11日至16日舉辦的VLSI Symposium 2023研討會(huì)上,首次展示PowerVia技術(shù)。有關(guān)信息顯示,Intel的20A工藝將引入PowerVia背部供電和RibbonFET全環(huán)繞柵極晶體管等全新技術(shù)。

這種技術(shù)可以大大降低供電噪聲和電阻損耗,優(yōu)化供電分布,提高整體能效。而RibbonFET技術(shù)則可以提高晶體管的性能,從而提高芯片的整體性能。通過PowerVia技術(shù),Intel將把傳統(tǒng)位于芯片正面的供電層轉(zhuǎn)移到芯片背面,并通過一系列TSV硅穿孔為芯片供電。

但是展示的并不是20A工藝,而是基于Intel 4工藝的一顆測(cè)試芯片,架構(gòu)為E核心。這顆核心的面積僅為2.9平方毫米,得益于PowerVia技術(shù),大部分區(qū)域的標(biāo)準(zhǔn)單元利用率都超過了90%。同時(shí),PowerVia技術(shù)還帶來了超過5%的頻率提升,吞吐時(shí)間略高但可以接受,功耗發(fā)熱情況符合預(yù)期。

Intel還將為客戶代工使用PowerVia技術(shù)。Intel一直在積極推進(jìn)新一代工藝節(jié)點(diǎn)的研發(fā)和投產(chǎn),而PowerVia技術(shù)的引入為芯片的供電層提供了全新的解決方案,為未來的ERP芯片性能提供更多的可能性。

以上轉(zhuǎn)載自互聯(lián)網(wǎng),版權(quán)歸原創(chuàng)所有

-

芯片

+關(guān)注

關(guān)注

456文章

51140瀏覽量

426147 -

intel

+關(guān)注

關(guān)注

19文章

3483瀏覽量

186284

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

2025年半導(dǎo)體行業(yè)競(jìng)爭(zhēng)白熱化:2nm制程工藝成焦點(diǎn)

臺(tái)積電2nm工藝將量產(chǎn),蘋果iPhone成首批受益者

臺(tái)積電分享 2nm 工藝深入細(xì)節(jié):功耗降低 35% 或性能提升15%!

蘋果iPhone 17或沿用3nm技術(shù),2nm得等到2026年了!

聯(lián)發(fā)科攜手臺(tái)積電、新思科技邁向2nm芯片時(shí)代

臺(tái)積電2nm芯片助力 蘋果把大招留給了iPhone18

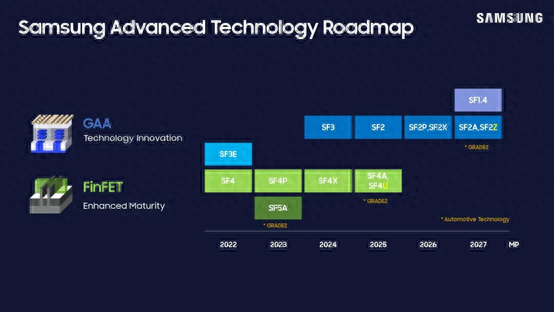

三星公布最新工藝路線圖

Intel推出全新工藝節(jié)點(diǎn),或?qū)⑦~入2nm時(shí)代

Intel推出全新工藝節(jié)點(diǎn),或?qū)⑦~入2nm時(shí)代

評(píng)論