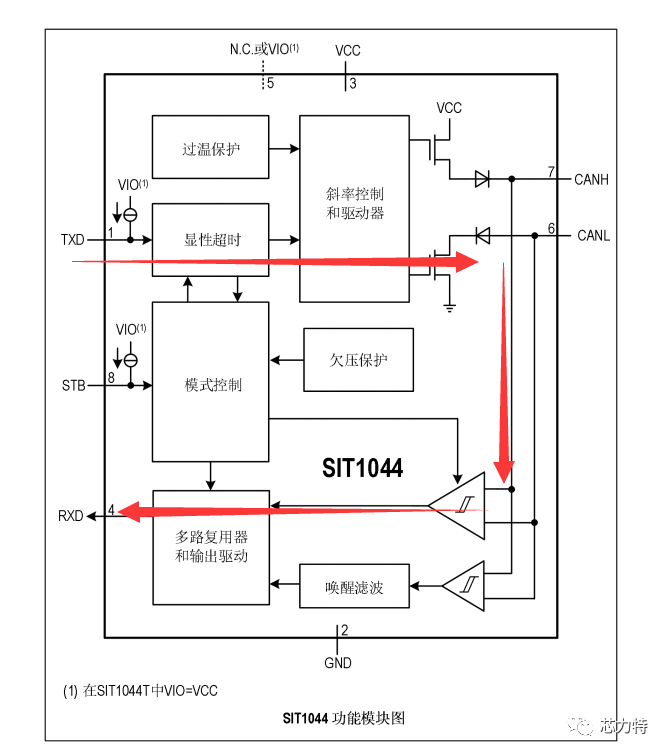

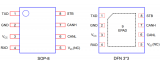

芯力特自主研發的SIT1044芯片是一款應用于CAN協議控制器和物理總線之間的高性能CAN FD收發器芯片,可應用于卡車、公交、小汽車、工業控制等領域,總線耐壓達到±40V,支持5Mbps CAN FD靈活數據速率,具有在總線與CAN協議控制器之間進行差分信號傳輸的能力。

環路延時是指從TXD輸入的數字信號被轉換成相應的模擬總線信號,同時總線收發器監控總線,將模擬總線信號轉換成相應的數字信號從RXD輸出的過程,如下圖所示:

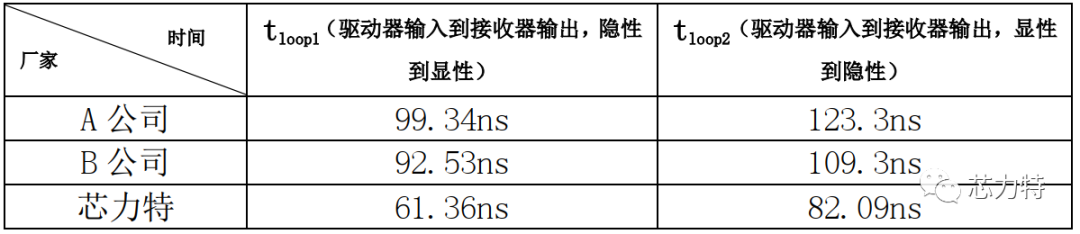

對比目前市面上幾家進口公司的同類芯片的環路延時數據,如下表所示:(以下數據在相同環境下測試)

由以上實測測試數據可得知,芯力特公司SIT1044的實測環路延時時間要小于A公司和B公司同類產品。

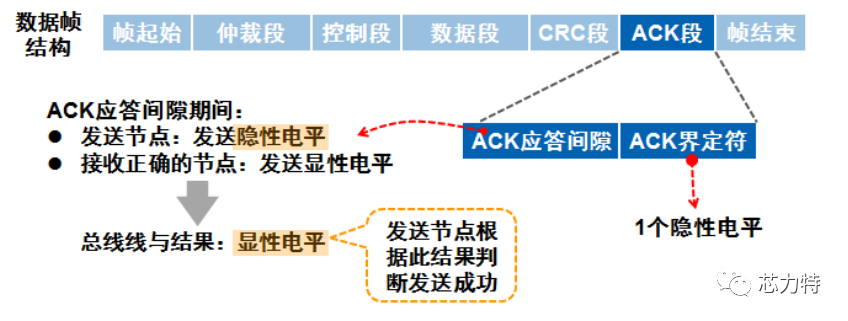

更低的環路延時時間在實際應用時可以使通信距離變長。下面我們以1Mbps波特率下的應用為例,對CAN總線信號延時做簡要分析。以標準數據幀為例,從結構上看分成7段,分別為起始段、仲裁段、控制段、數據段、CRC校驗段、ACK應答段、幀結束,如下圖所示:

ACK段長度為2個位,包含應答間隙(ACK SLOT)和應答界定符(ACK DELIMITER)。在應答場里,發送站發送兩個“隱性”位。當接收器正確地接收到有效的報文,接收器就會在應答間隙(ACK SLOT)期間(發送ACK信號)向發送器發送一“顯性”的位以示應答。發送節點檢測到總線呈顯性狀態時,就認為有節點進行了有效地應答并且自己所發出的幀是正常的。

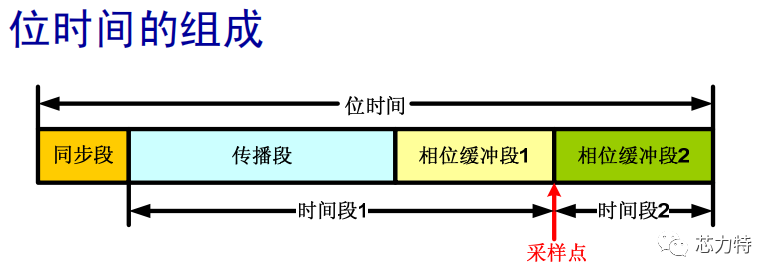

CAN網絡通信位定時參數如下圖:

CAN總線通信中每一位的時間由4部分組成,即同步段、傳播段、相位緩沖段1、相位緩沖段2,劃分為3段。

同步段:用于總線諸節點之間的同步;

時間段1:由傳播段與相位緩沖段1組成,傳播段用于補償信號的物理傳播延時;

時間段2:即相位緩沖段2,相位緩沖段1和相位緩沖段2用于補償沿的相位誤差。

在時間控制器設計中,通過調整時間段1、時間段2的值可以改變對總線傳播延時的補償時間。

發送節點在發完CRC場后,會發出一位應答間隙(ACK SLOT),在這一位的時間內,接收節點應該輸出顯性位作為回應,發送節點如果在應答間隙內沒有檢測到有效的顯性位,則會判定總線錯誤,所以限制CAN總線系統信號傳播延時上限的根本條件就是必須確保發送節點在應答間隙內接收到有效的應答信號。

為滿足這一根本條件,以1Mbit/S,單點采樣模式為例,依據采樣點在設置同步段、時間段1、時間段2內的前后變化,當設置為75%位寬度時(即采樣點位于距位起始的75%位寬度,為750ns),在應答間隙要使得發送節點采集到有效的顯性位,理論上來講,必須滿足整個信號傳播延時小于750ns。即隔離期間、總線驅動器、線纜等的延時綜合小于750ns才能保證應答有效。

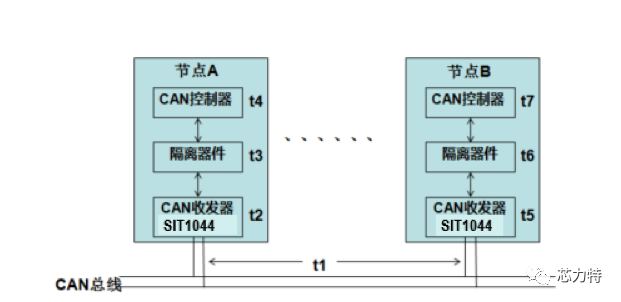

對于CAN網絡上節點之間通信的傳播延時情況,如下圖所示,t2、t5為收發器環路延時,t3、t6為隔離延時(磁耦隔離方式,延時時間在3~5ns)、t4、t7為CAN控制器處理延時(通常情況下,延時在納秒級以下,可以忽略不計),t1為線纜傳輸延時。

以節點A發送,節點B接收為例,從CAN報文發出開始,到接收到ACK應答,整個應答回路延時為T總=(t1+t2+t3+t4+t5+t6+t7)*2,期間報文經過了4次隔離及收發器,兩次線纜;

由以上公式可知,整個應答回路延時T總=(t1+t2+t3+t4+t5+t6+t7)*2≤750ns,取T總=750ns,假設t3+t4+t6+t7=25ns,則t1+t2+t5=300ns,即t1=300-(t1+t2),所以可以得知t1+t2的值越小,t1的值就越大,在相同線纜材質的情況下,線纜就越長即傳輸距離更遠;故低環路延時的芯力特芯片SIT1044較上述兩家進口公司同類芯片更有利于長距離傳輸。

此外降低應答回路延時時間,可以選擇性能較好的CAN FD控制器、使用磁耦隔離收發器以及使用標準線纜,禁止使用電話線、網線等線徑較小的線纜,必要時可選擇較好材質的導線。

-

芯片

+關注

關注

456文章

51155瀏覽量

426345 -

收發器

+關注

關注

10文章

3454瀏覽量

106178

發布評論請先 登錄

相關推薦

國內首家:納芯微CAN收發器NCA1044-Q1全面通過IBEE/FTZ-Zwickau EMC認證

茂睿芯全系列車規CAN收發器均已實現量產出貨

納芯微CAN收發器NCA1044-Q1獲得IBEE/FTZ-Zwickau EMC認證

芯力特發布帶振鈴抑制功能的CAN收發器——SIT1463Q

TCAN1051具有CAN FD和故障保護功能的CAN收發器數據表

TCAN33x具備CAN FD(靈活數據速率)的3.3V CAN收發器數據表

具有待機模式和故障保護功能的TCAN1044A-Q1和TCAN1044AV-Q1汽車類CAN FD收發器數據表

具有1.8V I/O支持和故障保護功能的TCAN1044V-Q1汽車類CAN FD收發器數據表

TCAN1042具有CAN FD和故障保護功能的CAN收發器數據表

芯力特CAN?FD收發器芯片SIT1044低環路延時特性更有利于長距離傳輸

芯力特CAN?FD收發器芯片SIT1044低環路延時特性更有利于長距離傳輸

評論