上拉和下拉電阻是許多數字電路的組成部分。了解什么是上拉電阻或下拉電阻很重要?為什么將其用于數字電路?以及如何選擇這些的價值?本文將回答這三個問題,并讓您更好地了解它。

什么是上拉或下拉電阻:

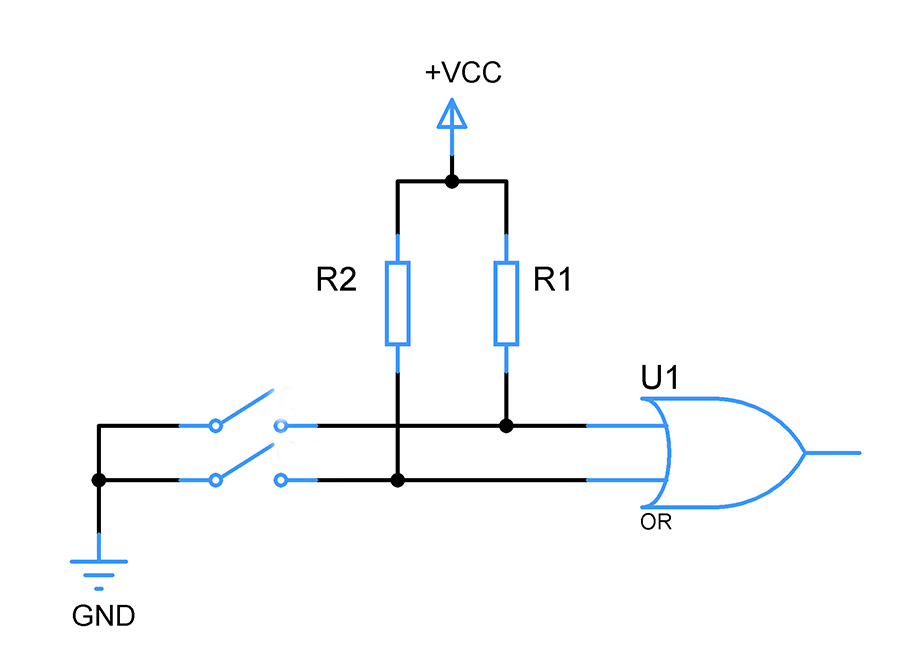

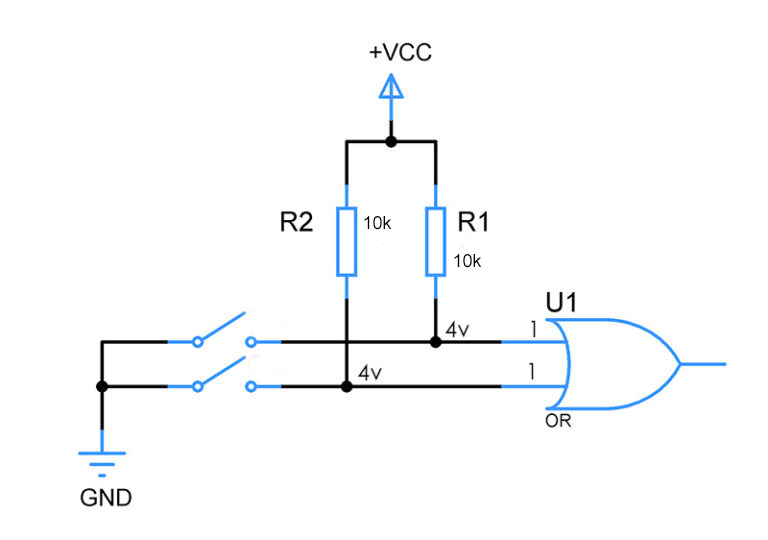

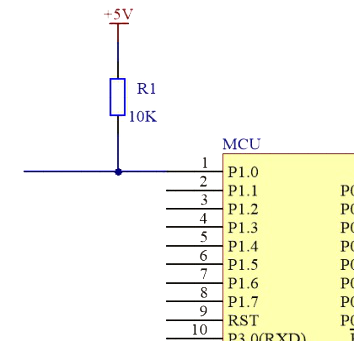

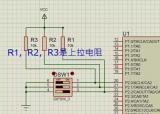

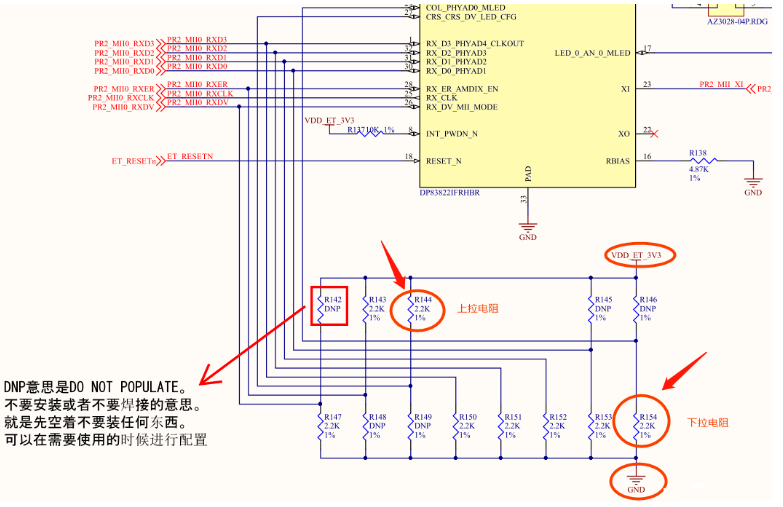

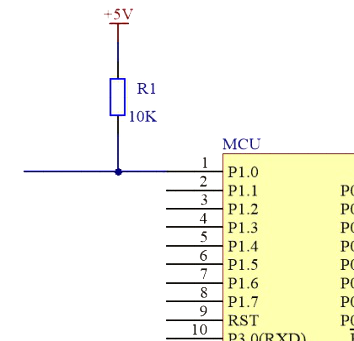

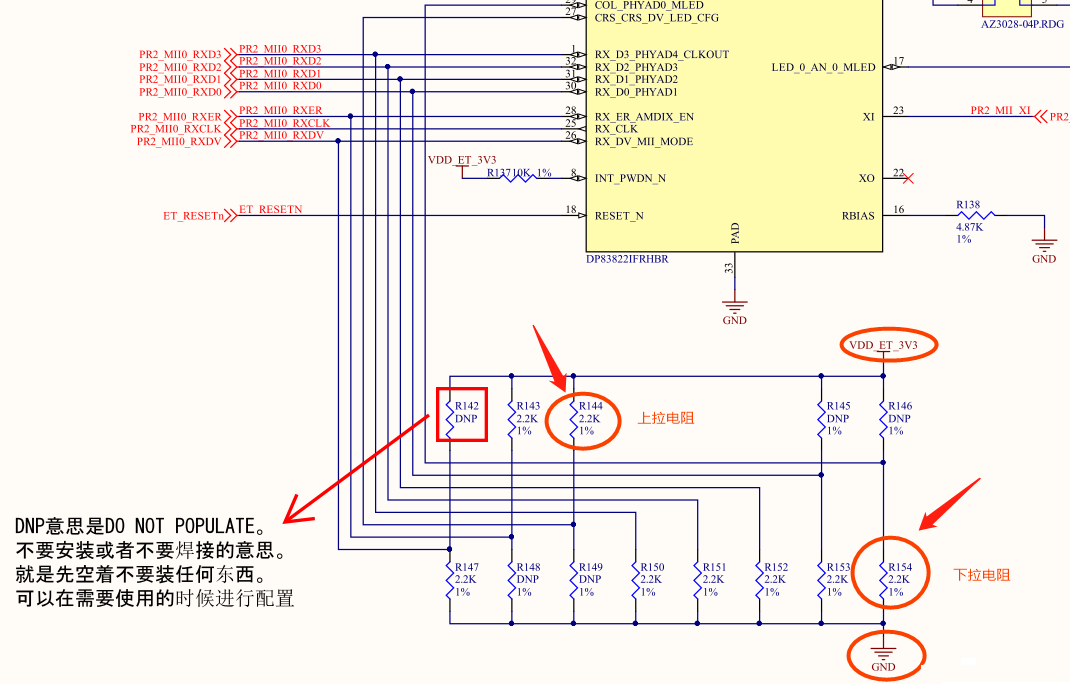

這些是將數字輸入引腳連接到VCC或接地的常用電阻器。這些電阻的目的是調出相當于地或VCC電壓的輸入引腳。參考上面的電路圖,電阻R1和R2是上拉電阻。這些電阻將輸入引腳的電壓拉高到VCC電平。

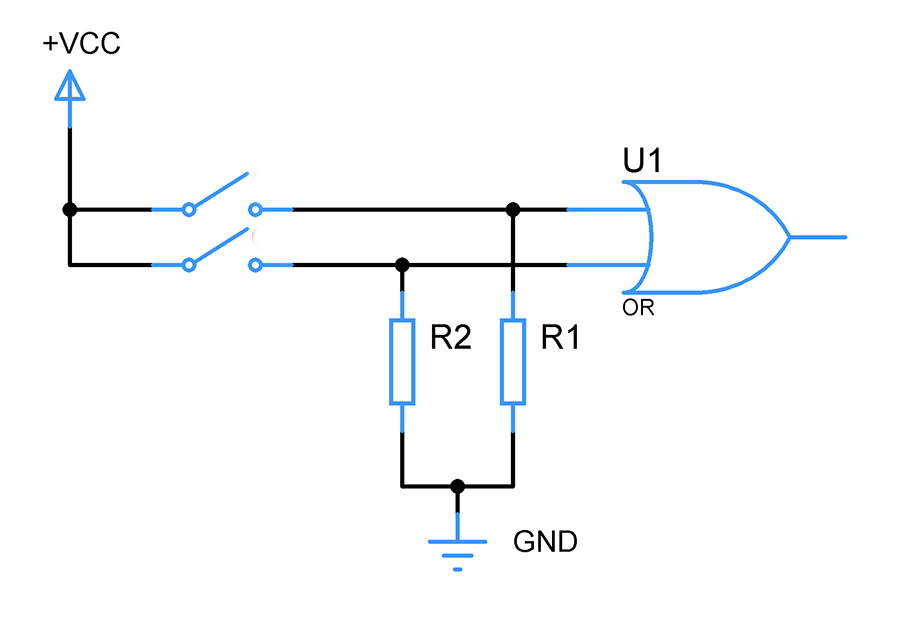

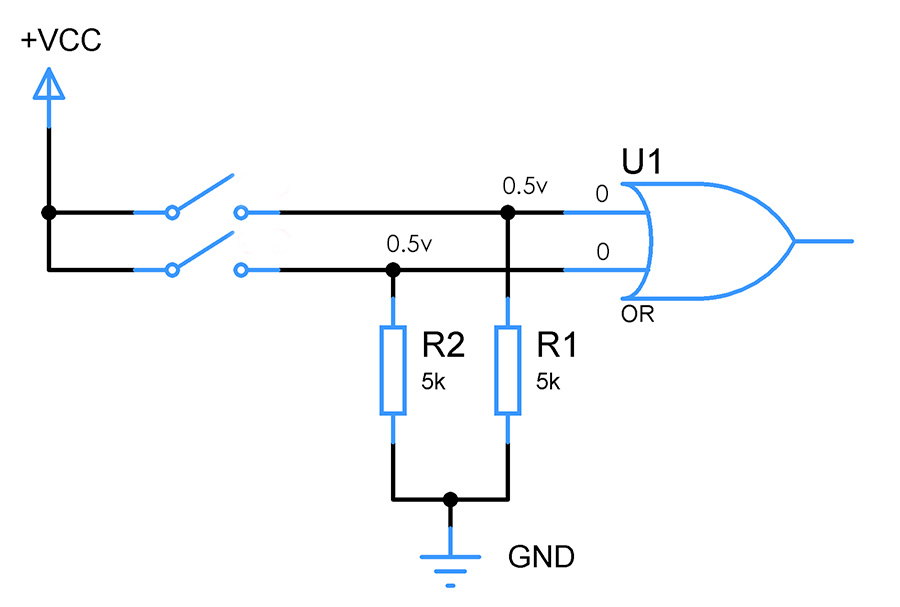

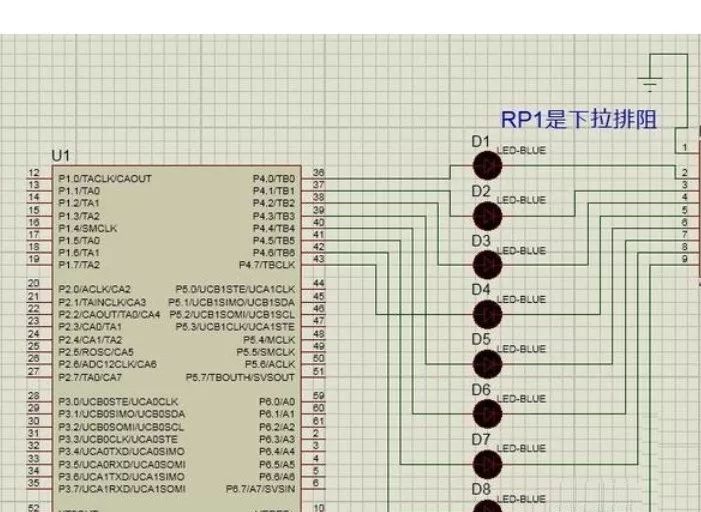

現在看上面的電路圖,這里的電阻R1和R2充當下拉電阻。這些電阻將輸入引腳的電壓下拉至接近GND電平。

為什么使用上拉或下拉電阻:

簡而言之,上拉或下拉電阻的目的是使數字引腳的輸入保持在穩定狀態 - 上拉電阻為1,下拉電阻為0。為了進一步解釋這一點,我們需要了解 Logic

家族以及每個家族之間的區別。

邏輯電平:

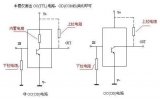

邏輯電平只不過是決定數字電路中的輸入或輸出如何解釋為“1”(高狀態)或“0”(低狀態)的電壓范圍。數字系統中存在許多邏輯家族。TTl,CMOS,RTL,DTL是少數幾個系列,其中TTL和CMOS非常有名且常用。

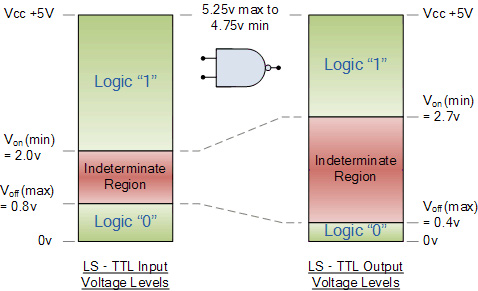

上圖顯示了+5VccTTL邏輯系列的邏輯電平圖。正如您在輸出圖和輸入圖中觀察到的那樣,每種邏輯狀態都有一個電壓范圍。參考輸入電壓電平,您可以觀察到

柵極讀取邏輯 1 – 輸入電壓范圍必須在 2v 至 5v 之間

柵極讀取邏輯 0 – 輸入電壓范圍必須在 0 至 0.8v 之間

不確定區域是陷阱,這意味著當輸入電壓從0.8到2v之間時,柵極將無法理解它,并且它將以不希望的方式起作用。輸出可以是 0 或

1,我們無法預測它們。

最后一種情況對于設計數字電路來說太糟糕了,因為它可能會使整個電路失效,而您的設計將毫無用處。

浮動狀態:

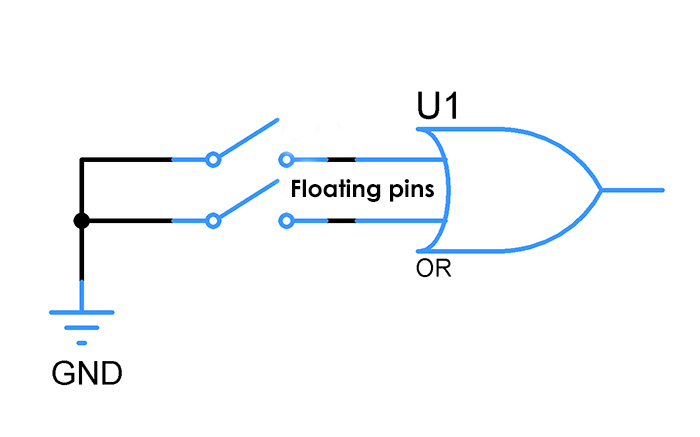

現在看一下上面的電路,其中開關連接到OR門的輸入引腳。當開關未連接時,引腳被稱為浮動狀態,這意味著其中沒有顯示定義的電壓。在這個瞬間,來自周圍的電噪聲或電磁波會在這些引腳中感應出一些電壓,因此輸入電壓很有可能落入0.8至2v的不確定區域,從而推動我們的整個系統失效。在最壞的情況下,噪聲和電磁波會產生波動的電壓,使整個系統不穩定。

為了擺脫上述情況,請在兩個輸入引腳上添加一個電阻,并將它們連接到Vcc。通過這樣做,輸入引腳電壓將被上拉,電壓將幾乎等于Vcc。這使得邏輯門檢測輸入電壓作為邏輯1并采取相應的行動。

計算電阻值:

每個數字輸入引腳都會消耗一些電流,并具有一些內部阻抗。由于這些原因,這些上拉電阻兩端存在壓降。因此,在選擇電阻值時,我們應該確保

電阻不要太高,因此輸入引腳不會有足夠的電流工作

太小,以至于多余的電流流過并導致短路。

上拉電阻:

假設OR門的數字引腳在+100Vcc時消耗5uA電流。為了選擇電阻器,我選擇了4v作為上拉電壓,因為它會從2v提供一些不錯的空間,超出該空間是不確定的區域。您不能選擇5v,因為如上所述,電阻器兩端會有一些壓降,因此選擇低于Vcc電平是安全的。

應用歐姆定律和這些值,

R = 5 – 4 / 100uA

= 1 / 100uA

= 10科姆

下拉電阻:

對于上述100uA的消耗電流,我將選擇0.5v的下拉電壓,因為它從0.8v提供了一個空間,高于該空間的輸入進入不確定區域。在這里應用歐姆定律將得到電阻值

R = 0.5V / 100uA

= 5科姆

注意:

查看數據手冊,了解數字芯片的輸入電流和輸入阻抗,并執行上述計算,為您的數字電路找到完美的上拉或下拉電阻。

切勿嘗試在沒有電阻的情況下嘗試上述設置,您最終會短路電源,因為沒有電阻器關閉開關會導致電流過大,因為沒有阻抗可用。

-

上拉電阻

+關注

關注

5文章

363瀏覽量

30686 -

下拉電阻

+關注

關注

4文章

147瀏覽量

20570 -

數字電路

+關注

關注

193文章

1622瀏覽量

80750

發布評論請先 登錄

相關推薦

什么是上拉或下拉電阻?為什么使用上拉或下拉電阻?

什么是上拉或下拉電阻?為什么使用上拉或下拉電阻?

評論