PSRAM完全解讀

一. PSRAM概述

PSRAM即偽靜態(tài)RAM,要講到PSRAM首先得從SRAM和DRAM講起。

SRAM和DRAM都代表易失性的存儲形式,當(dāng)電源掉電時內(nèi)容丟失。SRAM使用六晶體管存儲單元存儲數(shù)據(jù),速度更快,效率更高(比dram需要更少的功率),允許數(shù)據(jù)殘留,并且通常更昂貴,接口簡單, 驅(qū)動簡單。

相比之下,DRAM通過結(jié)合金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)和金屬氧化物半導(dǎo)體(MOS)電容器來實現(xiàn)數(shù)據(jù)存儲,DRAM芯片更便宜,但需要從外部源不斷刷新以保留其電容器上的數(shù)據(jù),接口復(fù)雜,驅(qū)動復(fù)雜。

那么有沒有一種RAM能結(jié)合SRAM和DRAM的優(yōu)點,即容量大,又接口驅(qū)動簡單呢,有,因為有以上需求于是PSRAM應(yīng)運而生,PSRAM接口和SRAM一樣簡單,驅(qū)動簡單;而存儲形式則和DRAM一樣,容量遠(yuǎn)大于SRAM,介于SRAM和DRAM之間,現(xiàn)在一般是最大64MB。

美光科技聯(lián)合華邦電子 (Winbond Electronics)、GigaDevice Semiconductor 和 AP Memory Technology 創(chuàng)立了Xccela 聯(lián)盟, 其中 Xccela Bus 接口即PSRAM使用的接口。

二. PSRAM廠家

PSRAM廠家也有很多,以AP用的最多。

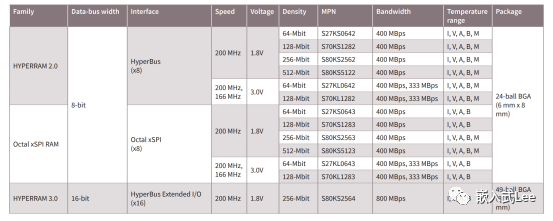

華邦

64Mb

W956D6KBK 1.8V/1.8V 133MHz -40℃~85℃ 4Mb x16 CRAM-ADM - P

256Mb

W968D6DAG 1.8V/1.8V 133MHz -40℃~85℃ 16Mb x16 CRAM - P

W968D6DAG 1.8V/1.8V 133MHz -40℃~85℃ 16Mb x16 CRAM - P

有多種接口,容量可選最大64MB

Apmemory

PSRAM的老大哥,最大到64MB

三.PSRAM詳解

以APS256XXN-OBRx DDR Octal SPI PSRAM 為例進(jìn)行詳解。

2.1特征

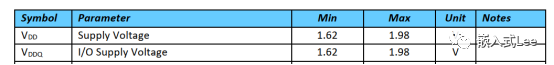

電源

單電源供電,VDD和VDDQ內(nèi)部連接,電源范圍1.62到 1.98V。

接口

Octal SPI接口支持DDR,即雙邊沿傳輸。

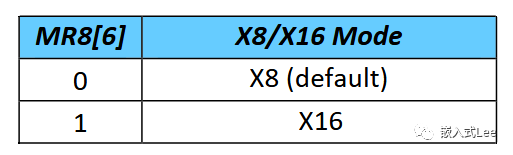

支持x8模式(默認(rèn))和x16模式,可以通過配置寄存器選擇

X8模式,一個CLK傳輸2個字節(jié)數(shù)據(jù),x16模式一個CLK傳輸4個字節(jié)數(shù)據(jù),因為是雙邊沿傳輸。

默認(rèn)x8模式,可以通過寄存器MR8[6]=1改為x16模式。

性能

時鐘最大200MHz,所以最大速度是x8模式400MB/s,x16模式800MB/s。

組織

256Mb X8 模式

一個PAGE大小2048字節(jié) 總?cè)萘?2M x 8bits即32MB

行地址AX[13:0],列地址AY[10:0]

256Mb X16 模式

一個PAGE大小2048字節(jié) 總?cè)萘?6M x 16bits即32MB

行地址AX[13:0],列地址AY[9:0] 一個列地址對應(yīng)16bits即2字節(jié),所以地址范圍是[9:0].

不管什么模式頁總是2KB,x16模式頁地址只需要CA[9:0]因為單位是2B了。

刷新

自刷新,無需發(fā)送命令。

操作溫度范圍

TOPER = -40°C to +85°C 標(biāo)準(zhǔn)范圍

TOPER = -40°C to +105°C 擴展范圍

典型待機電流

Halfsleep模式,數(shù)據(jù)保持,@ 25°C時40μA

最大待機電流

1100μA @ 105°C

680μA @ 85°C

可以看到溫度對待機電流影響較大。

低功耗特征

分區(qū)自刷新PASR,

自動溫度補償自刷新(ATCSR),內(nèi)部自帶溫度傳感器,根據(jù)溫度控制刷新率,溫度越高刷新率越高

軟件復(fù)位

支持軟件命令方式實現(xiàn)上電復(fù)位效果

引腳復(fù)位

不是所有封裝都有

輸出驅(qū)動能力

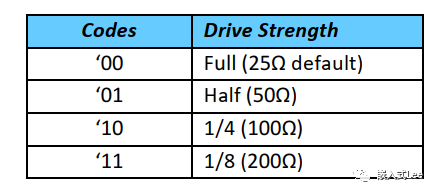

LVCMOS輸出,驅(qū)動能力可以通過寄存器配置

DM/DQS

寫操作支持DM

讀操作支持DQS,DM,DQS共用引腳。

讀寫延遲

可通過寄存器配置讀寫延遲時間

寫B(tài)urst長度

最大X8模式2048 x8bits ,X16模式1024x16bits

最小X8模式2x8bits ,X16模式2x16bits

即最大一個PAGE的大小,最小時一個總線寬度的呃倍,因為是DDR雙邊沿傳輸。

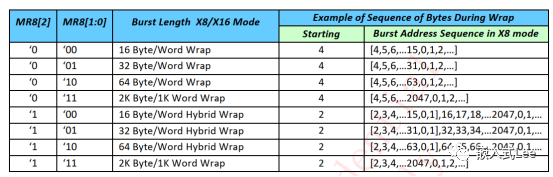

Wrap & hybrid burst

X8模式16/32/64/128/2K 單位Bytes

X16模式16/32/64/128/1K 單位Words(2B)

線性Burst命令

該命令即Burst固定為最大2KB

列地址自動遞增

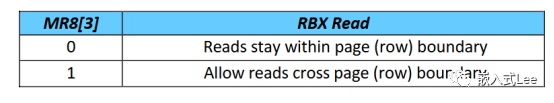

可以通過寄存器配置使能RBX

即讀操作時到了頁邊界,頁地址自動遞增,而不需要重新發(fā)送頁地址。

2.2 引腳信號

重點需要理解DQS/DM0和DQS/DM1這兩個引腳信號。

DQS和DM復(fù)用

DM由主機驅(qū)動,表示寫時數(shù)據(jù)是否MASK掉的,為1表示MASK掉即不需要寫

DQS由設(shè)備驅(qū)動,表示數(shù)據(jù)是否有效的,DQS=1表示數(shù)據(jù)有效。

可以這樣理解,DQS和DM都是誰發(fā)數(shù)據(jù)由誰驅(qū)動,告訴接收方對應(yīng)的字節(jié)數(shù)據(jù)是否有效。

DQS是和DQ數(shù)據(jù)同時更新的。

| 引腳 | 類型 | 描述 | 說明 |

|---|---|---|---|

| VDD | 電源 | Core 和IO 電源1.8V | VDDQ 內(nèi)部連接到VDD |

| VSS | 地 | Core和IO 電源地 | |

| A/DQ[7:0] | IO | 地址/數(shù)據(jù)總線[7:0]注意發(fā)送地址始終是用的[7:0],不會用高16位。 | X8 和X16模式使用 |

| DQ[15:8] | IO | 數(shù)據(jù)總線[15:8] | 只X16 模式使用 |

| DQS/DM<0> | IO | 讀數(shù)據(jù)時DQ[7:0]的DQS信號,設(shè)備端驅(qū)動,為1表示數(shù)據(jù)有效。寫數(shù)據(jù)時DQ[7:0]的DM信號,主機端驅(qū)動,高有效,DM=1表示MASK掉DQ[7:0]即不寫。 | X8 和X16模式使用DQS和DM共用一個引腳 |

| DQS/DM<1> | IO | 讀數(shù)據(jù)時DQ[15:8]的DQS信號,設(shè)備端驅(qū)動,為1表示數(shù)據(jù)有效。寫數(shù)據(jù)時DQ[15:8]的DM信號,主機端驅(qū)動,高有效,DM=1表示MASK掉DQ[15:8]即不寫。 | 只X16 模式使用DQS和DM共用一個引腳 |

| CE# | I | 芯片選擇,低有效. CE#=1,芯片進(jìn)入standby 狀態(tài). CE拉低是一次傳輸?shù)拈_始。 | |

| CLK | I | 輸入時鐘 | |

| RESET# | Input | 復(fù)位信號,低有效. 可選的內(nèi)部連接固定電平。 | 不是所有封裝都有 |

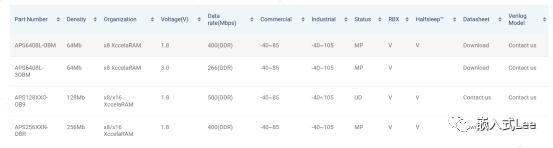

2.3 框圖

可以看到VDD會進(jìn)入到內(nèi)部的電源調(diào)節(jié)器,可以進(jìn)行電源狀態(tài)控制,比如PDP和Halfsleep的管理。

PSRAM控制邏輯和IO控制部分會產(chǎn)生行地址,進(jìn)行列地址計數(shù),分別進(jìn)行行列地址解碼,輸入到存儲陣列,選擇對一個存儲單元,通過Data I/O進(jìn)行數(shù)據(jù)的寫入和讀出。

命令地址,模式寄存器,輸入到控制邏輯序列,決定上面PSRAM控制邏輯和IO控制部分的邏輯。命令和地址,寄存器的讀寫不經(jīng)過Data I/O。

重點是時鐘的控制,CLK_int進(jìn)入時鐘緩沖和產(chǎn)生模塊,輸出CLK_IO給Data I/O用,輸出CLK_ctrl給控制邏輯用。

外部接口通過輸入輸出緩存和內(nèi)部交互,分別到Data I/O或者到控制邏輯部分,或者到CLK_int

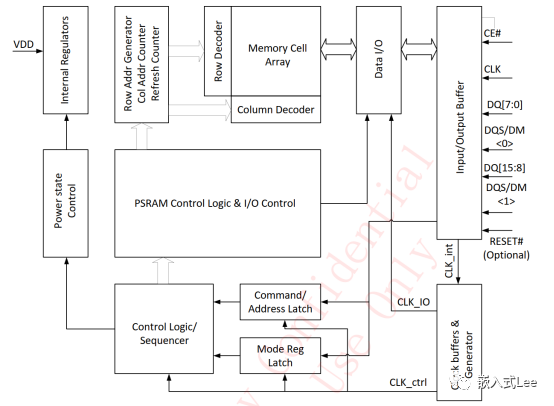

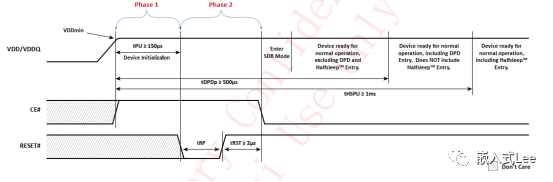

2.4 上電復(fù)位初始化時序

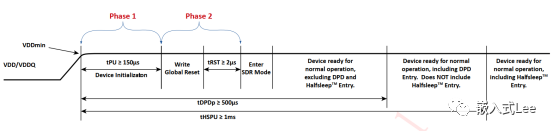

上電復(fù)位有兩種方式,一種是通過RESET#引腳復(fù)位(有些封裝該引腳未引出),直接電源的上電也是這種方式;還有一種是發(fā)送Global Reset命令。兩種方式復(fù)位的效果一致。

上電復(fù)位的效果是所有寄存器恢復(fù)到默認(rèn)狀態(tài),RAM中的內(nèi)容不保證狀態(tài)。

有幾個時間點需要注意

1.復(fù)位完成后即可進(jìn)入SDR模式,既可以進(jìn)行單速率讀。

然后即可進(jìn)行正常的所有操作(如果是VDD剛上電則需要滿足后面相應(yīng)的條件才能進(jìn)行PDP和Halfsleep操作)。

2.VDD達(dá)到VDDmin至少要≥500uS才能進(jìn)行所有正常操作,除了Halfsleep之外。

3.VDD達(dá)到VDDmin至少要≥1mS才能進(jìn)行所有正常操作。

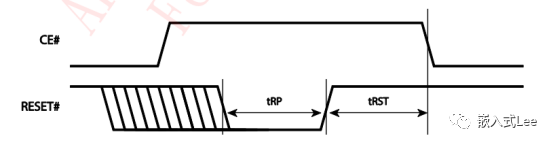

2.4.1 RESET#引腳復(fù)位

VDD/VDDQ必須達(dá)到VDDmin穩(wěn)定之后,才進(jìn)入初始化流程。

VDD穩(wěn)定后進(jìn)入初始化的階段1,該階段必須保持CE#為高,且VDD保持穩(wěn)定,該階段至少要保持tPU≥150uS。

階段1之后的任意時候,在CE#為高時,都可以進(jìn)行RESET#的拉低來進(jìn)行復(fù)位,拉低時間需要tRP≥1uS

然后釋放RESET#,釋放時間要≥2uS。所有RESET#引腳復(fù)位至少需要3uS,復(fù)位過程對應(yīng)階段2。

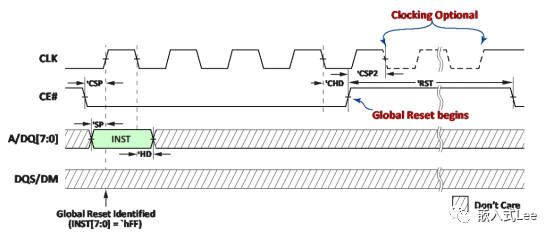

2.4.2 Global Reset命令復(fù)位方式

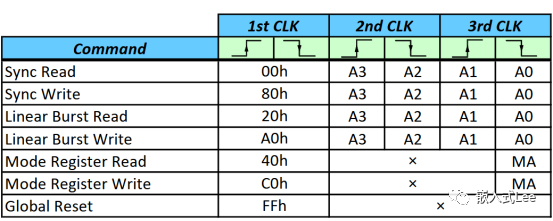

在階段1之后,任意時間,可以發(fā)送0xFF指令進(jìn)行上電復(fù)位,即上圖的階段2部分。

CE#拉低tCSP之后CLK的第一個邊沿和第二個邊沿發(fā)送INST,即A/DQ[7:0]=0xFF,此時DQS/DM

不關(guān)心。注意A/DQ[7:0]的建立時間至少要tSP,即CLK上升沿tSP之前數(shù)據(jù)就要準(zhǔn)備好,數(shù)據(jù)保持時間需要tHD以上,即CLK下降沿之后數(shù)據(jù)至少還要保持該時間。發(fā)完INST之后,CLK再發(fā)送3個CLK,最后一個CLk的下降沿tCHP之后CE#開始拉高釋放,此時開始真正的復(fù)位。

CE#釋放拉高之后的tCSP2時間后,CLK不再關(guān)心可有可無。tRST時間后復(fù)位完成。

即必需tRST時間之后,CE#才能再次拉低,進(jìn)行后續(xù)操作。

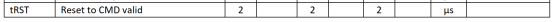

相關(guān)時序參數(shù)值如下:

2.5 接口描述

2.5.1 地址空間

讀寫數(shù)據(jù),地址必須是偶數(shù)對齊,即地址的A[0]必須為0, 所以x8模式是2B對齊,x16模式是4B對齊。讀寫寄存器無該要求,可以指定任意對應(yīng)可讀寫的寄存器。

2.5.2 Burst類型和長度

讀寫默認(rèn)是Hybrid Wrap 32 模式,可通過寄存器配置為x8模式的16B,32B,64B,2KB,x16模式的16words,32words,64words,1Kwords。

Bursts長度寫最少要是x8模式2B,x16模式4B,讀無最小限制。

讀寫的最大Burst長度不受限制,但是一次傳輸不能超過tCEM的時間。

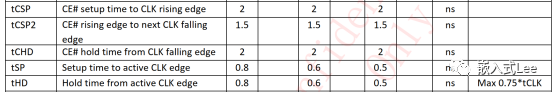

2.5.3 命令地址發(fā)送

CE#拉低之后,指令在第一個CLK的上升沿和下降沿被設(shè)備鎖存。從第二個CLK開始的2個CLK共4個邊沿發(fā)送4個字節(jié)的地址,都是邊沿設(shè)備鎖存數(shù)據(jù)。

所以3個CLK共6個邊沿發(fā)送命令+地址。命令實際只有一個字節(jié),在上下沿保持不變發(fā)送的是同樣的內(nèi)容,地址4個字節(jié)。

2.5.4 命令表

指令和地址總是只使用A/DQ[7:0]不管是x8還是x16模式。

x16模式 列地址不需要CA10,CA[9:0]足夠,因為單位是2字節(jié)了。

Linear Burst 命令0x20,0xA0,Burst固定,不受MR8[2:0]的配置影響

只有Linear Burst讀支持RBX,即自動頁地址遞增。

如下圖

其中x表示關(guān)心可以任意值

A3 = 7'bx, RA[13] {未使用位保留}

A2 = RA[12:5]

A1 = RA[4:0],CA[10:8] { CA[10] 只在 X8 模式有}

A0 = CA[7:0] 注意CA[0]始終是0

MA = 模式寄存器地址

其中Sync Read和Sync WriteBurst的Burst由MR[8:0]配置

Linear Burst Read和Linear Burst Write固定為Linear Burst即頁大小,不受MR[8:0]影響,該模式支持RBX(需要寄存器配置使能)。

Mode Register Read和Mode Register Write支持從任意寄存器開始讀寫(和寄存器的讀寫屬性要對應(yīng))。

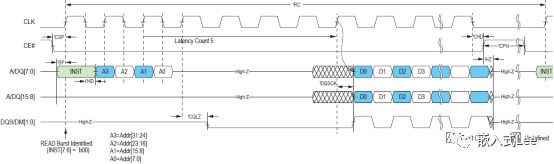

2.5.5 讀操作

CE#拉低后的開始3個CLK發(fā)送完命令和地址, 設(shè)備從第三個CLK的上升沿即發(fā)送A1時開始拉低DQS/DM。

延遲LC時間后,A/DQ[7:0]輸出數(shù)據(jù),由于內(nèi)部刷新機制,延遲時間可能是LC~LCx2之間。

第一個DQS/DM的上升沿表示設(shè)備輸出的數(shù)據(jù)有效。

不管是x8模式還是x16模式,命令和地址都只使用A/DQ[7:0],如果是x16模式則返回數(shù)據(jù)時A/DQ[7:0]輸出和A/DQ[7:0]完全一樣。

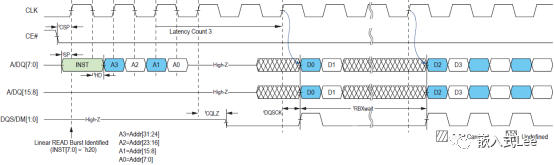

同步讀模式

( Synchronous Read )

1.CE#拉低表示一次傳輸開始,tCSP之后CLK開始拉高發(fā)送命令I(lǐng)NST

2.在CLK的上升沿之前tSP數(shù)據(jù)就要準(zhǔn)備好,即數(shù)據(jù)的建立時間

3.CLK下降沿之后tHD之后,數(shù)據(jù)還需要保持,即數(shù)據(jù)的保持時間

4.第4個CLK上升沿之后tCQLZ開始拉低,表示PSRAM收到指令了正在準(zhǔn)備數(shù)據(jù),此時主機還不能去讀數(shù)據(jù),數(shù)據(jù)還未就緒。

5.A1對應(yīng)的上升沿之后的LC時間(默認(rèn)是5個CLK),之后設(shè)備才會輸出數(shù)據(jù),這里是讀延遲時間。

6.LC之后的第一個上升沿之后的tDQCLK時間后,DQS/DM才會拉高,表示PSRAM輸出數(shù)據(jù)有效 DQS/DM是和DQ數(shù)據(jù)同步更新的。

7.主機在LC延遲之后,等待DQS的上升沿,捕獲到DQS的上升沿后需要延時一段時間才能采樣,因為DQS的上升沿DQ也才同步更新,需要一個建立時間之后才能采樣數(shù)據(jù),后面會講這個參數(shù)。

8.CLK的下降沿tCHD之后,CE#才能拉高。

9.CE#拉高之后tHZ時間后,數(shù)據(jù)線變?yōu)楦咦钁B(tài)。

10.CE#拉高必須至少tCPH時間.

11.一次傳輸至少需要tRC時間

12.一次傳輸CE#拉低的時間最長tCEM

線性Burst讀使能RBX

( Linear Burst Read with RBX (Starting address 0xFE in X8 mode and 0x3FE in X16 mode)

和Synchronous Read一樣,如果使能RBX,即(MR8[3]為1則在列地址跨頁邊界時,會由tRBXWait的時間延遲,然后頁地址自動遞增繼續(xù)讀。

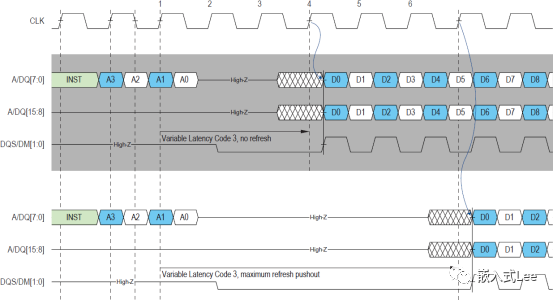

自刷新導(dǎo)致的讀延遲增加

( **Variable Read Latency Refresh Pushout ** )

上圖上面部分沒有自刷新,延遲時間是3個CLK,下面部分有自刷新,所以延遲時間最大可達(dá)2x3=6CLK。

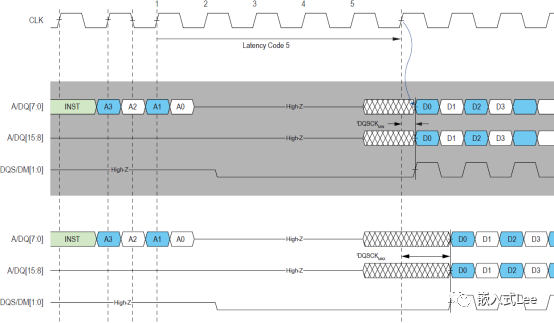

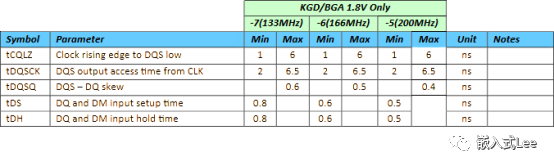

讀延遲和tDQSCK

( **Read Latency & tDQSCK ** )

以上可以看到tDQSCKmin和tDQSCKMmax差異可能導(dǎo)致,DQS/DM第一個數(shù)據(jù)出來的時間差半個CLK,即CLK下降沿鎖存數(shù)據(jù)變?yōu)樯仙劓i存數(shù)據(jù)。

tDQSCK最小2nS,最大6.5nS。

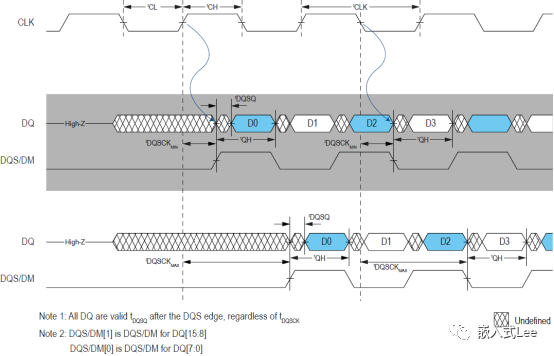

**讀時DQS/DM 和 DQ **時序

( Read DQS/DM & DQ timing )

1.DQS和DQ是同步更新的。

2.DQS上升沿之后的tDQSQ時間之后,數(shù)據(jù)才有效,因為需要數(shù)據(jù)建立時間。所以讀數(shù)據(jù)需要在DQS上升沿之后至少等待tDQSQ才能采樣。

3.讀數(shù)據(jù)是以DQS邊沿為準(zhǔn)而不是以CLK邊沿為準(zhǔn)了。

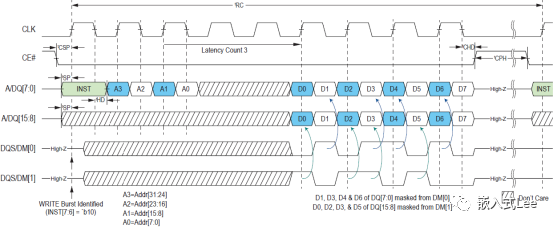

2.5.6 寫操作

同步寫操作

( Synchronous Write followed by any Operation )

1.tCSP,tSP,tHD,tCHD,tCPH,tRC等含義和讀一樣.

2.寫操作x8模式最少需要寫2字節(jié),x16模式至少需要寫4字節(jié)。

3.單字節(jié)的寫可以通過DQS/DM的MASK來實現(xiàn),DM=1表示對應(yīng)字節(jié)不寫。

4.指令地址總是只使用DQ[7:0], x16模式數(shù)據(jù)階段才會使用DQ[15:8].

5.數(shù)據(jù)階段DQ[15:8]和DQ[7:0]分別用DM[1]和DM[0]確認(rèn)是否MASK掉,為1則MASK掉不寫對應(yīng)對應(yīng)的字節(jié)。

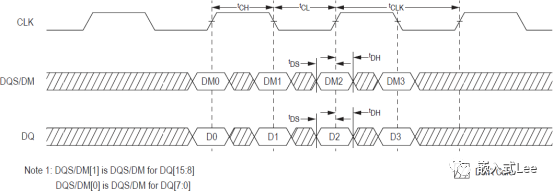

寫時DQS/DM & DQ的時序

( **Write DQS/DM & DQ Timing ** )

1.CLK上升沿和下降沿建立時間tDS之前準(zhǔn)備數(shù)據(jù),數(shù)據(jù)保持時間tDH。即在CLK邊沿前的tDS數(shù)據(jù)就要準(zhǔn)備好,tDS后數(shù)據(jù)才能釋放。

3.DM和DQ同步變化。

2.5.7 控制寄存器

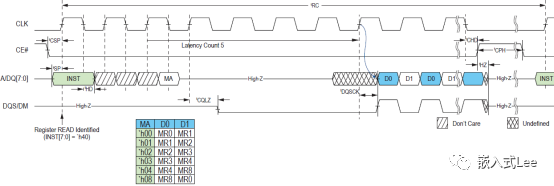

寄存器讀

寄存器讀寫始終只使用A/DQ[7:0]

( Register Read )

1.tCSP,tSP,tHD,tRC,tCQLZ,tDQSCK,tCHD,tHZ,tCPH等參數(shù)和讀數(shù)據(jù)時含義一樣。

2.寄存器6只寫,所以上述表格沒有MA6

3.讀寄存器可指定任意可讀寄存器開始, 連續(xù)讀則D0,D1即開始寄存器和后一個寄存器重復(fù)返回,PSRAM驅(qū)動DQS會指定只有D0有效,所以主機會重復(fù)讀到D0,丟棄D1.

4.寄存器讀的延遲和讀數(shù)據(jù)的延遲一樣,MR0[4:2]決定。

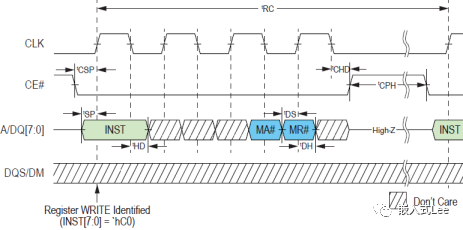

寄存器寫

( **Register Write ** )

注意寄存器寫沒有延遲,即MA之后CLK的下一個邊沿即發(fā)送MR,也不需要DM。

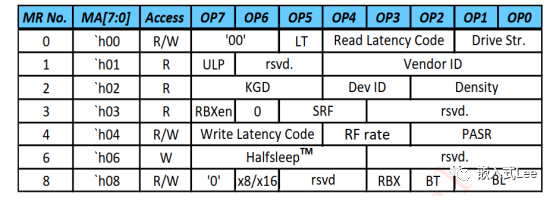

寄存器內(nèi)容

寄存器如下,MA6只寫,MA1,2,3只讀,其他的可讀寫。

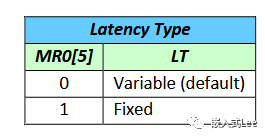

MR0[5] 讀延遲類型

延遲類型1表示固定的,0表示可變的。

這里的可變是因為有刷新所以加上刷新時間可能是LC~2xLC之間任意值,

固定就是干脆就直接固定為最大值2xLC,固定的話有時候可以,方便控制器端程序。

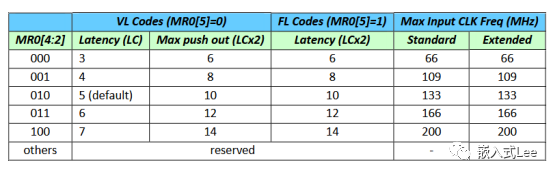

MR0[5:2] 讀延遲時間設(shè)置

延遲時間設(shè)置,不同的頻率需要設(shè)置不同的延遲時間,頻率大延遲時間大。

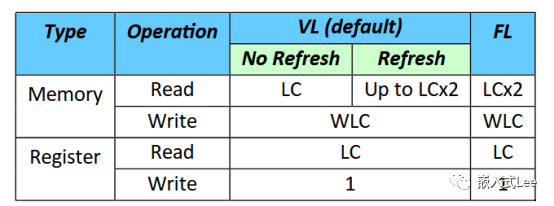

各種操作的延時

寫寄存器無延遲或者說延遲是1

讀寄存器是LC

寫數(shù)據(jù)延時為WLC

讀數(shù)據(jù)根據(jù)FL的設(shè)定可能是LC~2LC之間可變或者固定為2LC。

MR0[1:0] 驅(qū)動能力

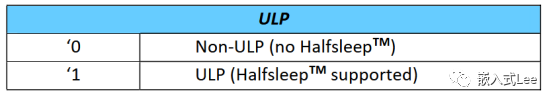

MR1[7] 支持Halfsleep能力

只讀,表示是否支持超低功耗

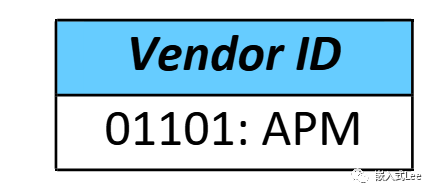

MR1[4:0] 廠商ID

只讀,廠商ID

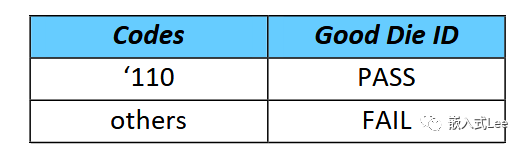

MR2[7:5] 測試狀態(tài)

只讀,表示是否測試OK,默認(rèn)的Die沒有測試時是FAIL狀態(tài),測試OK之后設(shè)置為PASS

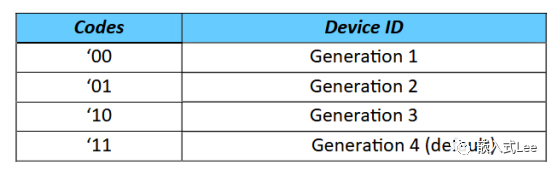

MR2[4:3] 設(shè)備ID

只讀,設(shè)備ID,確認(rèn)是第幾代產(chǎn)品

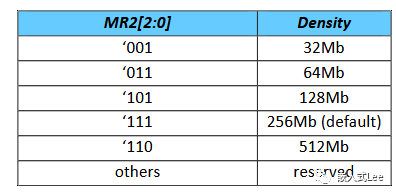

MR2[2:0] 容量

只讀,確認(rèn)容量大小

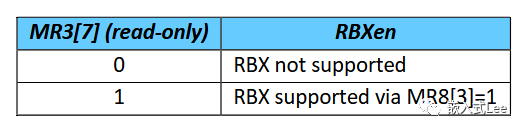

**MR3[7] **RBX模式能力

只讀,確認(rèn)是否支持地址自動跨頁,如果支持則通過MR8[3]使能

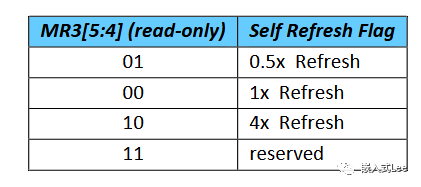

MR3[5:4] 自刷新標(biāo)志

只讀,當(dāng)前刷新率,由MR4[4:3]和溫度決定

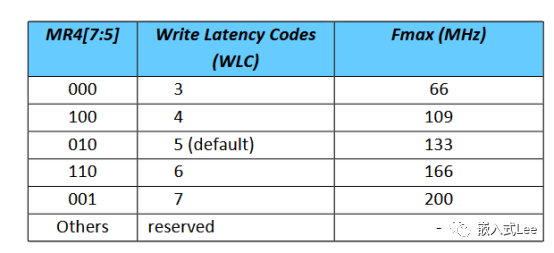

MR4[7:5] 寫延遲設(shè)置

寫延遲時間設(shè)置

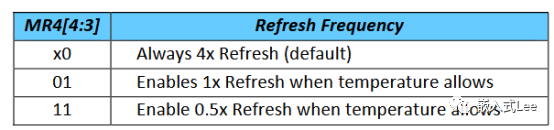

MR4[4:3] 刷新頻率設(shè)置

刷新頻率設(shè)置

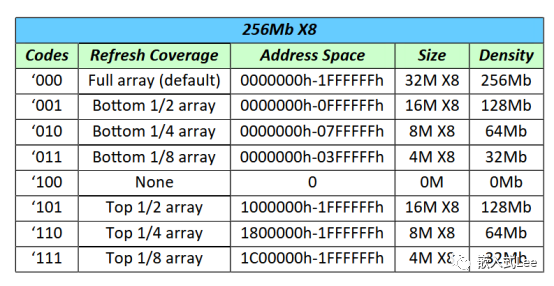

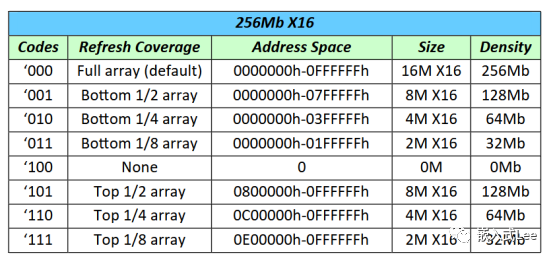

MR4[2:0] 分區(qū)刷新

16位模式只需要10位CA[9:0]既可以表示2K,1024x2B,所以不需要CA10

分區(qū)刷新可以減少待機功耗。

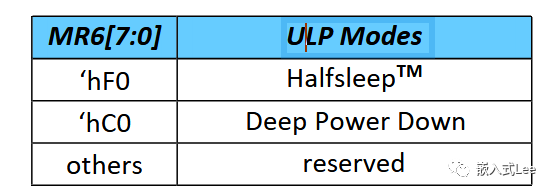

** MR6[7:0]**** Halfsleep設(shè)置**

MR8 [6] ** x8/x16模式選擇**

MR8[2] Burst類型 MR8[1:0] Burst長度

線性Burst命令自動頁大下Wrap,同步讀命令則根據(jù)MR8[1:0]設(shè)定 Wrap

不支持RBX,即不支持自動地址遞增的,一次只能最多讀一頁,超過繞回。

**MR8[3] **RBX讀使能

需要支持RBX的才能配置,MR3[7]可以確認(rèn)是不是支持RBX

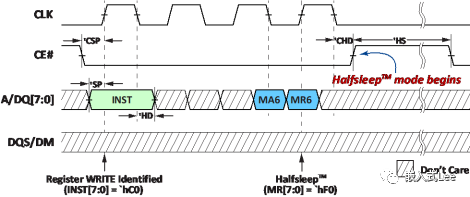

2.5.8 Halfsleep模式

(Halfsleep **Entry Write (latency same as Register Writes, WL1) ** )

Halfsleep模式下數(shù)據(jù)保持,

寫寄存器MR6為0xF0進(jìn)入低功耗,寫完釋放CE后tHS時間后才真正進(jìn)入低功耗

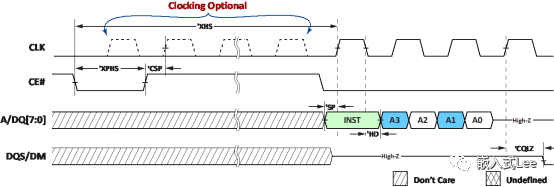

(Halfsleep **Exit (Read Operation shown as example) ** )

CE拉低觸發(fā)退出低功耗,但是必須滿足拉低時間超過tXPHS再釋放,釋放時間超過tCSP,tXHS為CE拉低后退出低功耗需要的時間,此時CLK可有可無。

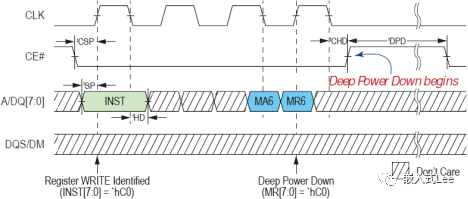

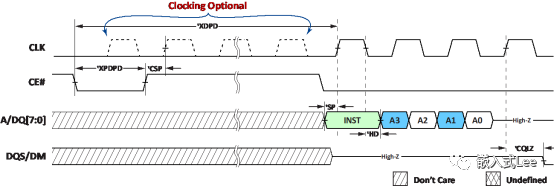

2.5.9 DPD模式 深度休眠模式

深度休眠進(jìn)入和退出和Halfsleep類似,命令不同,還有就是寄存器內(nèi)容和存儲內(nèi)容不保存,需要重新初始化。

( **Deep Power Down Entry ** )

( Deep Power Down Exit (Read Operation shown as example) )

2.6 典型參數(shù)

主要關(guān)注時序參數(shù),其他參數(shù)可以參考手冊

需要注意的是Halfsleep平均電流很小小于100uA,但是峰值電流可達(dá)25mA,持續(xù)幾十毫秒。

所以最好防止4.7uF到10uF的儲能電容到VDD和VSS之間。

直流特性參數(shù)

主要注意高電平要大于0.8VDDQ

低電平要小于0.2VDDQ

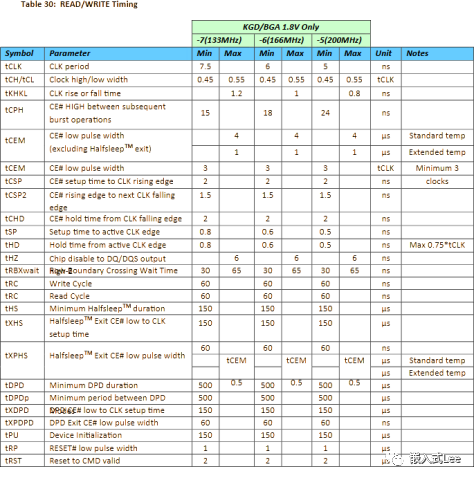

時序參數(shù)

需要注意滿足各個參數(shù)的最小值

四. 總結(jié)

PSRAM有類似SRAM簡單的接口,軟件驅(qū)動簡單,而又有DRAM高容量高性價比,所以在IOT領(lǐng)域應(yīng)用廣泛。很多SOC,MCU,MPU都內(nèi)部封裝了PSRAM,用戶低成本即可使用大的RAM存儲。

PSRAM的時序比較簡單,主要根據(jù)各個時序圖理解每個時序階段,及其參數(shù)。重點要理解DQS/DM是誰驅(qū)動的,代表什么意思, 數(shù)據(jù)采樣的時間即DQS上升沿延遲數(shù)據(jù)建立時間之后采樣。

不同PSRAM芯片時序基本一致,了解一個即可。

-

DRAM

+關(guān)注

關(guān)注

40文章

2311瀏覽量

183445 -

存儲單元

+關(guān)注

關(guān)注

1文章

63瀏覽量

16148 -

sram

+關(guān)注

關(guān)注

6文章

767瀏覽量

114675 -

晶體管

+關(guān)注

關(guān)注

77文章

9682瀏覽量

138080 -

PSRAM

+關(guān)注

關(guān)注

0文章

35瀏覽量

13337

發(fā)布評論請先 登錄

相關(guān)推薦

實例解讀51單片機完全學(xué)習(xí)與應(yīng)用 PPT課件共16章

PSRAM偽靜態(tài)隨機存取內(nèi)存

PSRAM在日常生活中的應(yīng)用

pSRAM與SRAM相比較,它的優(yōu)勢是什么

實例解讀模擬電子技術(shù) 完全學(xué)習(xí)與應(yīng)用pdf

STM32單片機擴展下的IPUS SQPI PSRAM應(yīng)用領(lǐng)域

Gowin PSRAM Memory Interface IP用戶指南

Gowin Video Frame Buffer with PSRAM IP用戶指南

EVAL PSRAM GW1NR4用戶手冊

ESP PSRAM64/ESP PSRAM64H技術(shù)規(guī)格書

PSRAM完全解讀

PSRAM完全解讀

評論