在了解芯片沉積工藝之前,先要闡述下薄膜(thin film)的概念。 薄膜材料是厚度介于單原子到幾毫米間的薄金屬或有機物層 。

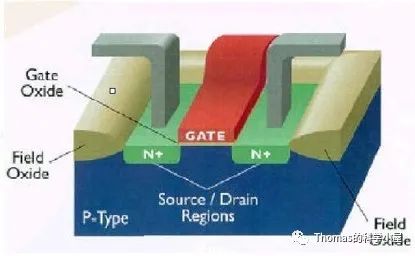

在芯片進行光刻、刻蝕之前,需要沉積一層薄膜。這層薄膜可能是各種化合物外延,多晶硅柵極,金屬層導體等等。 通過對這層薄膜的光刻、刻蝕,才能雕刻出邏輯電路的溝槽,從而裝上各種導體和絕緣體,以來形成邏輯電路的連接 。(下圖是NMOS立體示意圖)

沉積工藝

沉積又叫做淀積,一般通過物理方法在晶圓表面噴上去或者通過化學方法在晶圓上長出來 。沉積工藝非常直觀,將晶圓基底投入沉積設備中,待形成充分的薄膜后,清理殘余的部分就可以進入下一道工序。

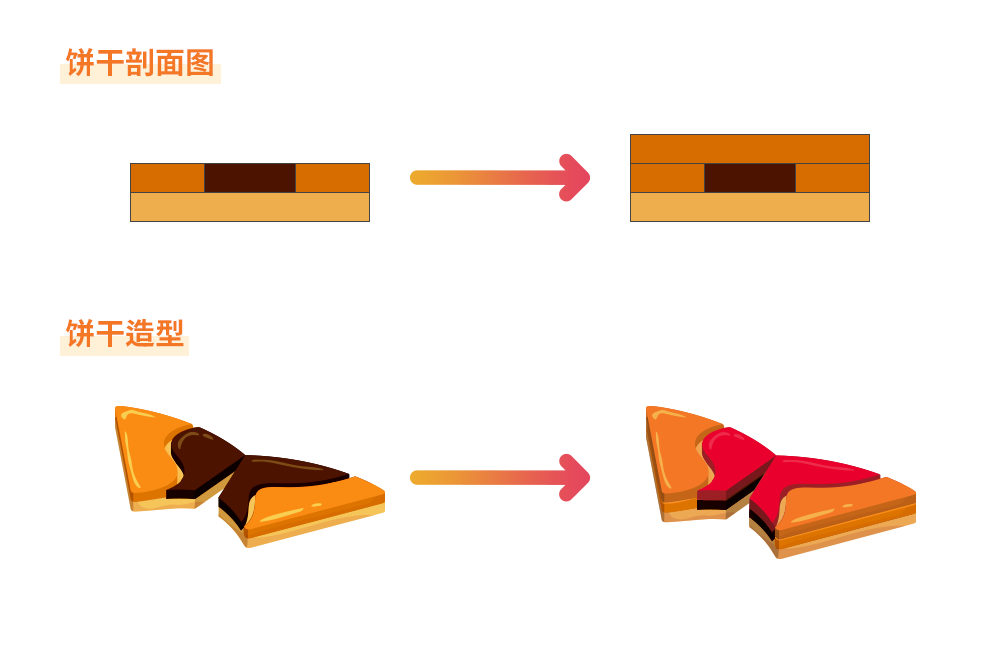

由于市場對電子產品的性能和低電耗的要求越來越高,薄膜沉積也變得越來越復雜。不同于在表面刷一層漆那樣簡單,在硅片或晶圓上沉積一層,往往是納米級別的薄膜,致密性和均勻性也有著極高的要求。

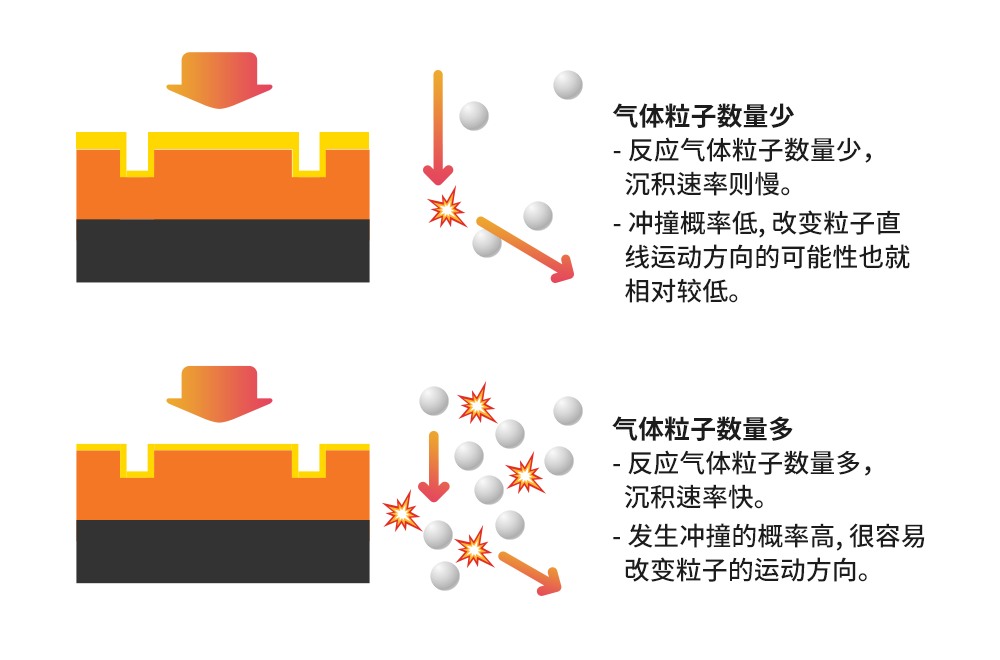

沉積工藝也可分為化學氣相沉積(CVD,Chemical Vapor Deposition)和物理氣相沉積(PVD,Physical Vapor Deposition)。

CVD的優(yōu)點是速率快,由于在晶圓表面發(fā)生化學反應,擁有優(yōu)秀的臺階覆蓋率。但是缺點也很明顯,產生副產物廢棄。PVD的優(yōu)點是無副產物,沉積薄膜的純度高,因此多用于純凈物的金屬布線 。

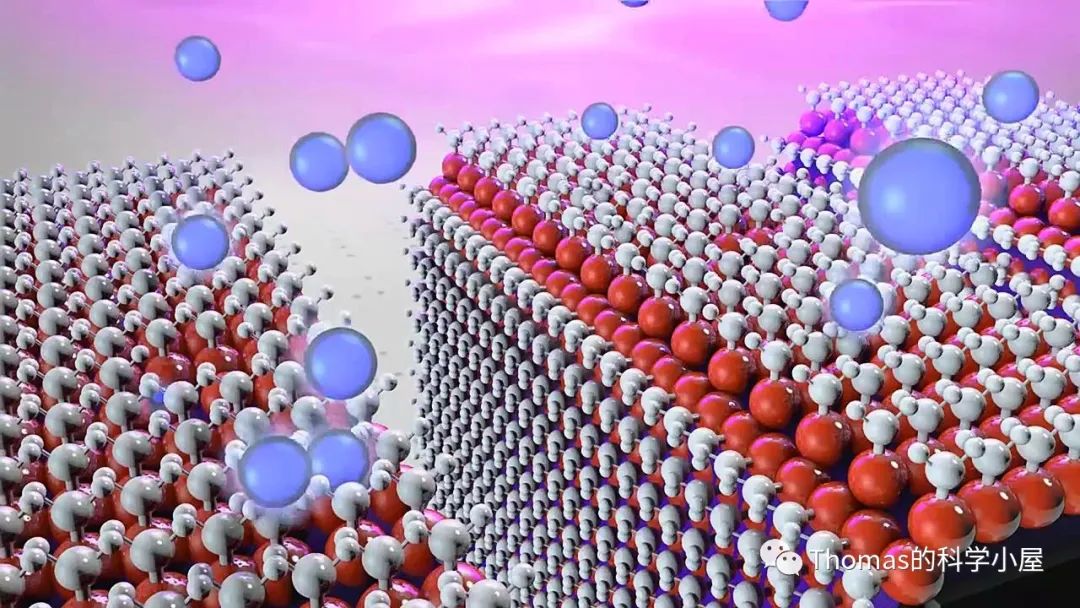

還有一種特殊的沉積方式,即原子層沉積(ALD,Atomic Layer Deposition)。原子層沉積與普通的化學沉積又相似之處,但是又有不同的生長方式。 ALD最大優(yōu)勢在于沉積層極其均勻的厚度和優(yōu)異的臺階覆蓋率 。(下圖為ALD示意圖)

物理氣相沉積

物理氣相沉積是指在真空條件下采用物理方法將材料源(固體或液體)表面氣化成氣態(tài)原子或分子,或部分電離成離子,并通過低壓電氣(或等離子體)過程,在基體表面沉積具有某種特殊功能的薄膜的技術 。(下圖是濺射鍍膜的原理圖)

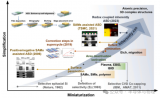

早在20世紀初,PVD技術就有應用。在進入半導體發(fā)展黃金期,工程師們發(fā)現PVD沉積溫度低且可控制在500攝氏度以下,受到了業(yè)界的青睞。

在此前,由于溫度低于大部分工件的回火溫度,對工件的強度和韌性沒有影響,PVD技術被應用于高精度刀具,磨具和摩擦磨損件的最終處理工藝。目前, PVD用于半導體制造領域邏輯和儲存器上制造超薄,超純金屬和過渡金屬氮化物薄膜 。

總結

在早期半導體發(fā)展的歷程中,物理氣相沉積發(fā)揮了巨大的作用。隨著半導體微細化趨勢,尤其是智能手機的崛起,讓化學氣相沉積和原子層沉積,得到了極大的研究和發(fā)展。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42632 -

PVD

+關注

關注

4文章

50瀏覽量

16993 -

儲存器

+關注

關注

1文章

93瀏覽量

17486 -

CVD

+關注

關注

1文章

72瀏覽量

10742 -

NMOS管

+關注

關注

2文章

121瀏覽量

5440

發(fā)布評論請先 登錄

相關推薦

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

MEMS與傳統(tǒng)CMOS刻蝕與沉積工藝的關系

MEMS與傳統(tǒng)CMOS刻蝕及沉積工藝的關系

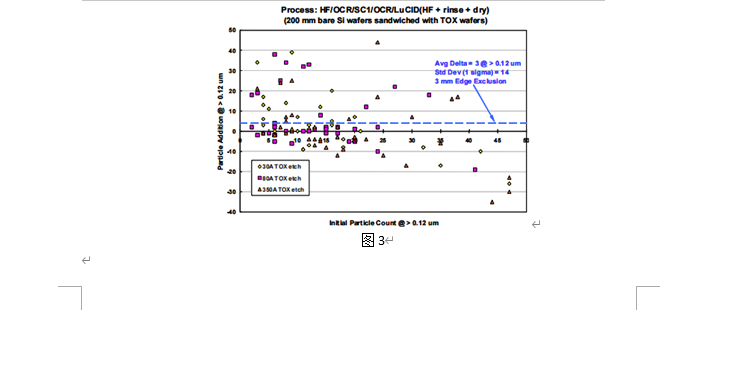

外延沉積前原位工藝清洗的效果

半導體設備行業(yè)跟蹤報告:ALD技術進行薄膜沉積工藝優(yōu)勢

基于PVD 薄膜沉積工藝

半導體前端工藝之沉積工藝

半導體前端工藝:沉積——“更小、更多”,微細化的關鍵

一文詳解半導體薄膜沉積工藝

淺析芯片沉積工藝

淺析芯片沉積工藝

評論